ÉLECTRONIQUE | EMBARQUÉ | RADIO | IOT

# HACKABLE

L'EMBARQUÉ À SA SOURCE

N° 55

JUILLET / AOÛT 2024

FRANCE MÉTRO. : 14,90 €

BELUX : 15,90 € - CH : 23,90 CHF ESP/IT/PORT-CONT : 14,90 €

DOM/5 : 14,90 € - TUN : 35,60 TND - MAR : 165 MAD - CAN : 24,99 CAD

L 19338 - 55 - F: 14,90 € - RD

CPPA : 192470

## HACK / OSCILLOSCOPE

Vous n'avez que deux mains pour faire vos mesures ? Ajoutez une **pédale USB** à votre oscilloscope ! p.18

## SÉCURITÉ / PROTOCOLE

Créez un environnement pour tester la sécurité des systèmes industriels basés sur **Modbus** p.34

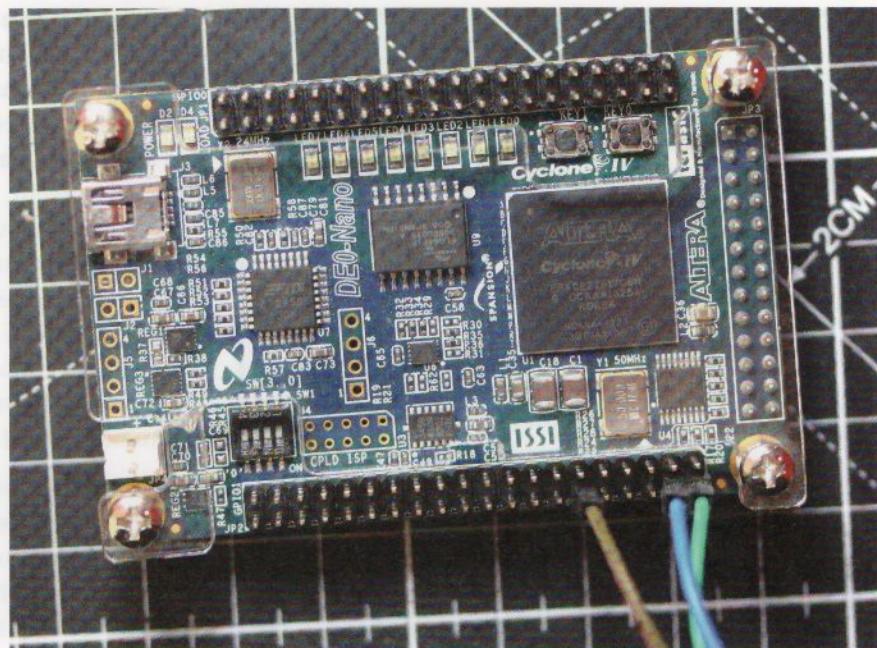

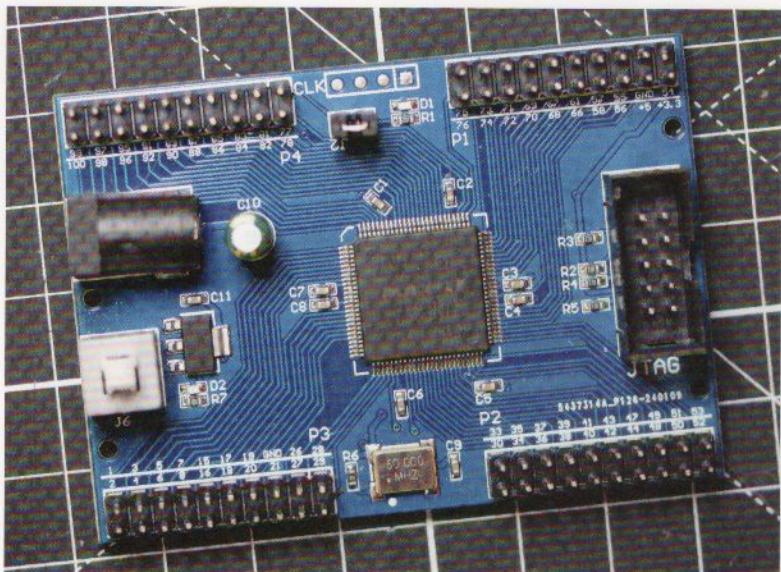

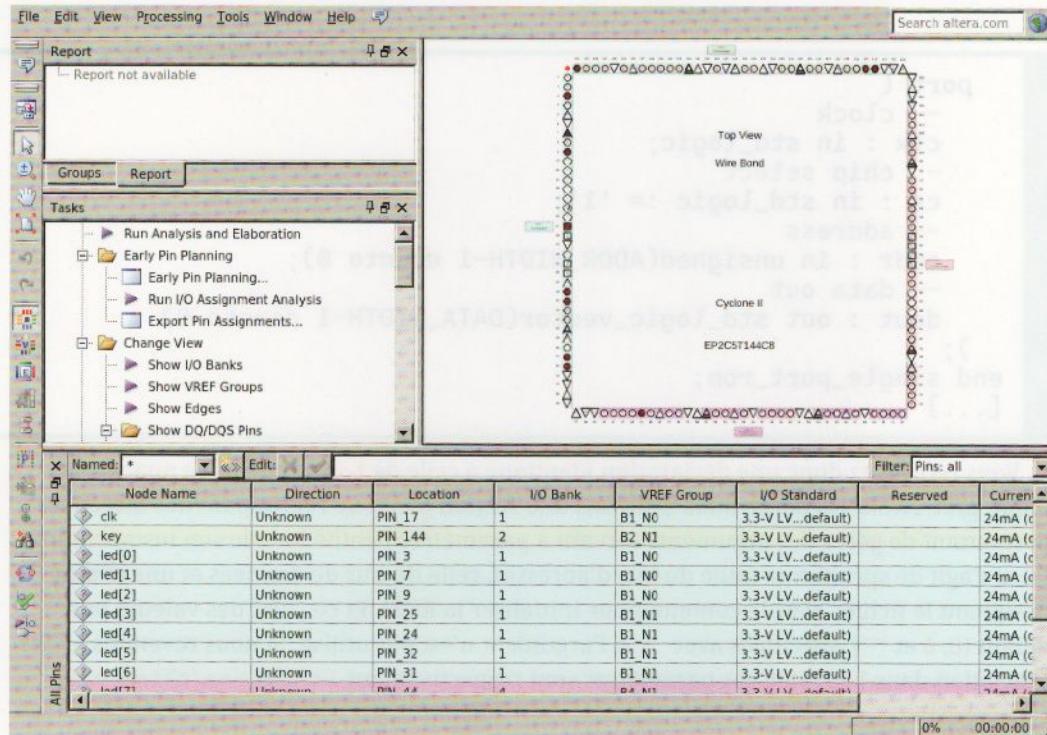

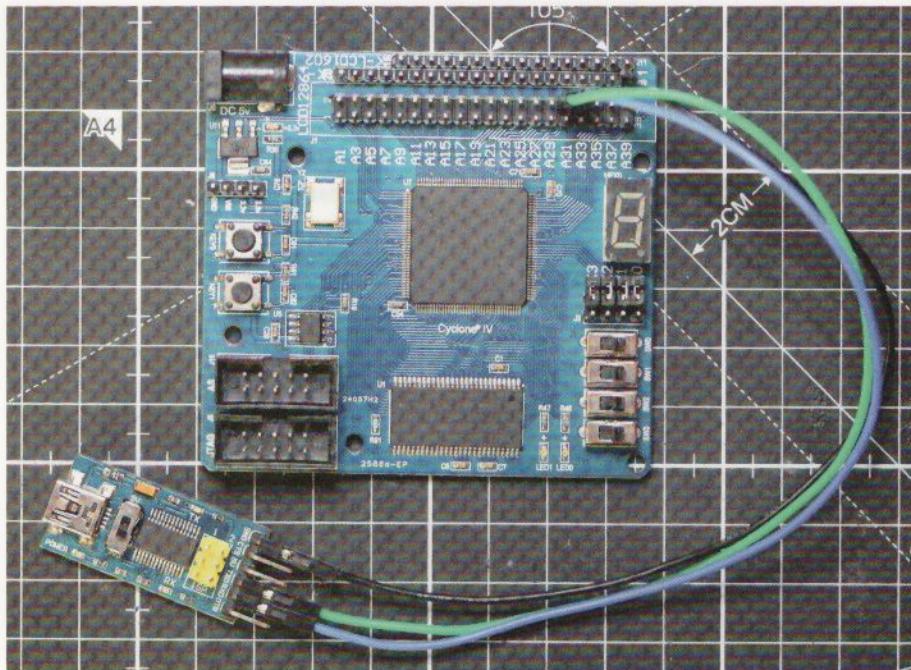

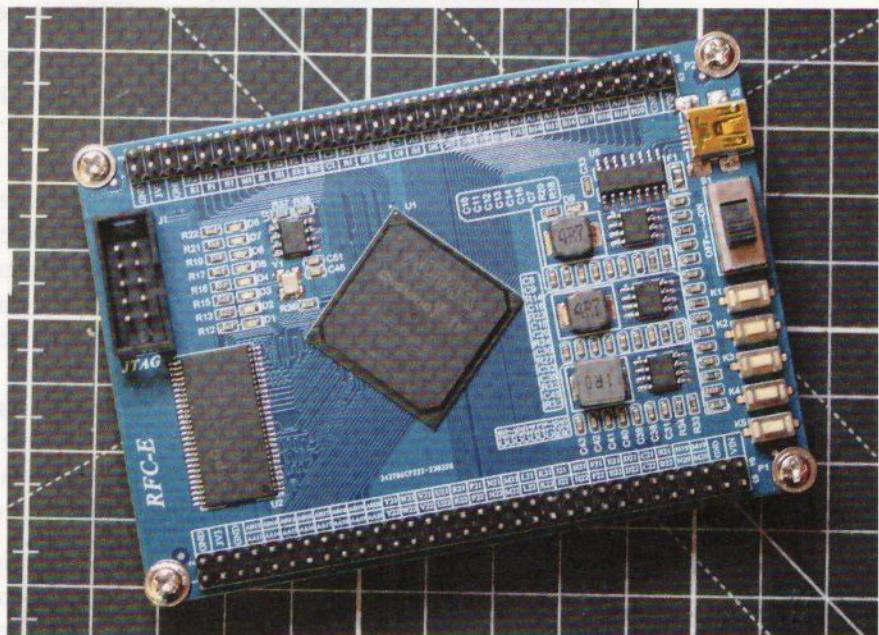

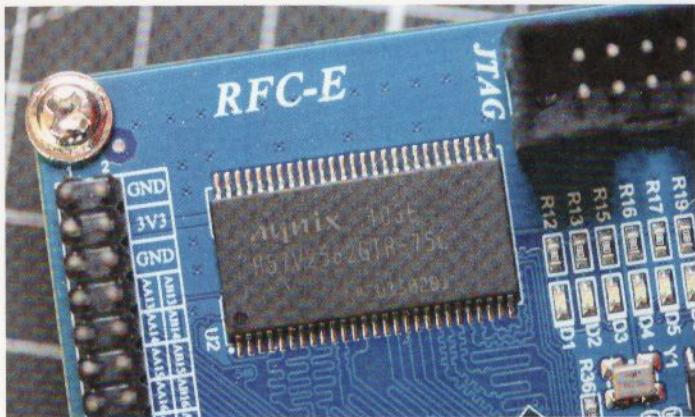

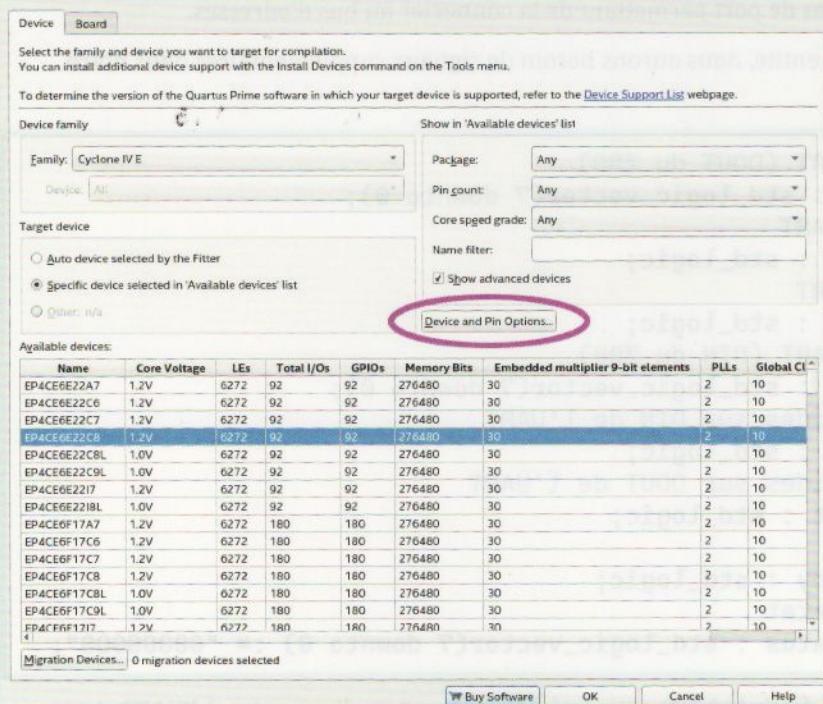

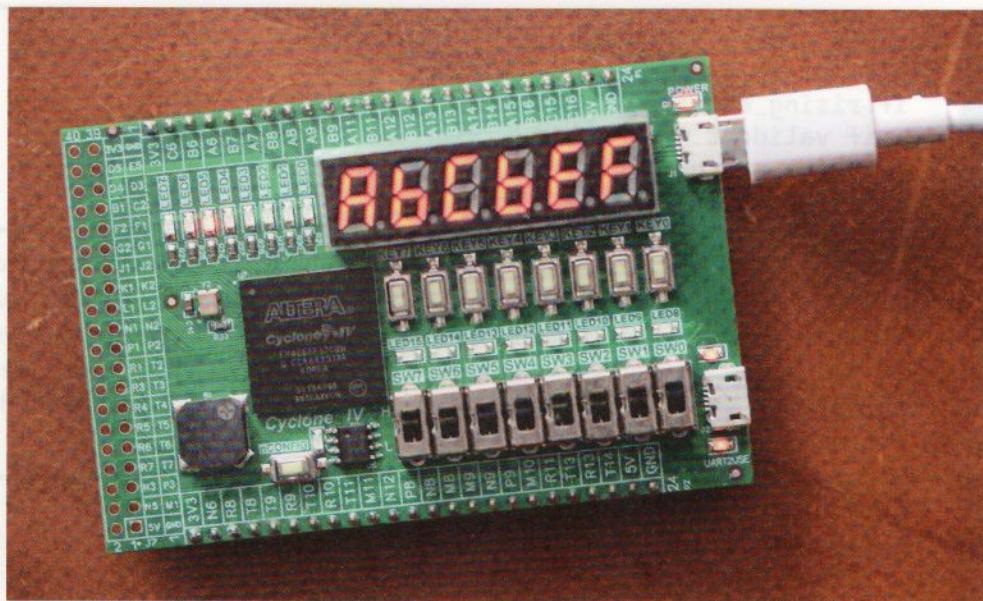

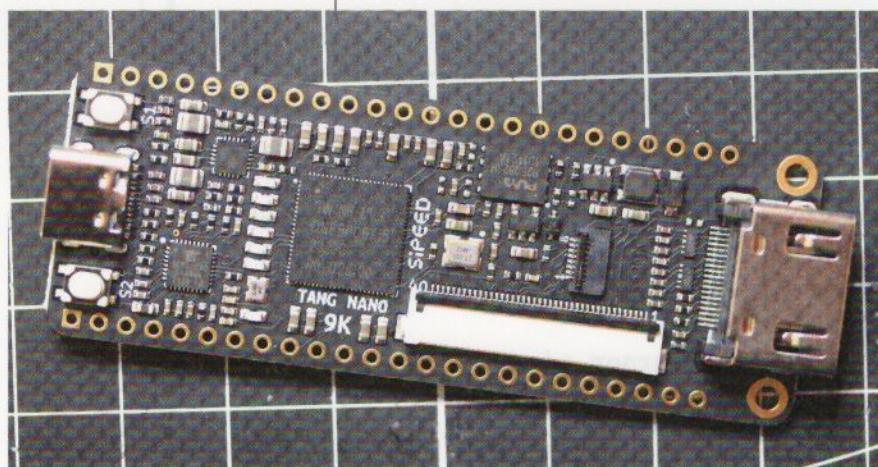

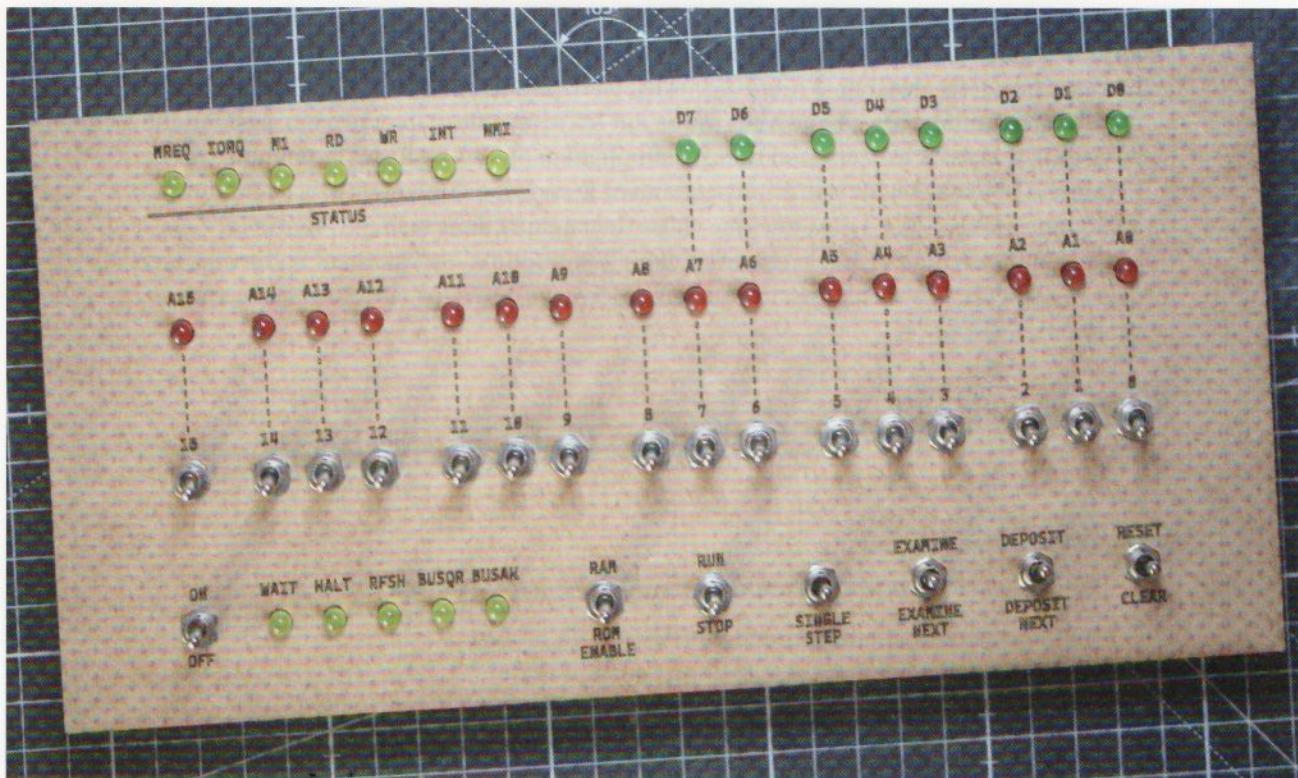

## Circuits programmables / VHDL / Z80

Toujours du mal à aller au-delà de la simple LED qui clignote ?

# MON PREMIER (VRAI) PROJET FPGA !

p.54

- Choisir sa plateforme

- Réunir CPU, RAM, ROM et UART

- Créer son ordinateur 8 bits

## RÉTRO / MODEM

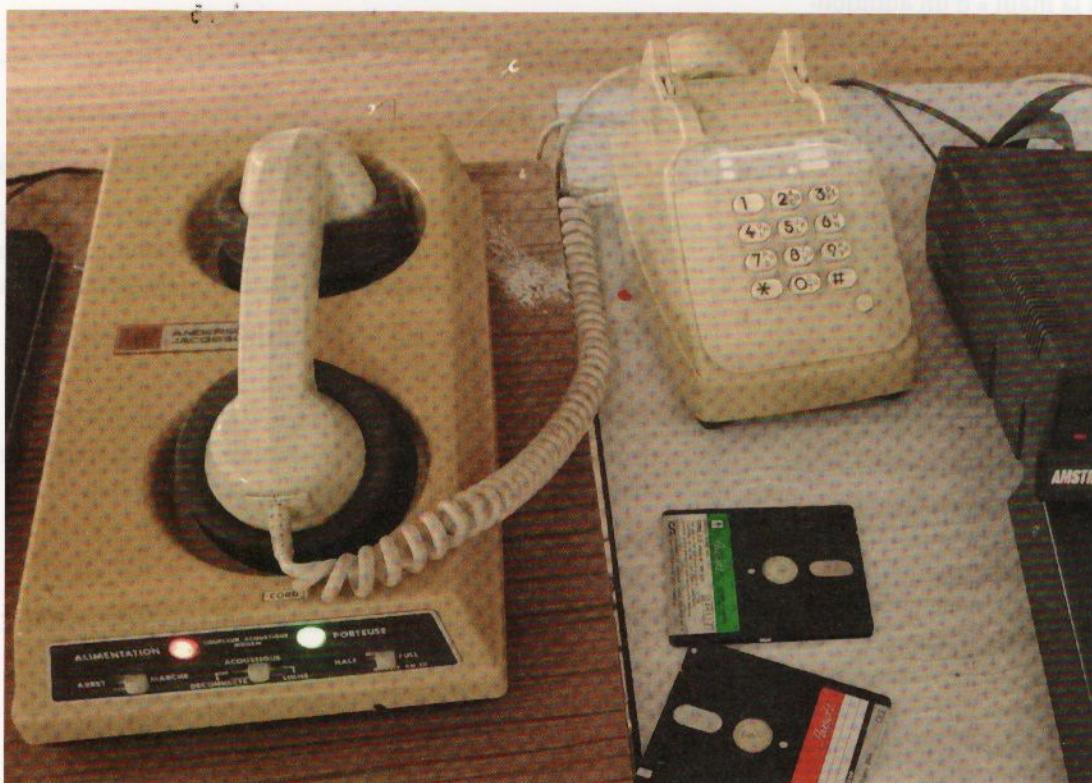

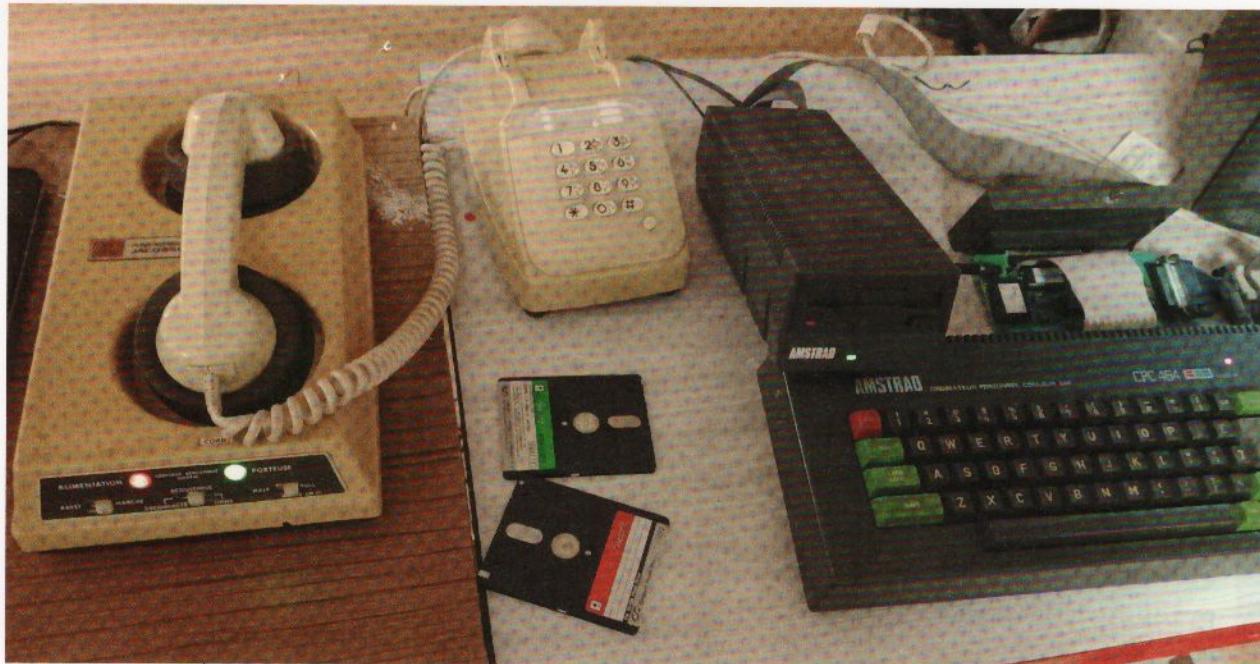

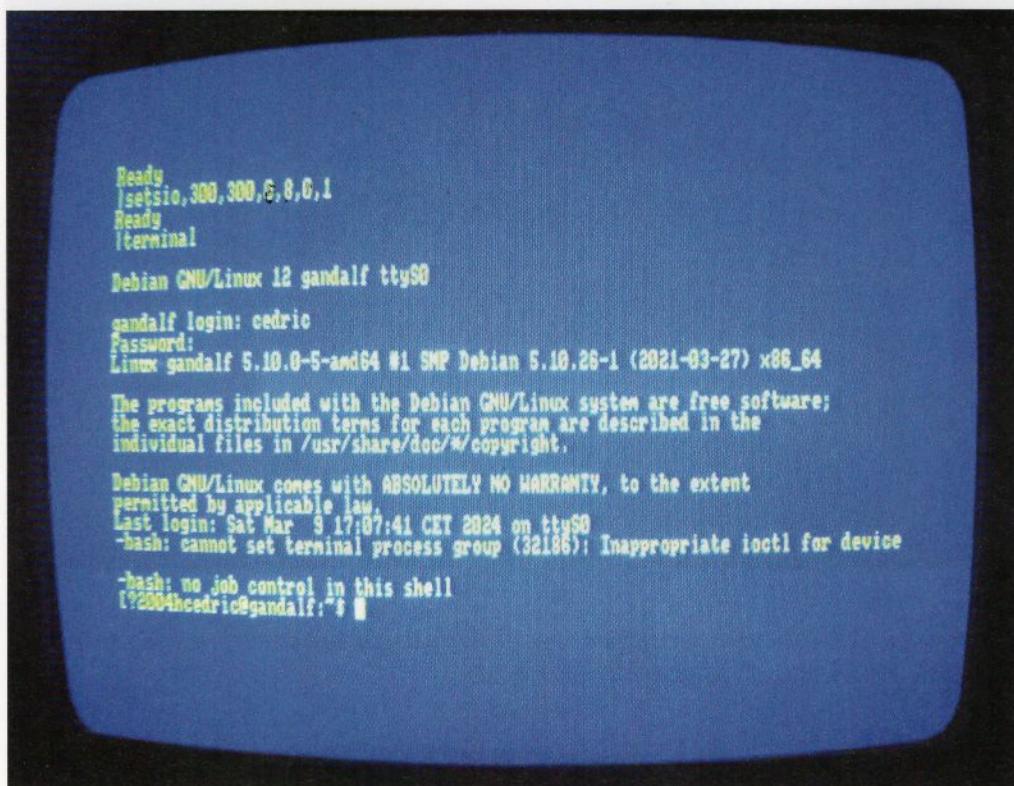

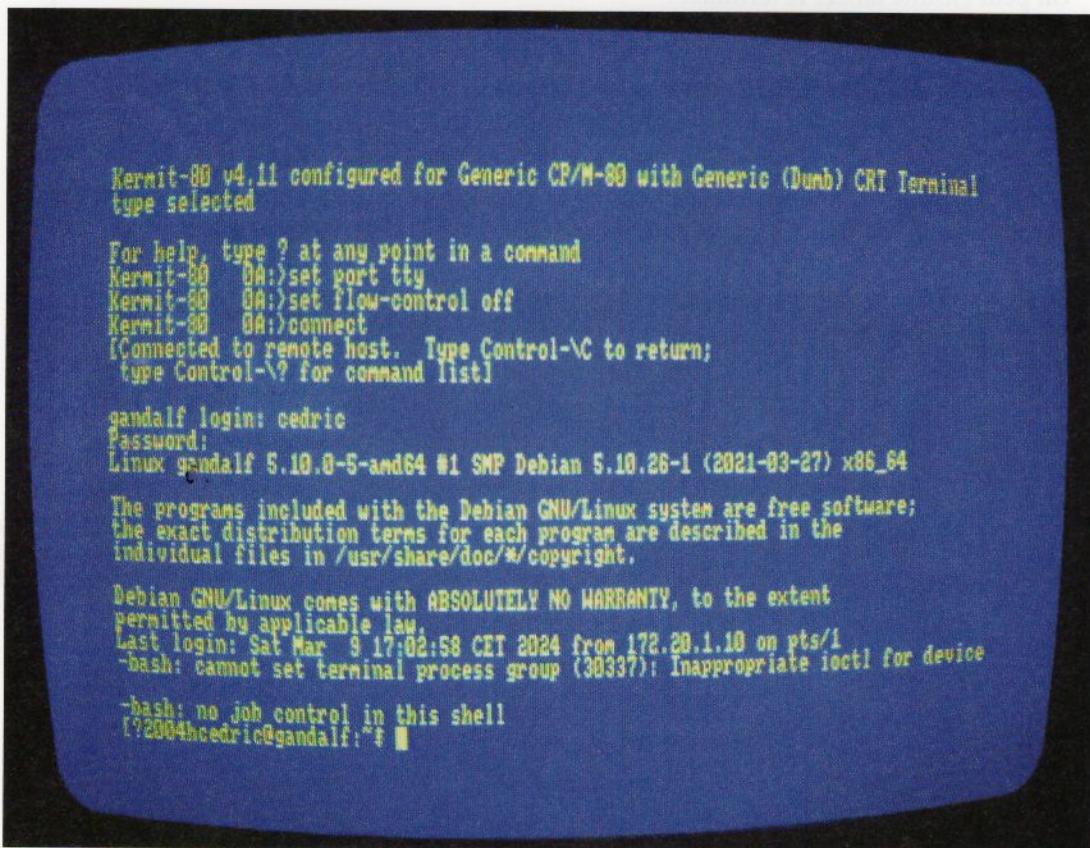

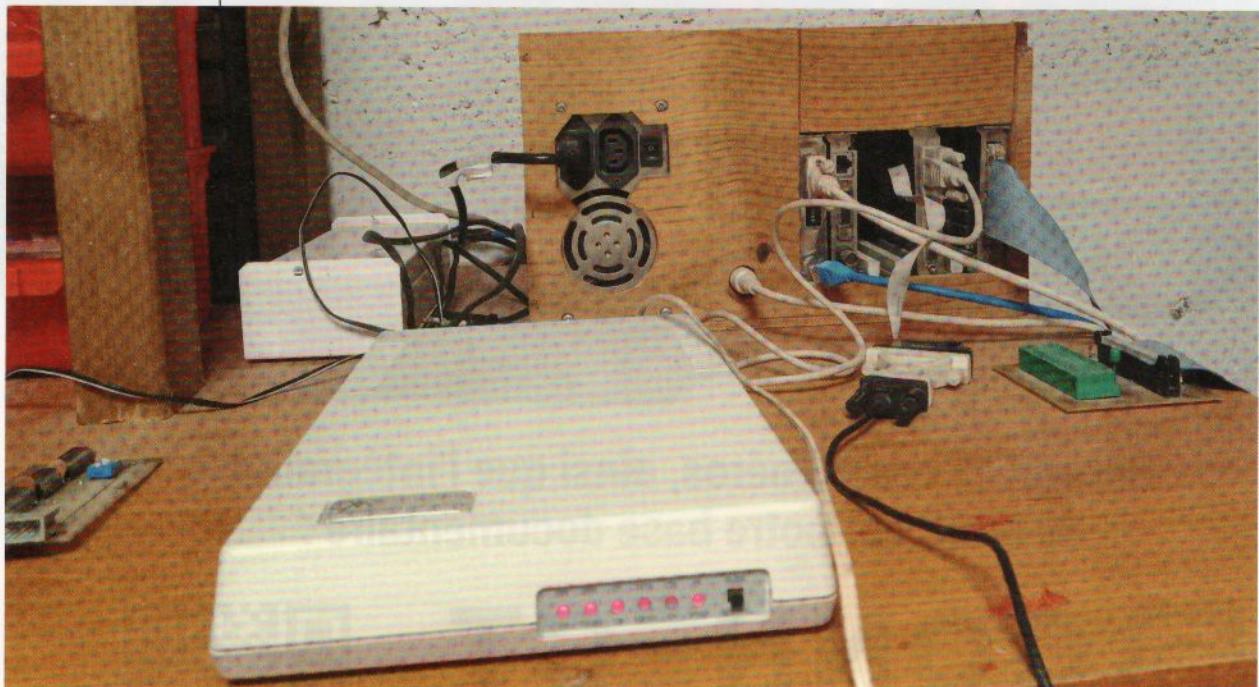

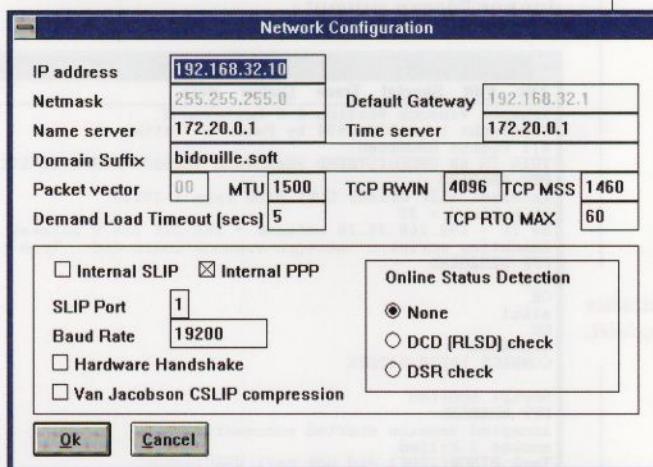

RS-232, carte FXS, RTC, PPP, **Asterisk**, Amstrad CPC 464... Et si on surfait comme en 1989 ? p.112

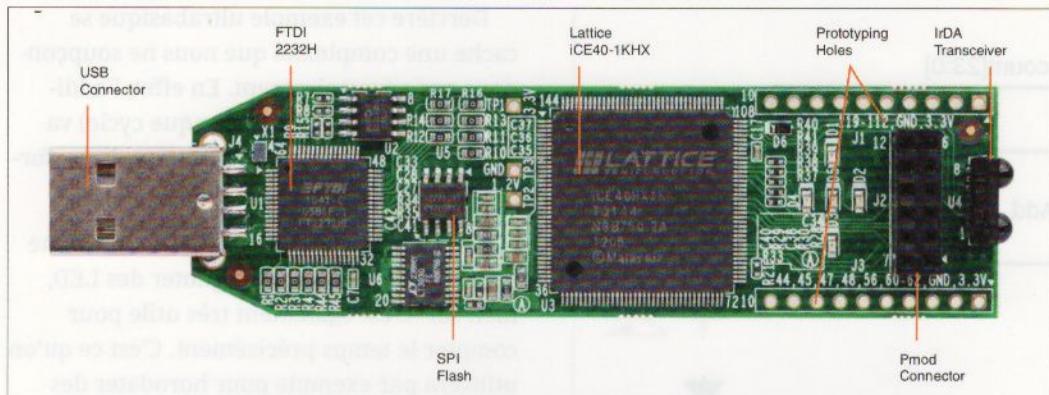

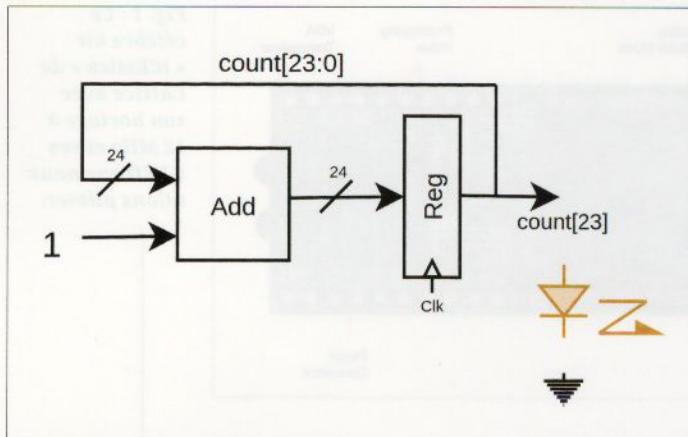

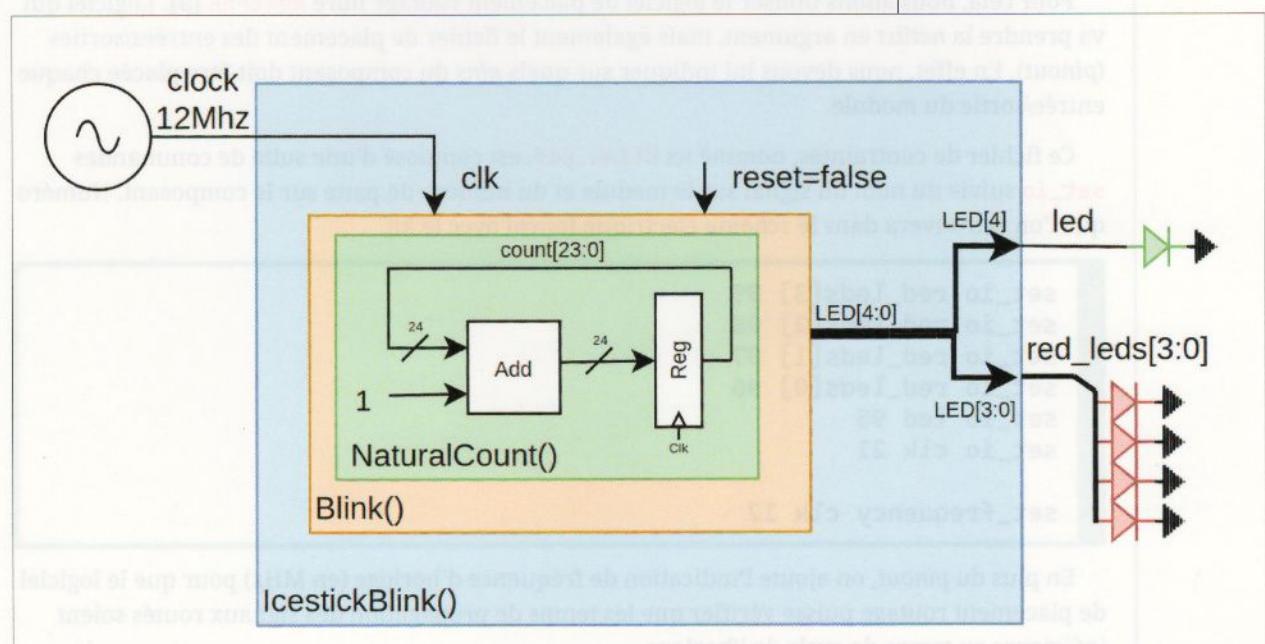

## ICESTICK / OPTIMISATION

Apprenez à augmenter les performances de vos circuits écrits en **Chisel** sur plateforme **ICE40** p.88

## ALIMENTATION / USB

**ALIENTEK DP100** : Prise en main et exploration d'une minuscule alimentation de laboratoire p.04

ÉDITION

#4

OPEN SOURCEZ

VOS SOLUTIONS IT

# OPEN SOURCE EXPERIENCE

PARIS

04 & 05

DÉCEMBRE 2024

- PALAIS

DES CONGRÈS

90 EXPOSANTS 100 CONFÉRENCES 125 SPEAKERS

[www.opensource-experience.com](http://www.opensource-experience.com)

Suivez-nous

#OSXP2024

Un événement

Systemic

Parts Region Deep Tech Ecosystem

organisé par

infoprodigital

TRADE SHOWS

NOUVEAU

CETTE ANNÉE !

Aux mêmes dates

et lieu que

DEVOPS REX

LA CONFÉRENCE DEVOPS

FRANCOPHONE

100% retour d'expérience

# JJ ÉDITO

Quelque chose est sur le point de changer dans l'embarqué... et pas seulement.

La sécurité des systèmes est plus que jamais sur le devant de la scène. L'industrie entière s'est enfin rendu compte des répercussions potentiellement catastrophiques de failles de sécurité au plus bas niveau et redouble d'efforts pour « régler » le problème. Mais on a beau tenter de « sécuriser » les systèmes, les applications, les services et même les langages, si une faiblesse existe, héritée de plusieurs dizaines d'années d'histoire de l'informatique moderne, elle sera forcément exploitée. Cette

faiblesse est la manière dont l'accès à la mémoire est géré par les processeurs et la corruption de cette mémoire, d'une façon ou d'une autre, représente statistiquement la principale cause des failles de sécurité.

Pour régler le problème, un nouveau paradigme a vu le jour et est sur le point de se généraliser, en particulier dans l'embarqué (dans un premier temps) : les *capabilities* et plus exactement l'adressage mémoire basée sur les *capabilities*. Le concept n'est pas nouveau, puisqu'il s'agit simplement d'associer une métadonnée à un objet (au sens large du terme), pour conférer ou non une « capacité » (d'où le nom) à manipuler cet objet. Ce qui est (presque) nouveau, en revanche, c'est d'intégrer ce mécanisme dans le processeur lui-même sous la forme d'une gestion mémoire étendue et d'instructions spécifiques. « Presque », parce que le System/38 d'IBM (1978) utilisait cette technologie, mais depuis, le mécanisme de pagination mémoire a été universellement adopté.

Le projet vers lequel convergent les recherches depuis quelque temps est celui de l'université de Cambridge : CHERI (pour *Capability Hardware Enhanced Risc Instructions*). Les constructeurs (ARM en tête avec son projet Morello, mais RISC-V n'est pas en reste), les éditeurs de logiciels, ainsi que les projets *open source* (Morello Linux, CheriBSD, LLVM, FreeRTOS, etc.) forcent la marche pour nous rapprocher d'un premier produit fini.

Difficile de prédire quand cette révolution aura lieu, et débarquera dans nos smartphones et nos SBC, mais elle est en route, et ça changera énormément de choses...

Denis Bodor

## Hackable Magazine

est édité par Les Éditions Diamond

BP 20142 - 67602 SELESTAT CEDEX - France

E-mail : lecteurs@hackable.fr

Service commercial : cial@ed-diamond.com

Sites : [hackable.fr](http://hackable.fr) - [ed-diamond.com](http://ed-diamond.com)

Directeur de publication : Arnaud Metzler

Rédacteur en chef : Denis Bodor

Réalisation graphique : Kathrin Scali

Régie publicitaire :

Valérie Fréchard - Tél. : 03 67 10 00 27

Service abonnement : Les Éditions Diamond BP 20142 - 67602 SELESTAT CEDEX, France, Tél. : 03 67 10 00 20

Impression : Westermann Druck | PVA, Braunschweig, Allemagne

Distribution France :

(uniquement pour les dépositaires de presse)

MLP Réassort : Plate-forme de Saint-Barthélémy-d'Anjou. Tél. : 02 41 27 53 12

Plate-forme de Saint-Quentin-Fallavier.

Tél. : 04 74 82 63 04

Service des ventes :

Abomarque - Tél. : 06 15 46 15 88

IMPRIMÉ en Allemagne - PRINTED in Germany

Dépot légal : À parution

N° ISBN : 2427-4631

CPPAP : K92470

Périodicité : bimestriel - Prix de vente : 14,90 €

La rédaction n'est pas responsable des textes, illustrations et photos qui lui sont communiqués par leurs auteurs. La reproduction totale ou partielle des articles publiés dans Hackable Magazine est interdite sans accord écrit de la société Les Éditions Diamond. Sauf accord particulier, les manuscrits, photos et dessins adressés à Hackable Magazine, publiés ou non, ne sont ni rendus, ni renvoyés. Les indications de prix et d'adresses figurant dans les pages rédactionnelles sont données à titre d'information, sans aucun but publicitaire. Toutes les marques citées dans ce numéro sont déposées par leur propriétaire respectif. Tous les logos représentés dans le magazine sont la propriété de leur ayant droit respectif.

Suivez-nous sur Twitter

@hackablemag

### POUR DEVENIR AUTEUR

Contactez :

[contrib@hackable.fr](mailto:contrib@hackable.fr)

Consultez :

[connect.ed-diamond.com](http://connect.ed-diamond.com)

## SOMMAIRE

### OUTILS & LOGICIELS

- 04** Alimentation de laboratoire

ALIENTEK DP100 : petite, mais costaud

- 18** Un oscilloscope à pédale

### SÉCURITÉ

- 34** Concevoir, mettre en place et bidouiller un environnement basé sur le protocole industriel Modbus

### FPGA & GATEWARE

- 54** Mon premier projet FPGA : un ordinateur 8 bits complet en VHDL

- 88** Pimp my LED counter, les performances de l'addition

### RÉTRO

- 112** Asterisk, RTC, PPP, CPC 464... Surfons comme en 1989 !

### ABONNEMENT

- 77** Abonnement

RETRouvez ce numéro et bien plus encore sur CONNECT

- » articles gratuits

» contenu premium

» listes de lecture...

[CONNECT.ED-DIAMOND.COM](http://CONNECT.ED-DIAMOND.COM)

### À PROPOS DE HACKABLE...

#### HACKS, HACKERS & HACKABLE

Ce magazine ne traite pas de piratage. Un **hack** est une solution rapide et bricolée pour régler un problème, tantôt élégante, tantôt brouillonne, mais systématiquement créative. Les personnes utilisant ce type de techniques sont appelées **hackers**, quel que soit le domaine technologique. C'est un abus de langage médiatisé que de confondre « pirate informatique » et « hacker ». Le nom de ce magazine a été choisi pour refléter cette notion de **bidouillage créatif** sur la base d'un terme utilisé dans sa définition légitime, véritable et historique.

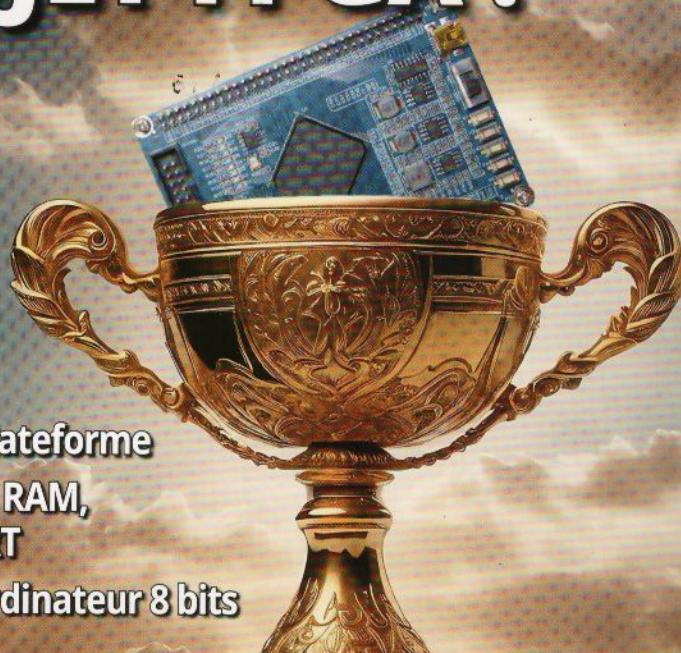

# ALIMENTATION DE LABORATOIRE ALIENTEK DP100 : PETITE, MAIS COSTAUD

Denis Bodor

L'alimentation de laboratoire fait partie des outils classiques lorsqu'on fait de l'électronique et de l'embarqué. Ceci prend généralement la forme d'un équipement volumineux destiné à prendre place sur un bench, entre la station de soudure et l'oscilloscope. Cependant, les mœurs ont sensiblement changé et souvent quelque chose de plus compact, pouvant prendre place sur un bureau à gauche du clavier est non seulement suffisant, mais plus adapté et ergonomique pour de « petits travaux ». Dans cette catégorie « outil miniature », je vous présente donc l'ALIENTEK DP100 USB-C...

- Alimentation de laboratoire ALIENTEK DP100 : petite, mais costaud -

**I**mager une alimentation de labo piochant son courant via un port USB-C peut faire doucement rigoler, mais ne vous y trompez pas, l'USB de pépé, c'est de l'histoire ancienne. Le « U » de USB, et en particulier d'USB-C, est aujourd'hui véritablement « Universal », tant ce connecteur est utilisé, aussi bien pour le transfert de données haut débit que pour l'alimentation et la charge. Ceci au point que même certains obsédés de la pomme californiens se sont vus contraints (merci, l'Europe) d'opter pour ce connecteur en lieu et place de leur propre création (« Lightning » se traduisant, selon mes sources, en « lol, donne-nous tes sous » dans un ancien dialecte mérovingien du sud-ouest de l'Ouzbékistan). On trouve de l'USB-C sur les laptops, les smartphones, les réglettes lumineuses, les multimètres, des disques externes, les clés de sécurité, etc. Et ce n'est pas que pour l'échange de données...

L'USB-C, ou plus exactement l'USB Type-C, est un simple connecteur, rien de plus et il doit être vu, dans une certaine mesure, comme étant détaché de l'USB, l'USB 3, 3.1, etc. En effet, ce connecteur de 24 broches permet le transport d'informations

avec bien d'autres protocoles de transmission que l'USB, parmi lesquels DisplayPort, Thunderbolt, PCIe, HDMI... Et ce n'est pas tout, la spécification *USB Power Delivery* (ou USB-PD) décrit également comment, et avec quelles caractéristiques, du courant peut être délivré à un périphérique, et ce avec une tension allant bien au-delà des 5 volts habituels que l'on connaît pour l'USB « classique ».

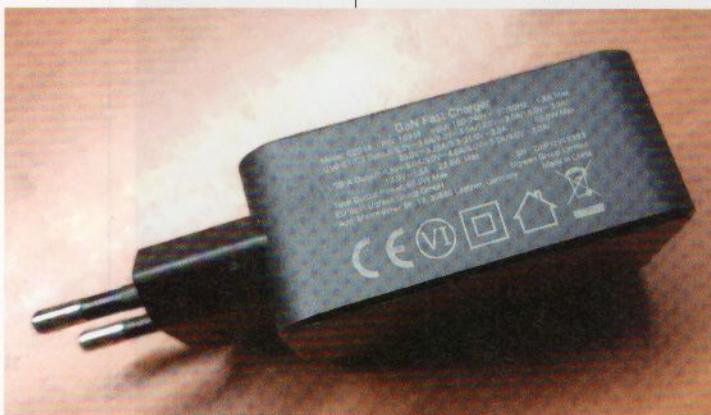

Avec une alimentation USB-PD et un périphérique compatible, le courant et la tension sont négociés entre les deux entités, permettant ainsi une charge rapide (pour les smartphones et *laptops*, par exemple). Ainsi, un unique bloc d'alimentation, comme mon UGREEN Nexode 65 W (~40 € sur Amazon), sera capable de fournir non seulement jusqu'à 5 A en 5 V pour un accu d'appoint USB ou un montage quelconque par exemple, mais également jusqu'à 3,25 A en 20 V pour mon portable Lenovo E480, remplaçant l'encombrant adaptateur d'origine livré avec l'ordinateur.

Pour éviter toute confusion, sur ce point du moins, une certification a été mise en place afin de permettre à l'utilisateur d'identifier clairement quels chargeurs et périphériques sont capables de supporter la gamme de puissances (15 W, 27 W, 45 W, 60 W, 100 W, 140 W, 180 W, 240 W) et de tensions (5 V, 9 V, 15 V, 20 V, 28 V, 36 V, 48 V) : c'est le fameux « *Fast Charge* » ou « *Certified USB Fast Charger* », accompagné d'un logo dédié, que l'on retrouve sur les différents équipements concernés.

*Le DP100 d'ALIENTEK est compact, très compact. Ceci s'avère certes pratique pour un usage nomade, mais uniquement à condition d'avoir des petits doigts et de bons yeux.*

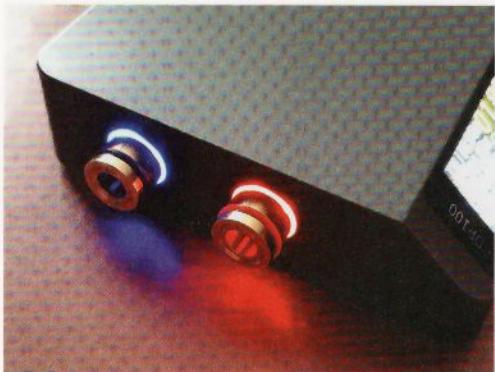

*Il faut l'avouer, même si l'utilité de cette fonctionnalité est relativement limitée (soyons honnêtes), les connecteurs fiche « banane » s'éclairant lorsque la sortie est active sont du plus bel effet.*

Ainsi, concernant le sujet qui nous intéresse ici, la notion d'alimentation de laboratoire reposant sur l'utilisation d'un bloc d'alimentation USB-C prend tout son sens, il ne s'agit pas simplement de 500 mA en 5 volts (ou 3 A dans le cas de l'USB-C non compatible « PD ») qu'on suppose habituellement lorsqu'on parle d'USB. Bien entendu, si j'en parle, c'est précisément parce que le matériel que nous allons explorer dans un instant est compatible USB-PD et qu'il devra être utilisé avec une source compatible, comme le matériel UGREEN que j'évoquais précédemment (pas question de brancher l'alimentation sur un port USB de PC, sauf exception, et encore).

## 1. PRISE EN MAIN DU DP100

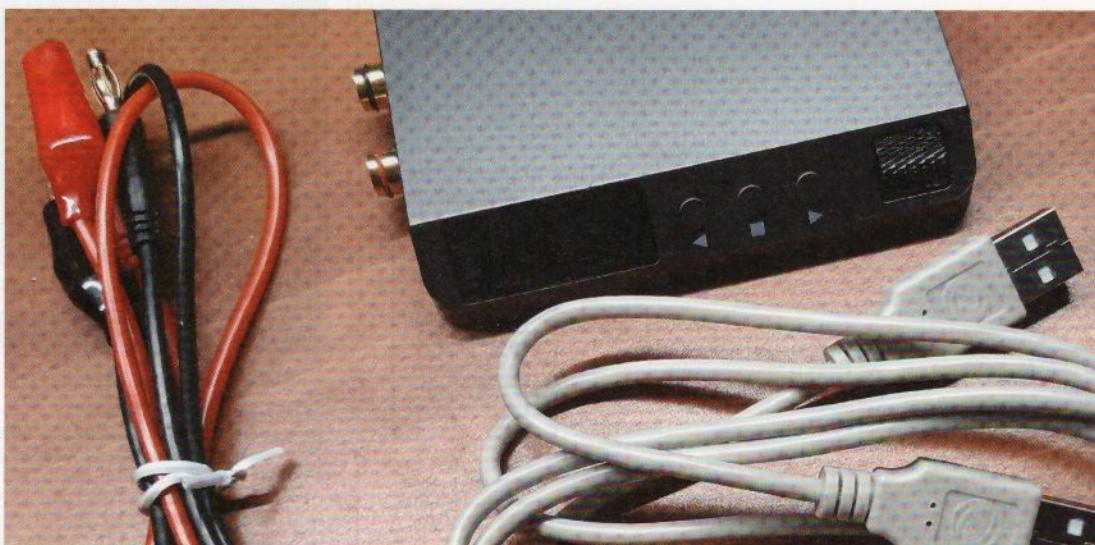

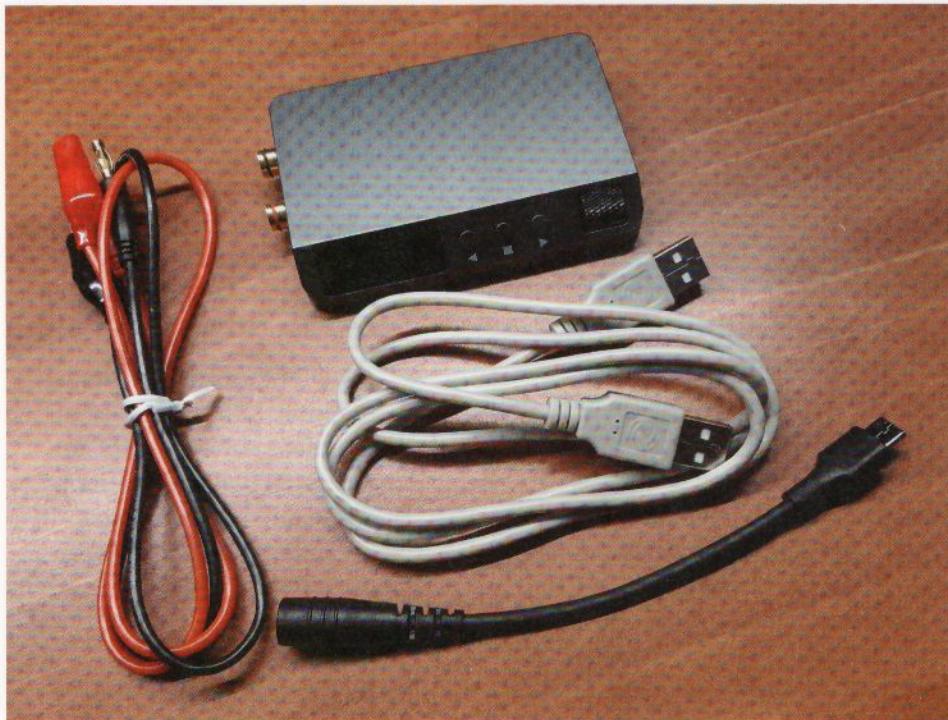

L'alimentation de laboratoire DP100 d'ALIENTEK se trouvera relativement facilement sur les sites habituels (Amazon, AliExpress et consorts). Selon la source d'approvisionnement (et donc le délai de livraison), ce petit joujou vous coûtera entre 60 € et 85 €. Le prix varie également en fonction des accessoires accompagnant le matériel et j'ai personnellement opté pour la solution « lente », mais économique en achetant directement cela dans le *store* ALIENTEK sur AliExpress [1]. Pour tout dire, notez que j'ai eu vent de ce matériel via une vidéo [2] de l'incomparable Dave Jones (EEVblog) analysant le circuit et procédant à quelques tests et mesures relativement satisfaisantes de son point de vue.

Le DP100 se présente sous la forme d'un petit pavé (95 mm x 62 mm x 16 mm) disposant d'un minuscule écran couleur (24 mm x 12 mm) et d'une interface (trois boutons + molette) sur l'un des côtés, incliné de 45°. Niveau connectique, l'alimentation se fait donc en USB-C via un bloc compatible USB-PD ou via un bloc « standard », maximum 32 V, via un adaptateur USB-C vers connecteur coaxial (*barrel jack*) de 5,5 mm

livré avec le produit. Juste à côté de l'USB-C, on trouve une prise femelle USB type A destinée à la connexion avec un ordinateur (mode périphérique) ou à l'alimentation USB 5 V (mode hôte 5 V/1 A). Un câble USB type A mâle/mâle (~1 m) est livré avec le DP100. Remarquez que la documentation livrée avec le produit parle également de la possibilité de connecter une souris USB sur ce port pour contrôler l'interface. C'est... original.

De l'autre côté, on retrouve les assez classiques emplacements pour fiches « banane » accueillant les câbles silicones rouge et noir (~60 cm) fournis et terminés par des pinces croco. Les connecteurs sont dévisables afin de permettre la connexion de fils dénudés par pincement, mais aussi, et surtout, sont étayés d'un anneau transparent s'éclairant (rouge et bleu) lorsque la sortie est active.

Au niveau de l'interface utilisateur et en dehors du fait que la taille de l'écran nécessite d'avoir de très bons yeux, le tout est relativement utilisable, à défaut d'être intuitif. Le « manuel » livré avec le matériel (anglais/mandarin) résume très bien la navigation dans les menus et on retiendra en premier lieu que les trois malheureux boutons possèdent

### - Alimentation de laboratoire ALIENTEK DP100 : petite, mais costaud -

plusieurs modes d'utilisation : simple pression, longue pression et double pression. Il est possible de régler les paramètres (courant et tension) de l'alimentation directement (bouton ■ et molette) ou d'utiliser les 10 présélections (ou profils) configurables via une pression longue sur ▶. La modification d'un profil se fait ensuite avec ■ pour passer d'un champ à l'autre, ▶ pour choisir le chiffre et la molette pour varier la valeur. Les profils permettent de configurer la tension, le courant, la limite de tension (OVP pour *Over Voltage Protection*) et celle de courant (OCP pour *Over Current Protection*). ↵ ↷

L'accès au menu des préférences se fait par double pression sur ■, puis on naviguera avec la molette pour ajuster le paramètre désiré (■ et ▶). Les entrées du menu sont :

- **Exit** : quitter la configuration ;

- **OVP Set** : tension max (protection) ;

- **OCP Set** : courant max (protection) ;

- **OPP Set** : puissance max (protection) ;

- **OTP Set** : température max (protection) ;

- **REP Set** : protection contre l'inversion de polarité ;

- **AUTO\_out** : sortie active automatiquement ;

- **PD\_Volt** : tension demandée en USB-PD (entrée) ;

- **Blk Set** : intensité lumineuse de l'écran ;

- **Vol Set** : volume du bip ;

- **USB Mode** : choix du mode pour l'USB-A ;

- **Language** : langue (anglais/mandarin) ;

- **Theme Col** : thèmes graphiques de l'interface (clair/sombre) ;

- **Restore** : réinitialise à la configuration d'usine ;

- **Ver\_info** : information de version du firmware.

L'activation de la sortie se fait par une simple pression sur le bouton ▶ et l'écran présente alors les valeurs de tension et de courant mesurées ainsi que le mode (« CC » pour courant constant et « CV » pour tension constante). Enfin, notez que noyé dans la documentation, nous avons la double pression sur ▲ pour marche/arrêt et la double pression sur ▶ pour basculer d'une tension USB-PD à une autre.

Vous l'aurez compris, la tension fournie en sortie dépendra totalement de celle en entrée. Le DP100 ne sortira pas de 20 V à partir d'une alimentation ne fournissant que 5 V (comme un adaptateur USB classique). En USB-C et avec USB-PD, la négociation de la tension en entrée dépendra de ce que peut fournir l'adaptateur secteur et de la configuration. Il m'est arrivé plus d'une fois de maladroitement presser plusieurs fois trop rapidement sur ▶, pour ensuite me demander pourquoi l'alimentation ne fournissait pas la tension attendue. La tension USB-PD demandée avait simplement basculé de 20 V à 9 V. Je trouve la double fonctionnalité de ce bouton (activation + choix USB-PD) peu judicieuse.

À l'usage et après un petit temps d'adaptation, l'alimentation s'avère fort utile, qu'il s'agisse de fournir du courant à un montage, surveiller la consommation ou même manuellement charger un accu. Bref, tout ce qu'on fait généralement avec un matériel plus encombrant. Bien entendu, tout n'est pas parfait, le DP100 alimenté avec un bloc USB-C/USB-PD de qualité sortira une tension et un courant stable et propre, mais la présence d'une unique sortie sera très limitante pour certains usages. La compacité du produit est à la fois un avantage, faible encombrement sur un bureau « normal » et un handicap, étant donné la faible lisibilité des informations présentées à l'écran. Mais pour ce point en particulier, il existe une solution...

## 2. INTERFACE AVEC UN ORDINATEUR

Comme précisé en début d'article, le DP100 peut être connecté à un PC, un Mac ou une Raspberry Pi. Non pour lui fournir une alimentation, mais pour permettre le contrôle de l'appareil. ALIENTEK met à disposition une application dédiée pour Windows sur le site officiel [3] et, d'après la documentation [4], celle-ci permet un accès plus ergonomique aux contrôles de l'appareil avec graphiques et prérglages, ainsi que la mise à jour du *firmware*. Je n'ai pas testé cette version pour deux raisons : l'accès au site était d'une lenteur catastrophique, et je n'ai aucune intention d'utiliser une application propriétaire dont je ne suis pas sûr à 100 %, même dans une VM ou un environnement émulé (Wine). De plus, l'intérêt d'une application proposant une interface graphique est, selon moi, très limité. Un tel programme doit permettre d'automatiser des opérations ou pouvoir être utilisé pour atteindre cet objectif. Ce qui n'est absolument pas le cas avec une GUI, aussi jolie et clinquante soit-elle...

L'idée étant de pouvoir télécommander l'alimentation, comme on le ferait avec un instrument compatible SCPI (*Standard Commands for Programmable Instruments*) tel le DP832 de RIGOL, il nous faut un outil, au minimum en ligne de commande, de manière à pouvoir filtrer la sortie avec les outils classiques UNIX (`sed`, `grep`, `awk`, etc.) et donner des ordres en composant un script invoquant la commande. L'utilitaire n'a donc pas besoin d'être directement scriptable, même si ceci serait un avantage certain. Dans ce genre de situation, le réflexe par défaut est de s'orienter vers GitHub/GitLab pour s'enquérir d'un développement préexistant.

Mais avant cela, commençons tout simplement par brancher le DP100 sur une machine GNU/Linux (PC ou SBC comme une Raspberry Pi), pour voir ce que le système en pense :

```

$ dmesg

[...]

new full-speed USB device number 22 using xhci_hcd

New USB device found, idVendor=2e3c,

idProduct=af01, bcdDevice= 2.00

New USB device strings: Mfr=1, Product=2,

SerialNumber=3

Product: ATK-MDP100

Manufacturer: ALIENTEK

SerialNumber: 223AF571C000

hid-generic 0003:2E3C:AF01.000D: hiddev0,hidraw4:

USB HID v1.10 Device [ALIENTEK ATK-MDP100]

on usb-0000:04:00.4-2.1.3.4/input0

```

Le matériel, identifié par les VID/PID USB **0x2e3c:0xaf01**, est énuméré comme étant un périphérique USB HID, ce qui n'est guère étonnant puisque HID, en plus d'être le protocole pour les claviers/souris, est généralement aussi celui utilisé pour toutes sortes de « gadgets », du notificateur de mail au lance-missile USB en passant par les clés de sécurité et gestionnaires de mot de passe matériels.

Même sans savoir quel outil nous finirons par utiliser, la première chose à faire est de gérer correctement les permissions sur le périphérique. Ceci passe par la configuration d'une règle `udev` nous évitant de devoir utiliser l'identité du super-utilisateur `root` pour lire/écrire sur le périphérique (entrée `/dev/hidraw4` ici, pour l'accès HID « brut »).

- Alimentation de laboratoire ALIENTEK DP100 : petite, mais costaud -

*Le produit est livré avec un jeu de câbles de relativement bonne facture. Notez le câble USB type A mâle/mâle permettant la connexion à un ordinateur ou SBC. Ce type de câble n'est pas courant, donc... à ne pas perdre.*

Notre règle, placée par exemple dans un fichier `alientekDP100.rules` dans `/etc/udev/rules.d`, ressemblera à ceci (sur une ligne) :

```

KERNEL=="hidraw*", ATTRS{idVendor}=="2e3c",

ATTRS{idProduct}=="af01", MODE="0660", GROUP="plugdev"

```

Ceci aura pour effet, lors de la connexion du DP100 reconnu via ses identifiants USB pour le sous-système/support `hidraw`, d'ajuster les permissions afin de permettre aux membres du groupe `plugdev` de lire et d'écrire l'entrée correspondante dans `/dev`. J'en profite d'ailleurs pour signaler que bon nombre de documentations en ligne précisent les nouvelles permissions à appliquer avec `MODE="0666"`. Ceci est totalement stupide, car revient à autoriser les opérations de lecture et d'écriture pour le propriétaire (`root`), les membres du groupe `plugdev`, et... **n'importe qui d'autre (others)**. Oui, c'est plus simple, mais pourquoi ne pas faire directement `sudo chmod -R 666 /*` dans ce cas ?!

Quoi qu'il en soit, une fois cette nouvelle règle ajoutée, on pourra demander à `udev` de relire sa configuration et réappliquer immédiatement les règles avec :

```

$ sudo udevadm control --reload-rules

$ sudo udevadm trigger

```

Un simple `ls -l` devrait vous confirmer que le périphérique est maintenant utilisable à souhait par l'utilisateur courant (membre de `plugdev` en principe).

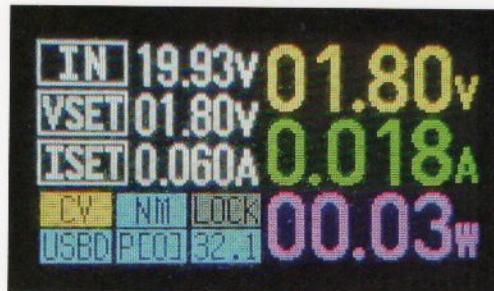

Zoomé ainsi, l'écran du DP100 est bien agencé et lisible, étant donné le nombre d'informations affichées. Seul petit problème, il ne fait en réalité que 24 mm de large pour 12 mm de haut.

Si nous retournons vers GitHub à présent, et cherchons « DP100 », nous trouvons quelques développements intéressants... qui ne concernent pas ce qui semble être une certification Microsoft. Parmi lesquelles :

- WebDP100 [5] : un début de projet en TypeScript destiné à fonctionner dans un navigateur supportant WebHID (Chrome, Chromium, Edge, etc.). Dans une vidéo liée à la page, l'auteur précise qu'il n'a aucune intention de développer une interface complète.

- Alientek-DP100-PyQT5 [6] qui est un fork traduit en anglais d'un projet identique écrit en Python avec une interface graphique Qt5 assez similaire à l'application du constructeur. Ce code repose sur l'utilisation des fichiers DLL du fabricant et possède donc une composante propriétaire (en plus d'être une application GUI).

- pydp100 [7], une poignée de scripts Python assez basiques.

- « Alientek DP100 experiments » [8], un tout début de module, très récent, écrit en Go qui se limite, pour l'instant, à l'envoi et la réception de rapports HID.

- open\_dp100 [9] qui est un outil utilisable, écrit en Rust, accompagné de quelques explications (en chinois) détaillant le protocole utilisé.

C'est vers ce dernier code que nous allons nous diriger, car c'est clairement ce qui se rapproche le plus d'un utilitaire

répondant à nos besoins et nous permettra éventuellement de développer davantage le concept ou, plutôt, de réimplémenter le tout dans un autre langage plus en alignment avec nos préférences, étant donné que le dépôt ne contient pas de licence et le code doit donc supposé être non réutilisable en l'état.

Installer Rust sur un système GNU/Linux, ARM ou x86, est un jeu d'enfant puisqu'il suffit de récupérer et invoquer un script shell qui fera tout le travail à votre place, tel que détaillé sur le site officiel : `curl --proto '=https' --tlsv1.2 -sSf https://sh.rustup.rs | sh`. La simple exécution de cette commande vous résumera les options d'installation et vous demandera le type d'installation souhaité. Choisissez simplement « `Proceed with standard installation` », l'environnement Rust sera installé (via `rustup`) dans `~/.cargo` et une ligne ajoutée automatiquement à votre `~/.bashrc`. Ceci fait, déconnectez-vous et reconnectez-vous (ou utilisez `source "$HOME/.cargo/env"` directement) pour rendre le tout utilisable. Si vous n'avez plus besoin de Rust par la suite, vous pourrez supprimer les éléments installés en effaçant les répertoires `~/.cargo` et `~/.rustup`, ainsi que la ligne ajoutée au `.bashrc`.

Nous pouvons alors nous placer dans un répertoire quelconque et cloner le dépôt « `open_dp100` » avec `git` et directement compiler et procéder à un premier essai :

- Alimentation de laboratoire ALIENTEK DP100 : petite, mais costaud -

```

$ git clone https://github.com/lessu/open_dp100.git

Clonage dans 'open_dp100'...

remote: Enumerating objects: 58, done.

remote: Counting objects: 100% (58/58), done.

remote: Compressing objects: 100% (40/40), done.

remote: Total 58 (delta 21), reused 47 (delta 15), pack-reused 0

Réception d'objets: 100% (58/58), 21.66 Kio | 4.33 Mio/s, fait.

Résolution des deltas: 100% (21/21), fait.

$ cd open_dp100

$ cargo build

Updating crates.io index

Downloaded cc v1.0.98

Downloaded cfg-if v1.0.0

[...]

Finished `dev` profile [unoptimized + debuginfo]

target(s) in 3.60s

$ ./target/debug/cli ls

Device count: 1

1 ATK-DP100 sn:0AA71805 hdw_ver:1.4

app_ver:1.4 2024-04-03

$ ./target/debug/cli status

Device 0 name:ATK-DP100

Basic Info:

vin:19.963V

vout:0V

iout:0A

vo_max:19.34V

temp1:31.5°C

temp2:31.4°C

dc_5v:5.067V

out_mode:2

work_st:0

Basic Set <9>: Off

vo_set:15V

io_set:5A

ovp_set:5V

ocp_set:5.05A

```

Comme vous pouvez le constater, nous obtenons assez facilement les informations en provenance du matériel, se résumant, plus ou moins, à ce qui est déjà affiché sur son écran. En branchant une LED (rouge 8 mm) et en réglant 4 V/20 mA avant d'activer la sortie, nous obtenons :

```

Basic Info:

[...]

vout:1.805V

iout:0.019A

[...]

out_mode:0

```

Et en changeant pour 1,8 V/60 mA, nous avons :

```

Basic Info:

[...]

vout:1.802V

iout:0.019A

[...]

out_mode:1

```

`out_mode` correspond donc respectivement à : **2** pour sortie désactivée, **0** pour courant constant (ici, 20 mA) et **1** pour tension constante (ici, 1,8 V). Ceci est déjà très utile dans l'état, car nous pouvons alors très simplement, dans un script shell, récupérer cette information au fil du temps pour accumuler des données et procéder à une sorte de surveillance, avec un journal et même produire un graphique si nécessaire.

L'outil cependant ne semble pas fini ou du moins pas au point d'en faire quelque chose d'autre de « publiquement » utilisable. Il n'y a, par exemple, qu'une gestion très partielle des erreurs sur les commandes passées en argument. Une commande erronée affichera un message intellligible avec une suggestion, tout comme `help` fournira une liste (partielle) de commandes, mais omettre totalement l'argument provoquera une erreur non gérée :

```

$ ./target/debug/cli

thread 'main' panicked at src/cli.rs:254:14:

internal error: entered unreachable code

note: run with `RUST_BACKTRACE=1` environment

variable to display a backtrace

```

Côté contrôle, les opérations semblent limitées par le protocole utilisé ou, du moins, par l'état actuel du travail d'analyse de ce dernier. Nous pouvons par exemple activer/désactiver la sortie avec `set on` ou `set off` ou modifier les valeurs courantes (`set v=1.30 i=0.020 ov=10.00 oc=1.00`), ou une seule (`set v=1.05`), ou encore activer un des profils (`set config=0`). Il est également possible de combiner ces opérations (`set v=2.28 i=0.025 on`), mais les possibilités s'arrêtent là. Il ne semble ainsi pas possible de modifier les profils enregistrés ou de changer les préférences globales stockées dans l'appareil. Notez que le fichier

– Alimentation de laboratoire ALIENTEK DP100 : petite, mais costaud –

**100\_Protocol.md**, inclus avec les sources, détaille ce qui est connu du protocole et ce qui est testé/vérifié.

Cet outil est, je pense, très intéressant, en particulier pour quelqu'un ayant des affinités avec Rust et sera donc capable de faire évoluer le code et de proposer des modifications à son auteur. Pour un usage dans un script, il fournit déjà le nécessaire, mesure et contrôle, et permettra d'atteindre notre objectif.

### 3. FONCTIONNEMENT EN RÉSEAU

« Mais m'sieur, y a pas de réseau avec le DP100 ! » me direz-vous incrédule. Ce à quoi je vous répondrai « Créature de peu de foi ! Quand on veut, on peut. » Et effectivement, on peut, de bien des manières même. Mais celle que je vais explorer ici consistera à littéralement déporter le périphérique lui-même sur une autre machine où il sera utilisable comme s'il était local. Ce petit miracle est possible grâce au support USBIP du noyau Linux et fonctionnera avec n'importe quel périphérique USB.

Le fonctionnement est relativement simple : choisir un périphérique USB sur la machine, l'exporter pour le rendre utilisable à distance et, sur un autre poste, l'attacher via le réseau. Celui-ci apparaîtra alors comme un périphérique USB local et sera pris en charge par les pilotes adéquats (USB-HIB, ici). Vous pouvez faire de même avec une

clé de stockage, une webcam, une carte Arduino, un débogueur JTAG... littéralement n'importe quoi !

Le support pour cette fonctionnalité étant intégré au niveau noyau et intervenant sur du matériel, la première chose à faire est de charger un module noyau avec :

- **sudo modprobe usbip-host** sur la machine où est branché le DP100 (le serveur) ;

- **sudo modprobe vhci-hcd** (VHCI pour *Virtual Host Controller Interface*) sur celle faisant fonctionner l'utilitaire que nous venons de compiler et tester (le client).

Il faut, ensuite, installer les outils adéquats sur les deux machines via **sudo apt-get install usbip** (Debian, Raspbian, Raspberry Pi OS, Ubuntu, etc.). La règle *udev* que nous avons précédemment vue doit être en place sur la machine « cliente », puisque le périphérique semblera effectivement connecté à cet hôte. Sur le serveur, ceci n'est pas nécessaire puisque l'accès se fait, de toute façon, avec des priviléges maximum. Ici, nous partirons du principe que le DP100 est connecté à une Raspberry Pi et l'outil fonctionne sur PC.

*L'alimentation du DP100 se fait via USB-C (à droite). Le port USB type A à gauche peut être configuré pour fournir 5 V/1 A (mode hôte) ou être utilisé pour la liaison avec un ordinateur (mode périphérique).*

## OUTILS & LOGICIELS

Ainsi, côté Pi, nous commençons par lister les périphériques présents :

```

$ sudo usbip list -l

- busid 1-1.1.1 (0424:7800)

Microchip Technology, Inc. (formerly SMSC) : unknown product (0424:7800)

- busid 1-1.1.3 (2e3c:af01)

unknown vendor : unknown product (2e3c:af01)

```

Nous voyons l'interface Ethernet de la Pi et le DP100 connecté sur le bus 1, port 1 (hub), port 1 (du hub), périphérique 3 : **1-1.1.3**. Il nous suffit alors d'utiliser cette désignation pour exporter le périphérique en question :

```

$ sudo usbip bind -b 1-1.1.3

usbip: info: bind device on busid 1-1.1.3: complete

```

L'export est fait, le noyau sait que ce périphérique est attaché au support USBIP, mais nous devons également permettre l'accès distant en lançant le serveur gérant les connexions :

```

$ sudo usbipd

usbipd: info: starting usbipd (usbip-utils 2.0)

usbipd: info: listening on 0.0.0.0:3240

usbipd: info: listening on :::3240

```

Notez qu'il est possible d'automatiser cela en créant un service pour lancer ce démon et l'intégrer à la configuration actuelle de Systemd. Personnellement, et vu mon dédain pour ce système d'Init, je préfère m'en abstenir. Côté PC, nous pourrons alors lister les périphériques mis à disposition par le serveur :

```

$ sudo usbip list -r raspilaser.local

Exportable USB devices

=====

- raspilaser.local

1-1.1.3: unknown vendor : unknown product (2e3c:af01)

: /sys/devices/platform/soc/3f980000.usb/usb1/1-1/1-1.1/1-1.1.3

: (Defined at Interface level) (00/00/00)

```

J'utilise ici le nom de la machine (résolution mDNS), mais vous pourrez tout aussi bien utiliser son IP directement. On voit clairement que le périphérique **2e3c:af01** est exporté et utilisable. Cette première connexion apparaît côté serveur dans le terminal où est lancé le démon **usbipd** :

```

usbipd: info: connection from 192.168.0.154:57356

usbipd: info: received request: 0x8005(5)

usbipd: info: exportable devices: 1

usbipd: info: request 0x8005(5): complete

```

- Alimentation de laboratoire ALIENTEK DP100 : petite, mais costaud -

On pourra alors attacher le périphérique en utilisant le nom ou l'IP du serveur et en spécifiant le chemin vers le matériel dans l'arborescence USB distante :

```

$ sudo usbip attach -r raspilaser.local -b 1-1.1.3

```

Encore une fois, le serveur nous informe de l'opération :

```

usbipd: info: connection from 192.168.0.154:37086

usbipd: info: received request: 0x8003(5)

usbipd: info: found requested device: 1-1.1.3

usbip: info: connect: 1-1.1.3

usbipd: info: request 0x8003(5): complete

```

À partir de ce moment, tout le reste du système côté PC réagit exactement comme si le périphérique venait d'être branché physiquement. On retrouve une trace de cette détection dans la sortie de la commande `dmesg` où il est fait mention à la fois de `vhci_hcd` se présentant comme un nouveau contrôleur USB et du périphérique USB HID comme avec une utilisation locale. La commande `lsusb` listera d'ailleurs le DP100 parmi les périphériques locaux :

```

$ lsusb

[...]

Bus 001 Device 003: ID 2109:2817 VIA Labs, Inc. USB2.0 Hub

Bus 005 Device 004: ID 2e3c:af01 ALIENTEK ATK-MDP100

Bus 005 Device 001: ID 1d6b:0002 Linux Foundation 2.0 root hub

Bus 004 Device 002: ID 2109:0817 VIA Labs, Inc. USB3.0 Hub

[...]

```

Et, bien sûr, notre utilitaire pour le DP100 fonctionnera exactement comme avant :

```

$ ./target/debug/cli status

Device 0 name:ATK-DP100

Basic Info:

vin:19.963V

vout:0V

iout:0A

vo_max:19.33V

temp1:31.8°C

temp2:31.7°C

dc_5v:5.061V

out_mode:2

work_st:0

Basic Set <0>: Off

vo_set:1.8V

io_set:0.06A

ovp_set:0.06V

ocp_set:5.05A

```

Une fois les manipulations terminées, vous pourrez détacher le périphérique côté PC avec :

```

$ sudo usbip detach -p 00

usbip: info: Port 0 is now detached!

```

puis arrêter le serveur côté Pi (Ctrl+C) avant de mettre fin à l'export :

```

$ sudo usbip unbind -b 1-1.1.3

usbip: info: unbind device on busid 1-1.1.3: complete

```

Cette technique vous permettra de manipuler de manière totalement transparente un périphérique USB à travers le réseau local, mais fonctionnera exactement de la même manière via un VPN, par exemple. Non testé ici, il semblerait que ceci fonctionne également entre un hôte Linux (serveur) et un client WSL sous Windows, afin de contourner l'absence d'accès direct au matériel dans cet environnement virtualisé. Et, encore une fois, on ne parle clairement pas que du DP100. Les possibilités sont absolument incroyables...

*Ceci est un bloc d'alimentation UGREEN Nexode Travel 65 W compatible USB-PD (~30 €), avec deux ports USB-C et un USB-A. Il est capable de fournir 5 V/3 A, 9 V/3 A, 12 V/3 A, 15 V/3 A et 20 V/3,25 A. Je l'utilise à la fois pour le DP100, alimenter des montages (USB-A), charger mon smartphone Samsung A40 et alimenter mon laptop Lenovo E480.*

## CONCLUSION

J'avoue que j'aime beaucoup ce matériel qui se glissera dans la trousse à outils facilement et constitue une solution « de bureau » très pratique. Bien entendu, ceci ne remplacera jamais une « vraie » alimentation de laboratoire comme la RIGOL DP832 (400 €) également pilotable en USB et LAN, mais proposant une interface plus agréable et plusieurs sorties contrôlables. Le prix, quelque 60 €, est un tantinet élevé à mon sens, bien que la qualité soit au rendez-vous. Pour quelque 10 ou 15 euros de moins, la question de la pertinence de l'achat ne se poserait même pas...

Voilà pour l'aspect purement pratique. Mais la partie la plus tentatrice à mon avis est l'outil de contrôle USB HIB qui ne demande qu'à être réimplémenté en ajoutant une myriade de fonctionnalités. Je pense naturellement à un développement en C, langage que je connais et aime, mais Go, Zig ou même Python peuvent être des pistes

– Alimentation de laboratoire ALIENTEK DP100 : petite, mais costaud –

intéressantes. On peut envisager d'intégrer un support Lua (voir article sur le sujet dans Linux Magazine 269 [10]) par exemple, pour rendre le tout scriptable, mais également la création de journaux de mesures, la génération de graphiques ou même le développement de greffons pour différents systèmes ou applications. Les idées ne manquent pas, le temps... oui, toujours. ■ DB

## RÉFÉRENCES

- [1] <https://fr.aliexpress.com/item/1005005992326848.html>

- [2] <https://www.youtube.com/watch?v=Pd6LG7iP2GQ>

- [3] <https://www.alientek.com/download>

- [4] [https://akizukidenshi.com/goodsuffix/DP100\\_manual.pdf](https://akizukidenshi.com/goodsuffix/DP100_manual.pdf)

- [5] <https://github.com/scottbez1/webdp100>

- [6] <https://github.com/ketukil/Alientek-DP100-PyQT5-english-gui>

- [7] <https://github.com/palzhj/pydp100>

- [8] <https://github.com/jonathangjertsen/dp100>

- [9] [https://github.com/lessu/open\\_dp100](https://github.com/lessu/open_dp100)

- [10] <https://connect.ed-diamond.com/gnu-linux-magazine/glmf-269/embarquez-un-peu-de-lua-dans-vos-projets-c>

## ENVIE D'EN SAVOIR PLUS SUR LES ALIMENTATIONS ?

Découvrez nos articles sur notre base documentaire Connect :

Hackable 32

Reverse-engineering

d'une alimentation

numérique et

contrôle avec bash

Hackable 15

Contrôlez votre

alimentation de

laboratoire avec

votre Raspberry Pi

CONNECT.ED-DIAMOND.COM

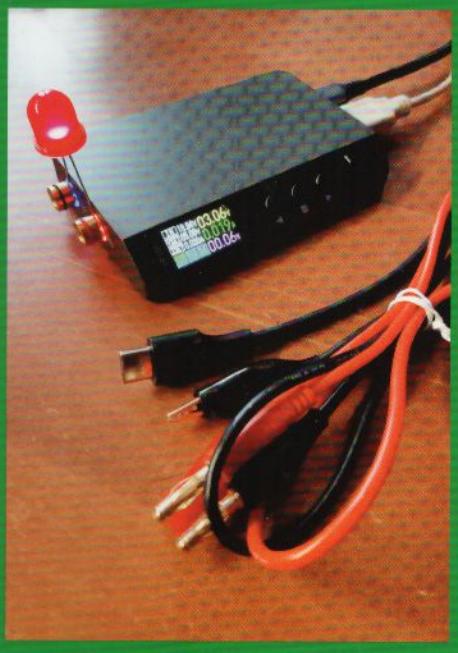

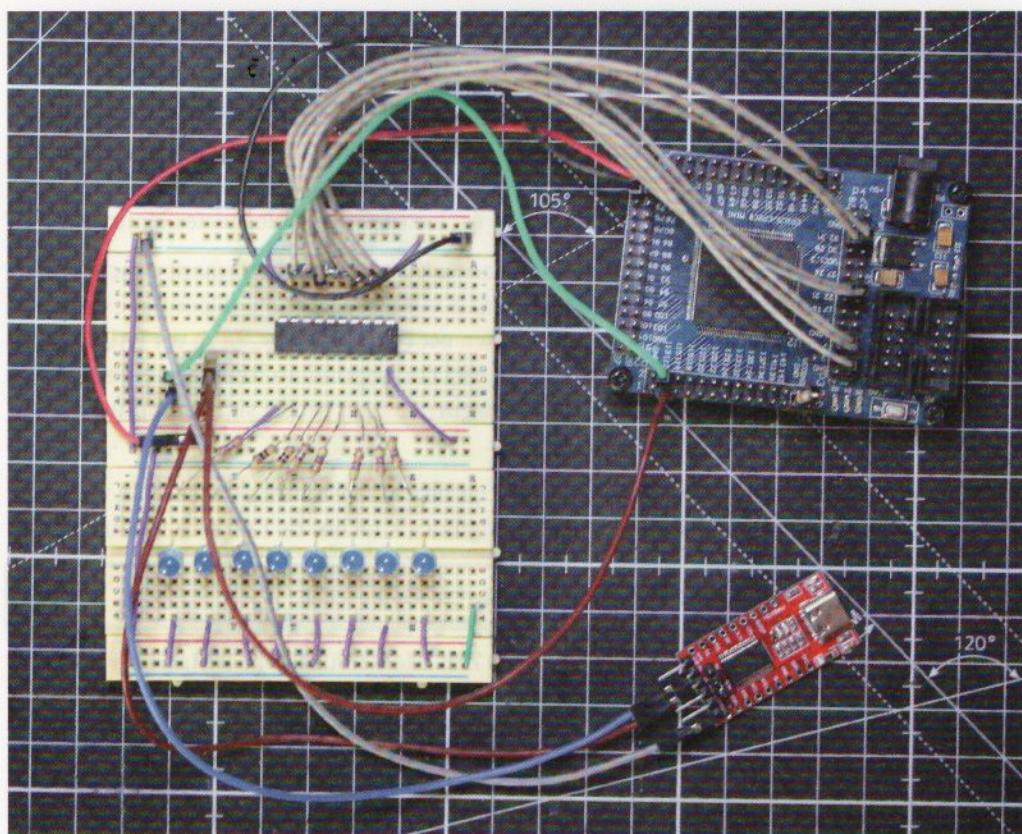

# UN OSCILLOSCOPE À PÉDALE

Fabien Marteau

Front de libération des FPGA

**Les électroniciennes et électroniciens sont des humains comme les autres, ils ont deux mains, deux pieds et une tête. Quand il s'agit de faire des mesures avec les deux sondes de l'oscilloscope, les deux mains sont vite prises.**

**Comment peut-on encore appuyer sur les boutons de l'engin alors que toutes nos mains sont occupées ? Et si nous utilisions nos pieds ? À l'heure de la démocratisation du vélo utilitaire, il est temps d'ajouter une pédale à votre oscilloscope.**

– Un oscilloscope à pédale –

**Fig. 1 :**

Oscilloscope ?

Vélo ?

Véloscope ?

**P**our bien démarer votre nouveau montage, vous avez branché le 5 V sur une alimentation stabilisée plutôt que sur l'USB, histoire de bien voir la consommation et de limiter le courant en cas de problème de court-circuit.

Vous avez également bien pris soin de régler votre oscilloscope pour qu'il déclenche sur front descendant du TX de l'UART que vous allez *monitorer* avec une première sonde dans

une main et vous *monitez* le RX avec la seconde sonde dans l'autre main. L'objectif de cette mise en route est de pouvoir saisir le chronogramme de la première trame TX envoyée par votre montage.

Tout est prêt, vos deux mains sont prises par les sondes de l'oscilloscope, la base de temps est réglée correctement pour voir passer les caractères à 115200 bauds et vous voyez bien passer la trame. Vite vite vite, il faut stopper l'oscilloscope pour qu'il ne redéclenche pas sur les trames suivantes !

Et là, c'est le drame. Si vous lâchez une sonde pour appuyer sur le bouton, l'oscilloscope va déclencher à nouveau et vous perdrez la trame voulue. Si vous restez comme ça à tenir vos sondes, vous aurez les trames suivantes, mais pas celle que vous vouliez. Vous pouvez bien essayer d'appuyer sur le bouton avec le nez ou le coude, mais l'acrobatie est loin d'être garantie. Évidemment, vous n'avez pas pu régler l'oscilloscope en mode « single » pour qu'il s'arrête

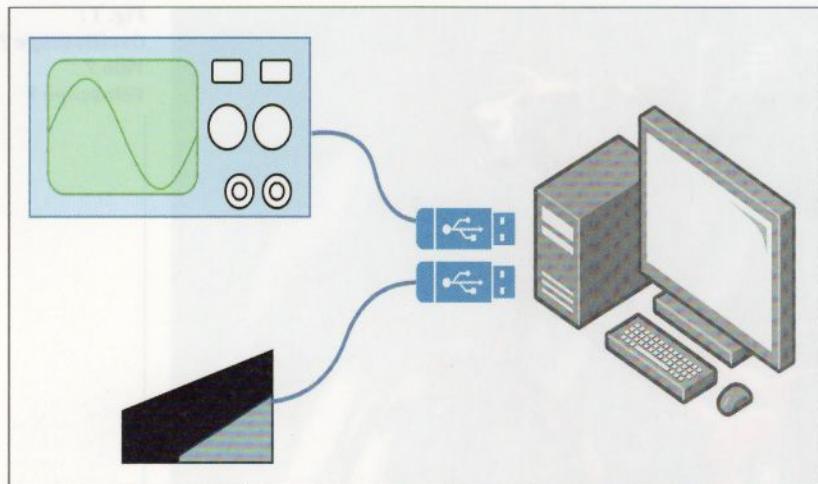

**Fig. 2 :**

Branchement

de l'oscilloscope

à pédale.

L'oscilloscope

ainsi que la pédale

sont branchés

sur un PC qui

se chargera de

piloter le premier

sur pression du

pied.

au premier déclenchement, puisqu'au démarrage votre montage envoie un *glitch* qui aurait déclenché avant la trame TX de l'UART.

Alors, que faire ?

En général, le problème est résolu en demandant à Gégé de la compta de venir donner un coup de main, ou à junior, si c'est un bricolage perso dans sa cave. Mais nous n'avons pas toujours quelqu'un à disposition pour bricoler, et puis ce n'est pas un rôle ultra palpitant que de se tenir à côté de la bricoleuse ou du bricoleur pour appuyer sur le bouton sur ordre, le moment venu.

Les électroniciennes et électroniciens ne se sont pas encore reproduits suffisamment longtemps entre eux pour se transformer en Shiva avec deux bras supplémentaires dans le dos. Cependant, la plupart sont dotés de deux pieds en plus de leurs deux bras, pourquoi ne pas les utiliser ?

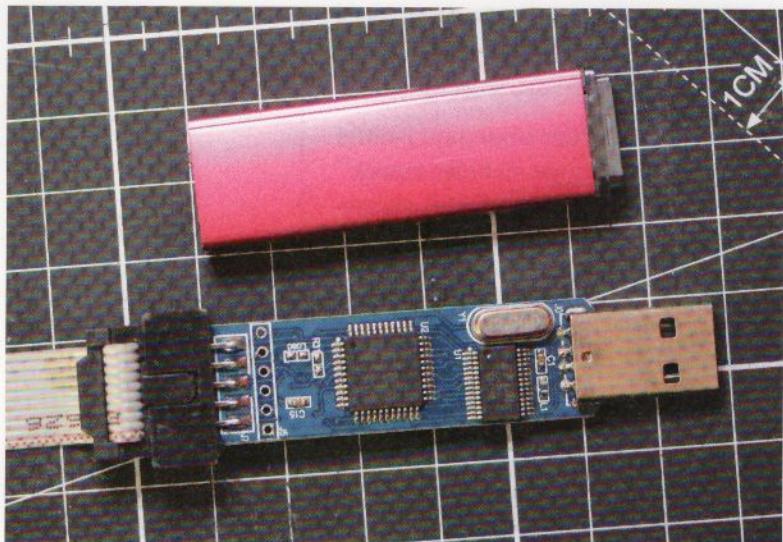

Dans cet article, nous allons voir comment ajouter une pédale USB à notre oscilloscope, de manière à déclencher le bouton STOP de l'appareil avec le pied. Nous utiliserons un oscilloscope actuel supportant le standard **VISA** et muni d'un port de contrôle sur USB que nous brancherons à un ordinateur sous GNU/Linux. Nous y ajouterons une pédale (trouvée sur

la célèbre plate-forme chinoise pour une dizaine d'euros) qui se branche sur USB.

Nous allons également voir que toutes les briques logicielles permettant de faire ce montage sont déjà disponibles et documentées. Ça n'est même pas un *hack*. Il est possible d'ajouter une pédale à n'importe quel oscilloscope moderne, du moment qu'il soit connectable à un ordinateur et que le protocole soit documenté et au standard **VISA**.

Le pilotage d'instrument de mesure par USB a déjà été traité par Jean-Baptiste Vioix dans les colonnes de Hackable [1] avec des appareils **RIGOL**. Yann Guidon a également écrit un article pour piloter l'alimentation de laboratoire **AX-6002P** de marque **AXIOMET** [2].

Nous utiliserons ici un oscilloscope **Siglent**. Comme il est également compatible avec le standard **VISA**, nous pourrons nous référer à l'article.

## 1. BRANCHEMENT DE L'OSCILLOSCOPE

L'oscilloscope utilisé pour cet article est un **SDS1202X-E** conçu par l'entreprise **Siglent**. Cet oscilloscope numérique est pilotable par USB et Ethernet.

Voyons ce que donne le branchement de l'USB sous GNU/Linux (Mint 20) :

– Un oscilloscope à pédales –

```

[73208.563506] usb 1-1: new high-speed USB device number 4 using xhci_hcd

[73208.716657] usb 1-1: config 1 interface 0 altsetting 0 bulk endpoint 0x81

has invalid maxpacket 64

[73208.716665] usb 1-1: config 1 interface 0 altsetting 0 bulk endpoint 0x1

has invalid maxpacket 64

[73208.716670] usb 1-1: config 1 interface 0 altsetting 0 endpoint 0x82 has

an invalid bInterval 0, changing to 7

[73208.724524] usb 1-1: New USB device found, idVendor=f4ed, idProduct=ee3a,

bcdDevice=99.99

[73208.724531] usb 1-1: New USB device strings: Mfr=1, Product=2,

SerialNumber=3

[73208.724535] usb 1-1: Product: SDS1202X-E

[73208.724539] usb 1-1: Manufacturer: Siglent

[73208.724543] usb 1-1: SerialNumber: SDS1EDEQ3R4790

[73208.868510] usbcore: registered new interface driver usbtmc

```

L'appareil semble bien reconnu par le noyau qui reconnaît le nom du produit, le fabricant ainsi que son numéro de série **SDS1EDEQ3R4790**. Comme c'est un branchement par USB, nous avons également un numéro de vendeur (**idVendor**) en hexadécimal 0xf4ed ainsi qu'un numéro de produit (**idProduct**) 0xee3a.

Comme pour toute interface ouverte et standardisée, il existe un module Python associé à VISA : **PyVISA**. Nous allons donc pouvoir simplement piloter l'appareil en Python.

## 2. PYVISA

VISA pour *Virtual Instrument Software Architecture* est une bibliothèque standard poussée par **National Instruments**. Elle est téléchargeable sur le site **NI [3]**, mais pas vraiment libre. Il est beaucoup plus simple de se jeter sur la « version Python » *open source* **PyVISA [4]**.

PyVISA est un utilitaire Python permettant de piloter tout plein d'instruments, dont notre oscilloscope. Il est bien sûr disponible dans toute bonne distribution GNU/Linux à base de **Debian**.

```

$ sudo apt install python3-pyvisa python3-pyvisa-py python3-usb

```

La lectrice ou le lecteur qui chercherait à comprendre toutes les couches impliquées dans le pilotage des appareils de mesure en électronique pourra se référer à l'article de Denis Bodor **[5]**, pour que les sigles VISA, SCPI, GPIB, etc., n'aient plus de secret pour vous.

Avant de tenter une quelconque connexion à l'appareil, il est important de configurer ses règles **udev** correctement en ajoutant le fichier suivant :

```

$ sudo vim /etc/udev/rules.d/70-siglent.rules

```

Avec les identifiants USB de l'appareil vus au branchement. Dans le cas du **Siglent**, l'identifiant vendeur est 0xf4ed et 0xee3a pour le produit.

```

# SIGLENT SDS1202X-E

SUBSYSTEMS=="usb", ACTION=="add", ATTRS{idVendor}=="f4ed",

ATTRS{idProduct}=="ee3a", GROUP="usbm", MODE="0660"

```

Si le groupe **usbm** n'existe pas, on l'ajoute :

```

$ groupadd usbm

$ sudo usermod -aG usbm nomutilisateur

```

Pour que l'ajout du groupe à l'utilisateur soit effectif, il est important de se « délogger » de sa session pour se « relogger ».

Puis on recharge les règles avant de brancher l'USB de l'oscilloscope.

```

sudo udevadm control --reload

```

Pour les premiers tests, on peut lancer une console Python de type **ipython** :

```

$ ipython

In [1]: import pyvisa

In [2]: rm = pyvisa.ResourceManager()

In [3]: rm.list_resources()

Out[4]: ('USB0::62701::60986::SDS1EDEQ3R4790::0::INSTR',)

```

On retrouve l'oscilloscope dans la liste des ressources avec des identifiants vendeurs et produits en décimal.

Mais comme nous n'avons qu'un appareil de branché à l'ordinateur, il n'est pas nécessaire de se poser de question sur lequel utiliser. Pour ouvrir la ressource il suffira de passer **USB0::62701::60986::SDS1EDEQ3R4790::0::INSTR** en paramètre de la fonction **open\_resource()**.

```

In [5]: inst = rm.open_resource('USB0::62701::60986::SDS1EDEQ3R4790::0::INSTR')

In [6]: print(inst.query("*IDN?"))

Siglent Technologies, SDS1202X-E, SDS1EDEQ3R4790, 1.3.26

```

On récupère ainsi une instance **inst** sur laquelle on va effectuer des requêtes **query()** pour lire des valeurs. Pour envoyer des commandes, on utilisera la méthode **write()** avec la commande VISA à lancer.

Dans l'exemple ci-dessus, nous avons lancé une requête d'identification pour connaître le nom du constructeur, le modèle, le numéro de série ainsi que la version du *firmware* de l'oscilloscope.

Toutes les commandes VISA supportées par l'oscilloscope sont décrites dans le manuel nommé « SIGLENT Digital Oscilloscopes Remote Control Manual » et disponible gratuitement en PDF sur le site du constructeur [6].

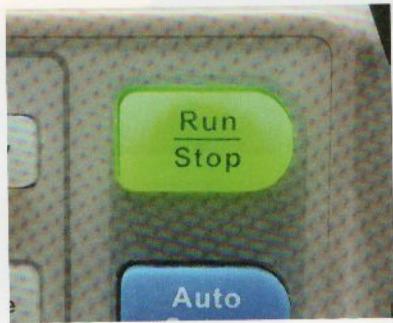

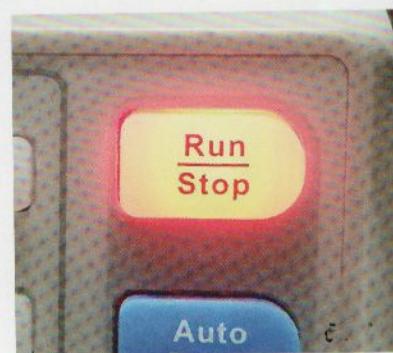

*Fig. 3 : L'oscilloscope est en mode capture automatique en continu, le bouton est vert.*

*Fig. 4 : L'oscilloscope est stoppé, le bouton est rouge.*

*Fig. 5 : Une photo de la pédale trouvée sur AliExpress avec un lien QR code pour celles et ceux qui seraient intéressés.*

On y trouve la requête **\*IDN?** qui permet de récupérer les caractéristiques d'identification de l'appareil.

On peut évidemment régler par commande Python les paramètres que l'on règle habituellement avec les boutons de l'oscilloscope. Cette manière de faire est d'ailleurs très pratique pour faire des bancs de test ou de mesure. Mais dans notre cas, nous souhaitons simplement ajouter un bouton pilotable au pied, donc nous continuerons à faire les réglages directement sur l'oscilloscope en appuyant sur le bouton **Run/Stop** pour qu'il s'affiche en vert comme on peut le voir sur la photo de la figure 3.

Une fois la capture du signal effectuée, nous souhaitons « figer » le signal en réappuyant sur ce même bouton qui fait alors office de bouton « STOP », comme en figure 4.

La documentation nous dit que si nous voulons simuler cet appui, il suffit d'écrire la commande VISA **STOP** :

```

In [7]: inst.write("STOP")

```

Et l'oscilloscope s'arrête, le bouton passe au rouge.

Nous avons compris comment piloter l'oscilloscope de manière à le faire appuyer sur le bouton **Run/Stop** et stopper l'acquisition. Passons maintenant à la deuxième partie de cette manipulation : l'interface pied-pédale.

## 3. PÉDALE USB

En traînant sur des sites asiatiques bien connus, on trouve toutes sortes de pédales qui se branchent sur l'ordinateur par USB pour une petite centaine de yuans.

Dans ce montage, nous utiliserons la pédale nommée *USB Foot Switch Single Pedal* proposée par la marque **PCSensor** sur AliExpress [7] montrée en figure 5.

Au branchement, la pédale est reconnue par le *kernel* avec le message suivant :

– Un oscilloscope à pédales –

```

[ 8261.979592] usb 1-1.3.3: new full-speed USB device number 22 using ehci-pci

[ 8262.090171] usb 1-1.3.3: New USB device found, idVendor=3553, idProduct=b001,

bcdDevice= 0.00

[ 8262.090176] usb 1-1.3.3: New USB device strings: Mfr=1, Product=2,

SerialNumber=0

[ 8262.090177] usb 1-1.3.3: Product: FootSwitch

[ 8262.090179] usb 1-1.3.3: Manufacturer: PCsensor

[ 8262.092395] input: PCsensor FootSwitch Keyboard as /devices/

pci0000:00/0000:00:1a.0/usb1/1-1/1-1.3/1-1.3.3:1.0/0003:3553:B001.0009/

input/input24

[ 8262.151777] input: PCsensor FootSwitch Mouse as /devices/

pci0000:00/0000:00:1a.0/usb1/1-1/1-1.3/1-1.3.3:1.0/0003:3553:B001.0009/

input/input25

[ 8262.151934] hid-generic 0003:3553:B001.0009: input,hidraw1: USB HID v1.11

Keyboard [PCsensor FootSwitch] on usb-0000:00:1a.0-1.3.3/input0

[ 8262.152573] input: PCsensor FootSwitch as /devices/pci0000:00/0000:00:1a.0/

usb1/1-1/1-1.3/1-1.3.3:1.1/0003:3553:B001.000A/input/input26

[ 8262.152654] hid-generic 0003:3553:B001.000A: input,hidraw2: USB HID v1.10

Device [PCsensor FootSwitch] on usb-0000:00:1a.0-1.3.3/input1

```

Linux la reconnaît directement comme un clavier et un appui sur la pédales correspond à la touche **x** d'un clavier. Nous pourrions bien sûr nous contenter de cette configuration. Cependant, la détection de l'appui d'une touche en Python nécessite l'utilisation de librairies compliquées qui ne sont pas toujours portables.

L'idée n'est pas de passer des heures à chercher la librairie idéale qui fera la capture bloquante de l'appui sur la pédales. Si on peut se contenter d'un **input()** simple de Python3, on sera content :

```

...

#Python va bloquer ici jusqu'à un appui sur x<entrée>

appuie_pedale = input("x")

inst.write("STOP")

...

```

La valeur entrée à l'appui de la pédales nous importe peu finalement. Ce qu'il nous manque par contre, c'est le caractère de fin de ligne... un appui sur la touche Entrée, quoi.

Plutôt que de correspondre à la touche **x**, il faudrait pouvoir configurer la pédales pour qu'elle appuie sur la touche Entrée, tout simplement.

Pour configurer la pédales, un CD contenant le pilote du périphérique est fourni avec le produit. Cependant :

- c'est un pilote prévu pour Windows ;

- et qui a encore un lecteur de CD-ROM accessible dans son PC « de tous les jours » ?

La flemme de sortir son lecteur CD USB du tiroir et de lire le CD-ROM pour voir un logiciel de configuration nous pousse donc naturellement à regarder comme ça vite fait sur Internet si on ne trouverait pas quelque chose.

Et en effet, on trouve un projet *open source* de configurateur de « footswitch » sur GitHub, proposé par **Radoslav Gerganov** qui fonctionne sous GNU/Linux.

```

$ git clone https://github.com/rgerganov/footswitch.git

$ cd footswitch

```

### HID (HUMAN INTERFACE DEVICE)

La classe de périphérique HID est un standard défini pour l'USB. C'est le protocole qui va permettre de piloter tout ce qui est clavier, souris, manette, joystick...

Tant que le périphérique est utilisé de manière standard comme un clavier ou une souris, nous n'avons pas à nous en soucier. Mais dès que nous avons besoin de configurations spécifiques, il faut s'intéresser au protocole. C'est l'objet du programme **footswitch** de Radoslav Gerganov.

Avant de pouvoir compiler le logiciel, il faudra s'assurer d'avoir installé la version de développement de la bibliothèque HID :

```

$ sudo apt install libhidapi-dev

$ make

$ sudo make install

```

La commande `make install` ajoute le fichier de règles udev **19-footswitch.rules** dans le répertoire **/etc/udev/rules.d**. Il sera donc nécessaire de les relire avant de rebrancher la pédale :

```

$ sudo udevadm control --reload-rules && sudo udevadm trigger

```

Le dépôt **Footswitch** comporte un répertoire **debian** qui permet de construire le paquet Debian et de l'installer proprement dans sa distribution (histoire d'éviter d'en mettre partout avec le **sudo make install**).

```

$ sudo apt install dpkg-dev cmake libhidapi-dev pkg-config devscripts equivs

$ cd debian

$ sudo mk-build-deps -i

$ dpkg-buildpackage -us -uc -b

```

- Un oscilloscope à pédale -

Une fois que la pédale est installée puis branchée, on peut la lister avec l'option **-r** :

```

$ footswitch -r

[switch 1]: unconfigured

[switch 2]: x

[switch 3]: unconfigured

```

**footswitch** détecte trois commutateurs, mais seul le 2 semble configuré. Pour changer de touche, on indiquera le numéro de *switch* à configurer et l'option **-k**.

Par exemple, si l'on veut *mapper* la lettre **a**, nous utiliserons la commande suivante :

```

$ footswitch -2 -k a

```

L'appui sur la pédale correspondra désormais à la lettre **a**. Notez que cette configuration est inscrite directement dans la mémoire de la pédale. Ça n'est pas une configuration du *driver* de l'ordinateur. La pédale est reconnue comme un clavier, donc si on la branche sur un autre ordinateur, elle affichera également **a**.

Il y a cependant un problème pour les personnes qui utilisent un *mapping* de clavier exotique (en bépo, par exemple). La lettre écrite ne correspondra pas toujours à celle qui sera *mappé* lors de l'appui sur la touche.

Dans notre cas, ça n'est pas très grave, car ce qui nous importe, c'est de pouvoir appuyer sur la touche <ENTRÉE> dont le *mapping* n'est pas très exotique, en général.

Pour demander la touche Entrée, il suffit de la nommer comme ceci :

```

$ footswitch -2 -k enter

```

Et nous gagnons une magnifique touche Entrée actionnable avec le pied.

## 4. UN PETIT SCRIPT PYTHON POUR ASSEMBLER TOUT ÇA

Maintenant que nous savons piloter l'oscilloscope et que nous avons configuré la pédale pour qu'elle corresponde à l'appui sur la touche Entrée, nous pouvons faire un petit script *quick-and-dirty* pour mettre en œuvre l'oscilloscope à pédale.

```

from usb.core import USBError ❶

import pyvisa

SERIALNUM="SDS1EDEQ3R4790"

IDVENDOR = 0xf4ed

IDPRODUCT = 0xee3a

SIGLENT_OSC_NAME = f'USB0::{IDVENDOR}::{IDPRODUCT}::{SERIALNUM}::0::INSTR'

```

```

rm = pyvisa.ResourceManager()

inst = rm.open_resource(SIGLENT_OSC_NAME) ❷

footswitch_press = input() ❸

try:

inst.query("STOP") ❹

except USBError: ❶

pass

```

On se connecte à l'oscilloscope via le **ResourceManager** et sa méthode **open\_resource()** ❷. Puis on « bloque » sur une demande de valeur entrée au clavier avec la fonction native de Python **input()** ❸. L'appui sur la touche Entrée a pour effet de passer à la ligne suivante qui est ❹ : l'envoi de la requête **STOP**.

Sur l'ordinateur de l'auteur, l'interface USB a tendance à lever fréquemment une erreur d'USB (**USBError**) alors que la requête a bien fonctionné. Il est donc nécessaire de la capturer pour l'ignorer ❶.

Pour le faire fonctionner, nous réglerons l'oscilloscope comme souhaité, puis nous lancerons le script :

```

$ python push_stop_siglent.py

```

Lorsque nous aurons la courbe voulue sur l'oscilloscope, un appui sur la pédale (donc la touche Entrée) stoppera la capture.

Bien sûr, il sera nécessaire de recommencer la manipulation à chaque fois que nous relancerons la capture sur l'oscilloscope.

Pour éviter cela et faire en sorte que le script se « réarme » automatiquement, nous pourrions le faire tourner en boucle.

```

footswitch_press = input()

while footswitch_press.strip() == '': ❶

print("STOP") ❷

try:

inst.query("STOP")

except USBError:

pass

footswitch_press = input() ❸

```

La modification se fait à la fin du script, on boucle sur la valeur tapée au clavier ❶. Si elle est vide (seulement la touche Entrée), on affiche tout de suite le mot **STOP**, histoire de voir une réaction à l'écran ❷. On envoie la requête d'arrêt, puis on se bloque à nouveau sur l'attente de la touche Entrée ❸.

## OUTILS & LOGICIELS

De cette manière, il n'est plus nécessaire de revenir à l'ordinateur pour relancer un cycle après avoir relancé l'oscilloscope. De plus, on peut quitter la boucle très simplement en entrant une valeur avant d'appuyer sur la touche Entrée de son clavier.

```

$ python push_stop_loop_siglent.py

STOP

STOP

adieux monde cruel !

$

```

Tous les codes présentés ici se trouvent sur le dépôt de l'auteur [8].

## CONCLUSION

Malgré son aspect *quick-and-dirty*, ce montage est parfaitement fonctionnel. Nous avons pu ajouter une troisième « main » (qui s'avère être un pied) à l'oscilloscope. Grâce aux interfaces (à peu près) ouvertes, nous avons pu élaborer ce *hack* de manière assez transparente.

Nous avons utilisé une pédale USB simple pour ajouter une seule fonctionnalité. Il est cependant parfaitement possible d'utiliser un pédailler USB comportant deux ou trois pédales pour décupler les possibilités de manipulation de son oscilloscope.

Le montage nécessite cependant l'utilisation d'un PC. De nos jours, les PC peuvent être de taille réduite et avec une bonne autonomie, c'est même avec un vieux pc « ultra portable » qu'a été réalisée cette manipulation. Mais il serait intéressant de réduire la taille encore avec une **Raspberry Pi**, par exemple. La Raspberry Pi possède les entrées USB nécessaires à la connexion de l'oscilloscope et de la pédale, et comme elle tourne avec des distributions GNU/Linux récentes, il n'y a pas de problème de portage.

La Raspberry Pi est tout de même un ordinateur assez puissant qui se rapproche d'un ordinateur de bureautique. Ça reste cher pour l'ajout d'une simple touche à son oscilloscope. Surtout si on le dédit à cette fonctionnalité.

Pour réduire encore les coûts, on pourra aller voir du côté des SBC (*Single Board Computer*) chinois comme le **Milk-Duo** présenté par Denis Bodor dans le Hackable 54 [9]. Le temps d'intégration des *drivers* et la mise en place d'un programme seront sans doute un peu plus longs que sur un PC avec Python, mais nous restons sur un système GNU/Linux avec de l'USB. Si la partie USB complexifie le développement, on peut même passer par l'Ethernet de l'oscilloscope et une pédale sans USB (simple commutateur).

L'ultime simplification (côté utilisateur) consisterait à brancher la pédale USB directement sur l'oscilloscope, puisque l'appareil utilisé dans cet article possède une entrée USB « host » pour y brancher des clefs USB de stockage pour faire des saisies d'écran. Peut-être serait-il possible d'y brancher un autre périphérique USB ?

– Un oscilloscope à pédales –

Cette option nécessite par contre de « hacker » (dans le sens noble du terme) l'oscilloscope de manière à adapter le comportement de la prise USB. Et ça tombe bien, quelqu'un l'a fait avec le projet **360nosc0pe** [10]. L'électronique qui constitue l'oscilloscope de Siglent est en fait **Zynq** de chez **AMD/Xilinx**. Le Zynq est un SoC (*System On Chip*) muni d'une partie processeur (ARM Cortex-A9) et d'une partie FPGA (Artix 7). Le projet 360nosc0pe utilise le langage de description matériel nommé Migen/Litex basé sur du Python et promu par l'entreprise française **Enjoy Digital**. Comme tout le code du projet est fourni, il doit être possible de l'adapter pour piloter une pédale USB, et le piloter ainsi en direct !

Attention, en utilisant ainsi une pédale pour faire de l'électronique quotidiennement, vous risquez d'y prendre goût. Mais sachez que pour satisfaire votre dépendance, il est possible de décupler son usage en vous déplaçant à vélo et ainsi venir grossir les rangs des « vélotaffeuses » et « vélotaffeurs » qui commutent quotidiennement et font leur sport réglementaire pour se maintenir en

forme. Et si les rues et routes de votre région sont encore dangereuses, n'hésitez pas à rejoindre l'une des nombreuses associations de défense du vélo comme le **CADRes de Colmar et environs** [11], dans le cas de la ville de la rédaction du magazine. **FM**

## RÉFÉRENCES

- [1] Automatisez vos mesures en utilisant l'USB, Vioix, Jean-Baptiste, Hackable 24 (mai 2018), <https://connect.ed-diamond.com/Hackable/hk-024/automatisez-vos-mesures-en-utilisant-l-usb>

- [2] Reverse-engineering d'une alimentation numérique et contrôle avec bash, Guidon, Yann, Hackable 32 (janvier 2020), <https://connect.ed-diamond.com/Hackable/hk-032/reverse-engineering-d-une-alimentation-numerique-et-controle-avec-bash>

- [3] National Instruments, <https://www.ni.com/fr/support/downloads/drivers/download.ni-visa.html>

- [4] PyVISA, <https://pypi.org/project/PyVISA/>

- [5] Contrôlez votre alimentation de laboratoire avec votre Raspberry Pi, Bodor, Denis, Hackable 15 (novembre 2016), <https://connect.ed-diamond.com/Hackable/hk-015/controlez-votre-alimentation-de-laboratoire-avec-votre-raspberry-pi>

- [6] Siglent Remote Control Manual, [https://int.siglent.com/upload\\_file/user/SDS1000X+/SIGLENT\\_Digital\\_Oscilloscopes\\_Remote\\_Control\\_Manual.pdf](https://int.siglent.com/upload_file/user/SDS1000X+/SIGLENT_Digital_Oscilloscopes_Remote_Control_Manual.pdf)

- [7] Foot Switch FS221-P, PCSensor, <https://fr.aliexpress.com/item/1005006279064716.html>

- [8] Dépôt du code de l'article, <https://github.com/Martoni/OscilloPedale.git>

- [9] Milk-V Duo : un minuscule SBC RISC-V à 8 €, Bodor, Denis, Hackable 54 (mai 2024), <https://connect.ed-diamond.com/hackable/hk-054/milk-v-duo-un-minuscule-sbc-risc-v-a-8-eu>

- [10] 360nosc0pe, <https://github.com/360nosc0pe/scope>

- [11] Cyclistes Associés pour le Droit de Rouler en sécurité Colmar et environs, <http://www.cadrescolmar.org>

# CONCEVOIR, METTRE EN PLACE ET BIDOUILLER UN ENVIRONNEMENT BASÉ SUR LE PROTOCOLE INDUSTRIEL MODBUS

Erwan Cordier

Dans cet article, nous allons étudier et mettre en place un environnement de système industriel. Nous utiliserons des outils open source et le protocole de référence Modbus TCP. D'abord, nous allons observer le fonctionnement du protocole, ensuite nous mettrons en place un environnement de test pour comprendre comment détourner le comportement normal d'un microcontrôleur pour provoquer des malfonctions. Bien que largement couvert par d'autres articles des éditions Diamond et malgré son âge avancé (1<sup>re</sup> version en 1979), le protocole Modbus TCP est toujours d'actualité et reste utilisé sous plusieurs formes pour gérer des microcontrôleurs industriels (PLC) actuellement sur le marché.

- Concevoir, mettre en place et bidouiller un environnement basé sur le protocole industriel Modbus -

**N**ous allons proposer ici la mise en place d'un environnement qui exploite pleinement Modbus TCP pour que vous puissiez l'implémenter et expérimenter directement. Veuillez noter que l'objectif de cet article est de permettre une compréhension et l'exploitation du protocole et de son environnement, mais nous ne couvrirons pas la partie automatisation et développement des automates (Ladder Logic, Graphset, etc.).

## 1. INTRODUCTION

### 1.1 Historique et présentation du protocole Modbus

Pour une introduction plus complète du protocole, je me permets de citer celle proposée dans les lignes du *GNU/Linux Magazine* n°208 concernant le protocole Modbus [1].

Créé en 1979 par Modicon, Modbus est un protocole de communication industriel, utilisé initialement pour communiquer avec des automates programmables, il se décline sous deux versions :

- Modbus RTU ou Modbus ASCII pour les lignes séries ;

- Modbus TCP pour l'Ethernet.

Il fonctionne sur la logique de maître-esclave. Les esclaves sont totalement passifs et seul le maître peut initier un échange

de données, selon une logique reposant sur le principe de la question/réponse. Ce protocole est principalement utilisé dans les réseaux d'automates programmables. Ce protocole facile à utiliser, implémenter et robuste est devenu un protocole industriel de référence, surtout depuis son encapsulation dans les trames Ethernet.

Dans cet article, toutes les références au protocole Modbus feront référence au protocole Modbus TCP, Modbus RTU n'est pas abordé ici.

### 1.2 Recherche et structure protocolaire

Le protocole Modbus, par son ancienneté, a été largement documenté et modifié pour satisfaire des demandes sur mesure, par exemple, le protocole UMAS de Schneider Electric se sert de Modbus comme base pour son propre protocole.

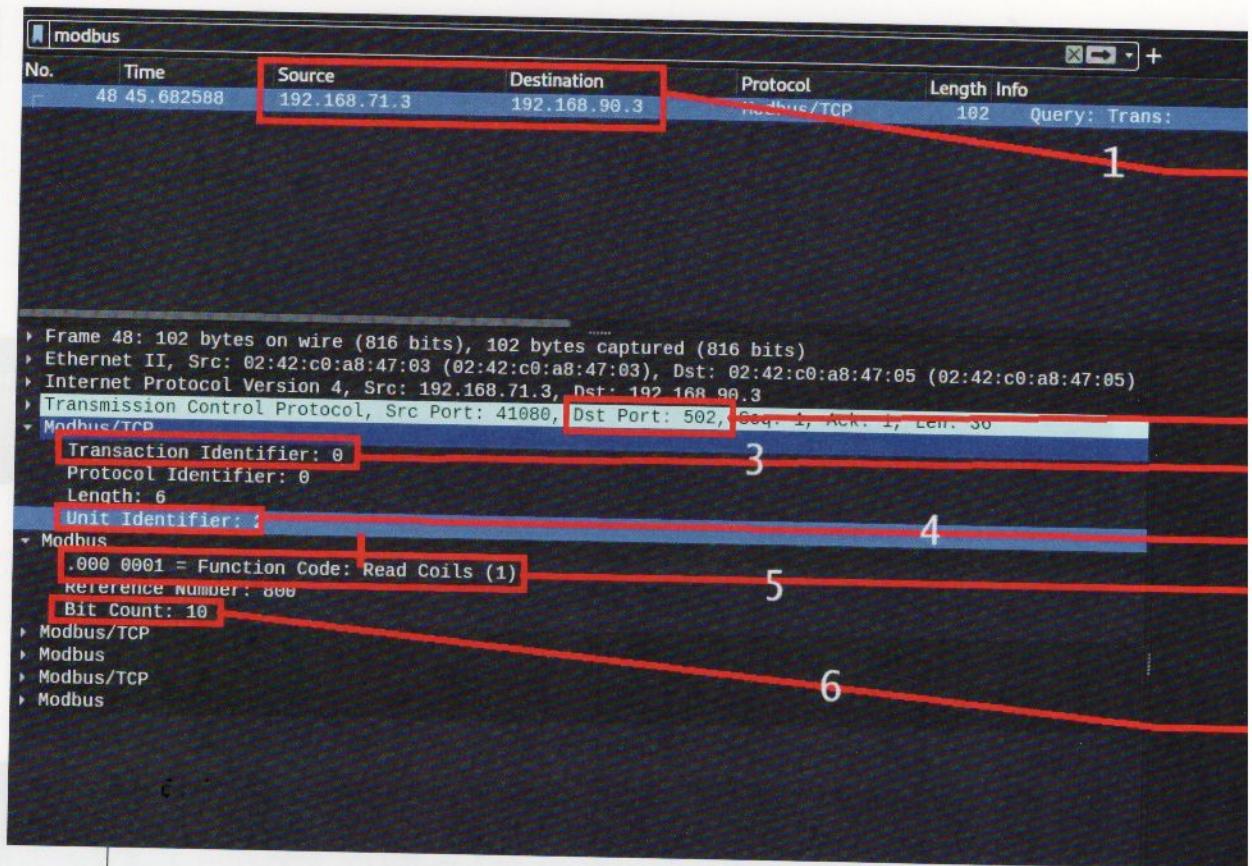

#### 1.2.1 Structure protocolaire

La structure protocolaire de Modbus est volontairement simpliste.

Les exemples sont tirés de l'IETF [draft-dude-modbus-applproto-00.txt](#) pour une compréhension complète du protocole et de chaque code de fonction. Nous vous recommandons cette lecture.

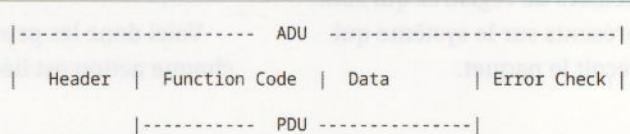

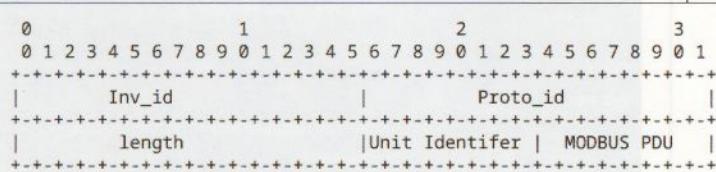

Un paquet Modbus TCP se structure de la manière suivante :

Le protocole est basé sur une pile TCP/IP. La section Modbus se trouve dans la partie TCP et est envoyée sur le port 502 (qui est le port dédié pour Modbus).

#### 1.2.1.1 MODBUS ADU : EN-TÊTE

L'en-tête a une longueur de 7 octets et comprend les champs suivants :

- L'Inv ID (2 octets) est utilisé pour définir une paire (une forme de signature pour associer une requête et une réponse) ;

- L'ID du protocole (2 octets) est toujours 0 pour les services Modbus (un ID qui n'est pas zéro peut être lié à une extension du protocole) ;

- La taille (2 octets) correspond à la somme du champ UID additionné à la taille du PDU ;

- L'ID unitaire (1 octet) ou UID est utilisé pour identifier un serveur distant situé sur un réseau non TCP.

### 1.2.1.2 MODBUS PDU : TYPE DE DONNÉES, CODE DE FONCTION

Modbus base son modèle de données sur une série de fichiers de registres qui sont présents sur le système qui reçoit le paquet.

Il y a deux catégories de modèle de données :

- les *coils* (valeur booléenne 1 bit) ;

- les registres (valeur hexadécimale 16 bits) ;

Les *coils*, par exemple, peuvent être utilisés pour définir ou retourner l'état d'un interrupteur, quand les registres peuvent définir ou retourner l'état d'une unité de mesure (L, M/s, Pa). Nous parlons ici de « définir » et de « retourner » puisqu'il y a un concept d'écriture et de lecture dans la construction d'une trame Modbus qui doit être pris en compte.

Les systèmes *Input/Output* (I/O = valeur physique) n'acceptent que la lecture, quand les données d'applications acceptent la lecture/écriture.

La suite est assez logique. Nous pouvons faire deux types d'actions, lire ou écrire sur un ou plusieurs *coils* ou registres (en comptant une restriction en lecture seule sur les I/O).

Je vous affiche ici 4 possibilités de codes fonctions.

- Écriture ou lecture :

→ *Discrete Output (Coils)* || *data from application*

→ *Holding Registers* || *data from application*

- Lecture seule :

→ *Discrete Input (Coil)* || *data from I/O system*

→ *Input Register (Register)* || *data from I/O system*

Voici donc les principales actions que nous pouvons faire, chaque action est liée à son code de fonction.

### Public function codes [ edit ]

|             |               | Function type                                   | Function name                    | Function code |

|-------------|---------------|-------------------------------------------------|----------------------------------|---------------|

| Data Access | Bit access    | Physical Discrete Inputs                        | Read Discrete Inputs             | 2             |

|             |               | Internal Bits or Physical Coils                 | Read Coils                       | 1             |

| Data Access | 16-bit access | Physical Input Registers                        | Write Single Coil                | 5             |

|             |               | Internal Registers or Physical Output Registers | Write Multiple Coils             | 15            |

| Data Access | 16-bit access | Physical Input Registers                        | Read Input Registers             | 4             |

|             |               | Internal Registers or Physical Output Registers | Read Multiple Holding Registers  | 3             |

| Data Access | 16-bit access | Physical Input Registers                        | Write Single Holding Register    | 6             |

|             |               | Internal Registers or Physical Output Registers | Write Multiple Holding Registers | 16            |

| Data Access | 16-bit access | Physical Input Registers                        | Read/Write Multiple Registers    | 23            |

|             |               | Internal Registers or Physical Output Registers |                                  |               |

# Modbus

- Concevoir, mettre en place et bidouiller un environnement basé sur le protocole industriel Modbus –

Pour les codes de fonctions demandant la lecture ou l'écriture de plusieurs éléments, la partie Modbus PDU est définie via une adresse de base (*start adresse*) suivie d'une valeur *n* (*quantity*) qui va être additionnée à une valeur de base. Donc, si vous voulez lire deux registres qui ne sont pas successifs, il faut faire plusieurs requêtes, là où deux registres successifs peuvent être requêtés en un seul.

## 1.2.2 Recherche documentaire

Dans la suite de cet article, nous allons nous poser en attaquants ayant une volonté de destruction matérielle.

La compréhension du protocole est très importante, cependant si nous voulons uniquement modifier l'état d'un bouton, il nous faut juste le code de fonction qui permet de modifier un *coil*. La même logique peut être appliquée à tous les autres protocoles : si je veux récupérer le contenu d'une page HTML, je vais utiliser le paramètre GET. La difficulté est de comprendre un paquet qui a une fonction qui n'est pas présente dans une quelconque documentation officielle.

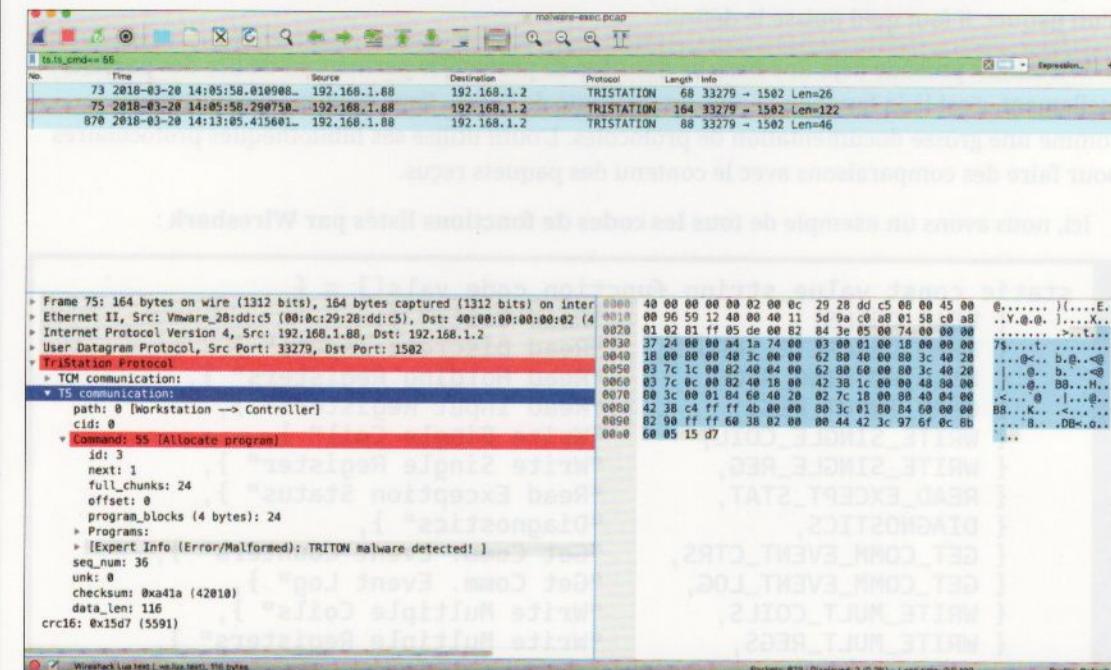

Néanmoins, il existe quelques chemins de traverse pour trouver votre bonheur (sauf si vous êtes le premier ou un des seuls à travailler sur ce protocole). Dans les deux exemples que nous allons traiter, nous allons nous servir de l'outil Wireshark et de son dissecteur de trames intégré.

### 1.2.2.1 DISSECTEUR WIRESHARK INTÉGRÉ

Wireshark est un outil très connu disponible sur GitHub et sur GitLab maintenu par la Wireshark Fondation. Il est sous licence GNU GPL, il est donc *open source*. Un des concepts de base de Wireshark est la dissection de paquets qu'il reçoit sur une interface définie. Mais, pour qu'il puisse identifier quel protocole est employé et comment séparer les différents éléments d'un paquet, il faut qu'il puisse le définir.

Wireshark possède déjà une base de données de protocoles permettant de lire des paquets facilement, c'est là la fonction la plus intéressante de l'outil. Vous pouvez voir Wireshark comme une grosse documentation de protocoles. L'outil utilise ses bibliothèques protocolaires pour faire des comparaisons avec le contenu des paquets reçus.

Ici, nous avons un exemple de **tous les codes de fonctions listés par Wireshark** :

```

static const value_string function_code_vals[] = {

{ READ_COILS, "Read Coils" },

{ READ_DISCRETE_INPUTS, "Read Discrete Inputs" },

{ READ_HOLDING_REGS, "Read Holding Registers" },

{ READ_INPUT_REGS, "Read Input Registers" },

{ WRITE_SINGLE_COIL, "Write Single Coil" },

{ WRITE_SINGLE_REG, "Write Single Register" },

{ READ_EXCEPT_STAT, "Read Exception Status" },

{ DIAGNOSTICS, "Diagnostics" },

{ GET_COMM_EVENT_CTRS, "Get Comm. Event Counters" },

{ GET_COMM_EVENT_LOG, "Get Comm. Event Log" },

{ WRITE_MULT_COILS, "Write Multiple Coils" },

{ WRITE_MULT_REGS, "Write Multiple Registers" },

```

# SÉCURITÉ

Sur cette page, nous allons voir comment déboguer un malware avec Wireshark et comment l'analyser avec un disassembleur.

```

{ REPORT_SLAVE_ID,           "Report Slave ID" },

{ READ_FILE_RECORD,          "Read File Record" },

{ WRITE_FILE_RECORD,          "Write File Record" },

{ MASK_WRITE_REG,            "Mask Write Register" },

{ READ_WRITE_REG,             "Read Write Register" },

{ READ_FIFO_QUEUE,            "Read FIFO Queue" },

{ ENCAP_INTERFACE_TRANSP,     "Encapsulated Interface Transport" },

{ UNITY_SCHNEIDER,            "Unity (Schneider)" },

{ 0,                            NULL }

```

Ce qui est intéressant ici est la centralisation de l'information. Un élément supplémentaire que je trouve pertinent est le fait qu'un code de fonction nommé **UNITY\_SCHNEIDER** est présent, alors qu'il n'est ni défini dans la page Wikipédia ni dans l'IETF listée plus haut. On peut donc tomber sur des éléments non documentés, mais approuvés par au moins deux personnes (le créateur du disasecteur et la fondation Wireshark).

## 1.2.2.2 DISSECTEUR WIRESHARK COMMUNAUTAIRE

Dans certains cas (un à ma connaissance), il arrive qu'un protocole ne soit pas documenté de manière publique et que Wireshark n'intègre pas dans sa version de base le dissecteur officiel pour ce dernier. Dans ces cas-là, vous pouvez (en général) compter sur la communauté Wireshark.

En effet, en plus de son moteur en C, Wireshark intègre un moteur de *scripting* de dissection formulable en **Lua** (langage de *scripting*), fait pour le développement de dissecteur sur mesure. Ce système est assez facile à prendre en main et fonctionne en dépliant au fur et à mesure le

# Modbus

– Concevoir, mettre en place et bidouiller un environnement basé sur le protocole industriel Modbus –

paquet. Les cas d'usage sont assez variés et ne se résument pas uniquement à la définition de protocoles réseau, il peut aussi avoir des cas d'usage de décodages différents sur certains champs de données, ou de la détection de certains comportements malicieux.

Grâce à ce moteur, n'importe qui peut ajouter son propre dissecteur. Et en général, la communauté distribue ces dissecteurs librement sur GitHub et sur GitLab.

Par exemple, il y a quelques années l'entreprise Nozomi Networks avait développé un **dissecteur Wireshark** pour détecter le *malware TRITON*, qui se spécialisait dans l'attaque des systèmes de contrôle industriels.

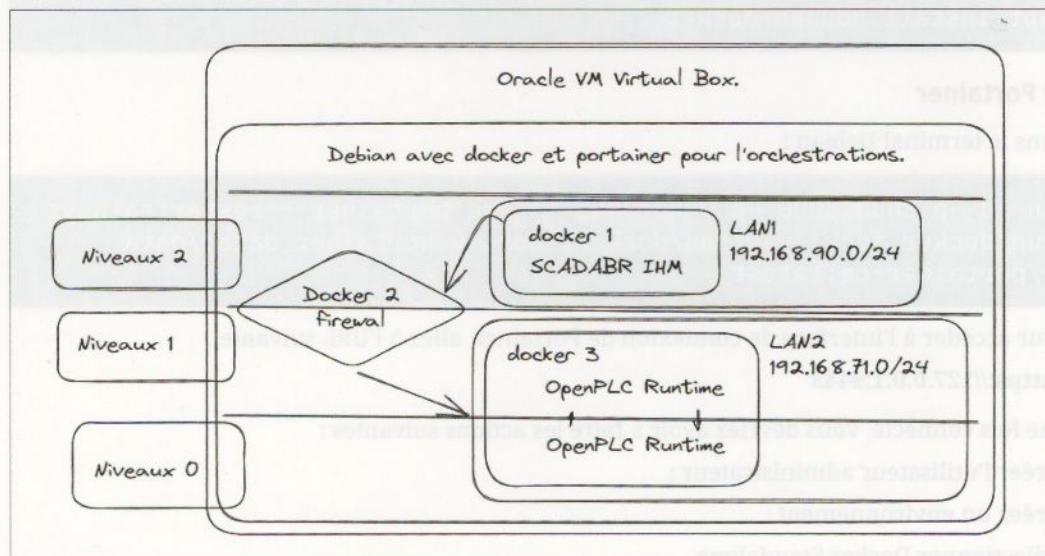

## 2. ENVIRONNEMENT, SEGMENTATION RÉSEAU ET LOGICIELLE

Maintenant les bases du protocole Modbus comprises, attardons-nous sur l'environnement dans lequel va évoluer ce protocole. L'objectif est de simuler un environnement de technologie opérationnel.

Les exigences suivantes sont obligatoires au bon fonctionnement d'un environnement OT :

- exigences en matière de délais et de performances ;

- exigence de disponibilité.

Les environnements ne sont pas les mêmes entre l'IT et l'OT. C'est pour cela que la segmentation est une préparation d'une architecture réseau nécessaire, cela nous amène donc au prochain point.

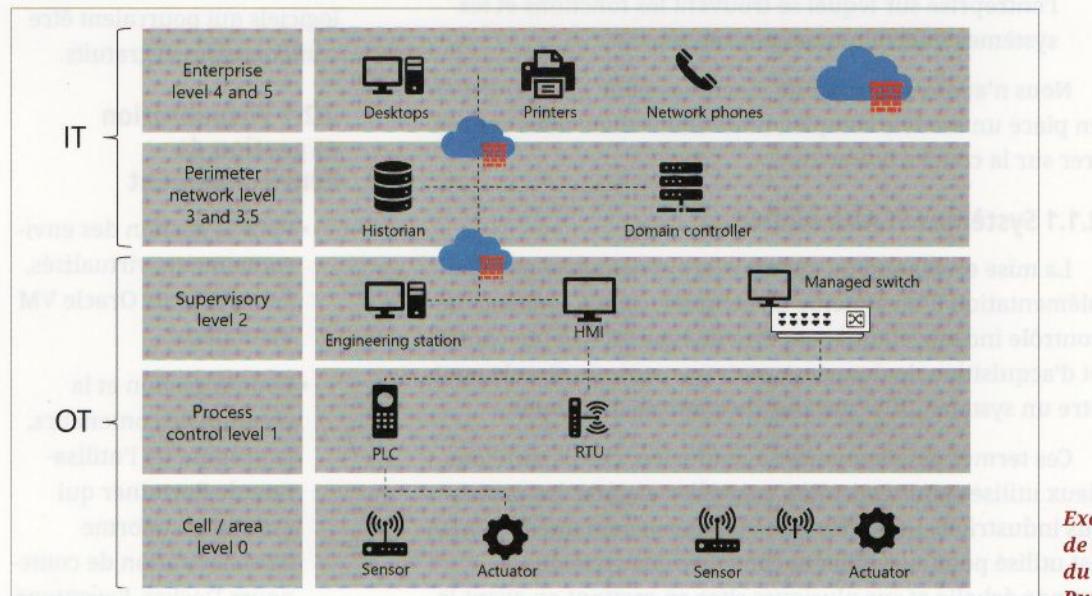

### 2.1 Modèle de Purdue

Le modèle de référence **Purdue** est un modèle de segmentation des réseaux de systèmes de contrôle industriels (ICS)/OT qui définit six couches, composants et contrôles de sécurité pertinents pour ces réseaux.

Exemple d'écran de représentations du modèle de Purdue.

- Niveau 0, cellule et zone :

Le niveau 0 est constitué d'un large éventail de capteurs, d'actionneurs et de dispositifs impliqués dans le processus de fabrication de base.

- Niveau 1, contrôle du processus :

Le niveau 1 comprend des contrôleurs intégrés qui contrôlent et manipulent le processus de fabrication et dont la fonction principale est de communiquer avec les dispositifs de niveau 0.

- Niveau 2, supervision :

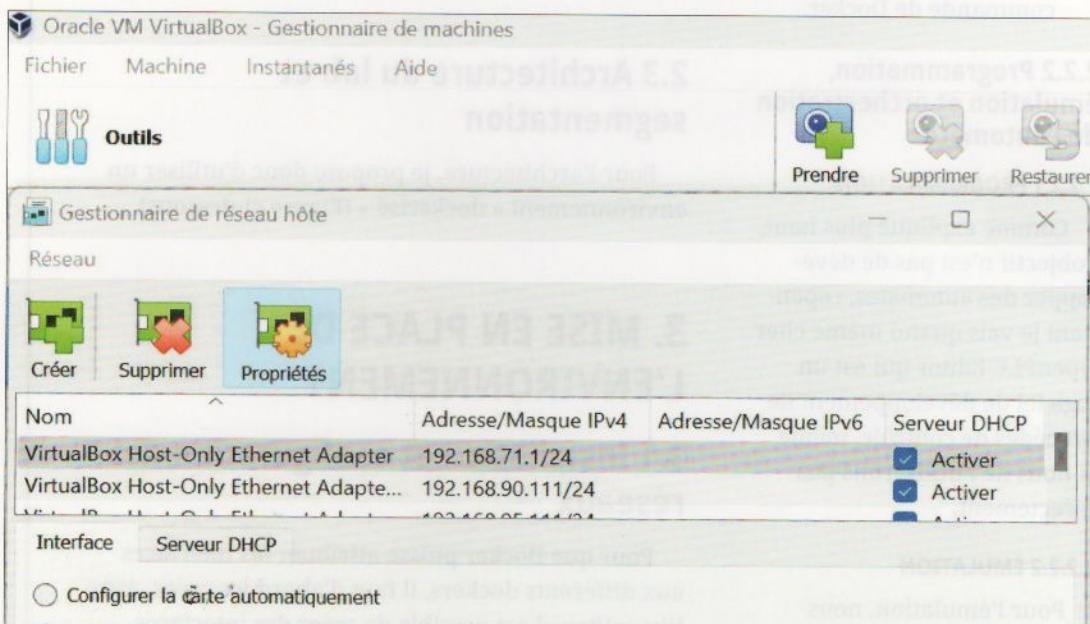

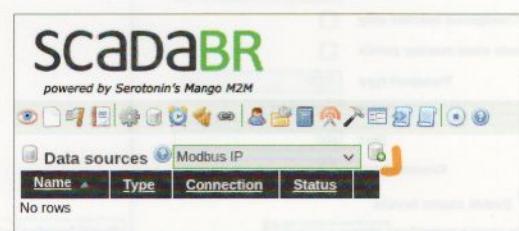

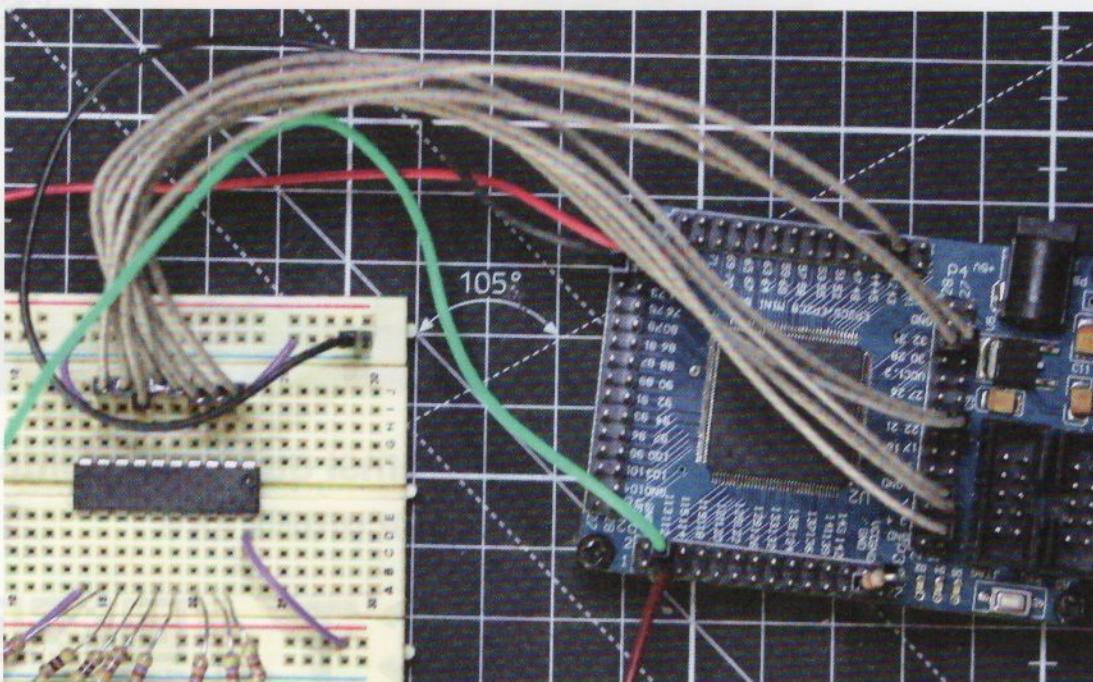

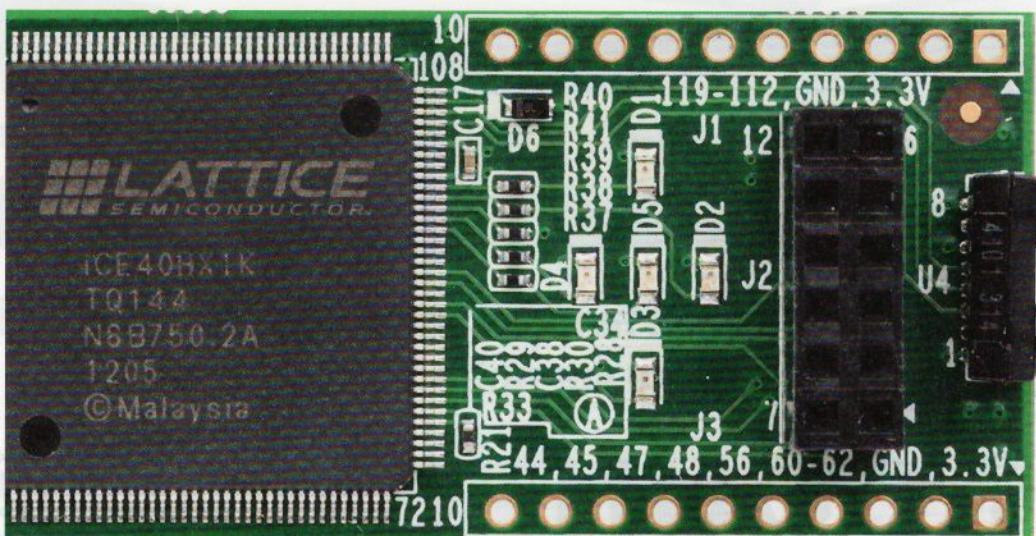

Le niveau 2 représente les systèmes et fonctions associés à la supervision et à l'exploitation du *runtime* d'une zone d'une installation de production (interface homme-machine).