ÉLECTRONIQUE | EMBARQUÉ | RADIO | IOT

# HACKABLE

L'EMBARQUÉ À SA SOURCE

N° 56

SEPTEMBRE / OCTOBRE 2024

FRANCE MÉTRO : 14,90 €

BELUX : 15,90 € - CH : 23,90 CHF ESP/IT/PORT-CONT : 14,90 €

DOM/S : 14,90 € - TUN : 35,60 TND - MAR : 165 MAD - CAN : 24,99 \$CAD

L 19338 - 56 - F: 14,90 € - RD

CPPAP : K92470

## REVERSE / ALIMENTATION

Analysons le protocole de l'ALIENTEK DP100 et écrivons notre propre outil de contrôle p.04

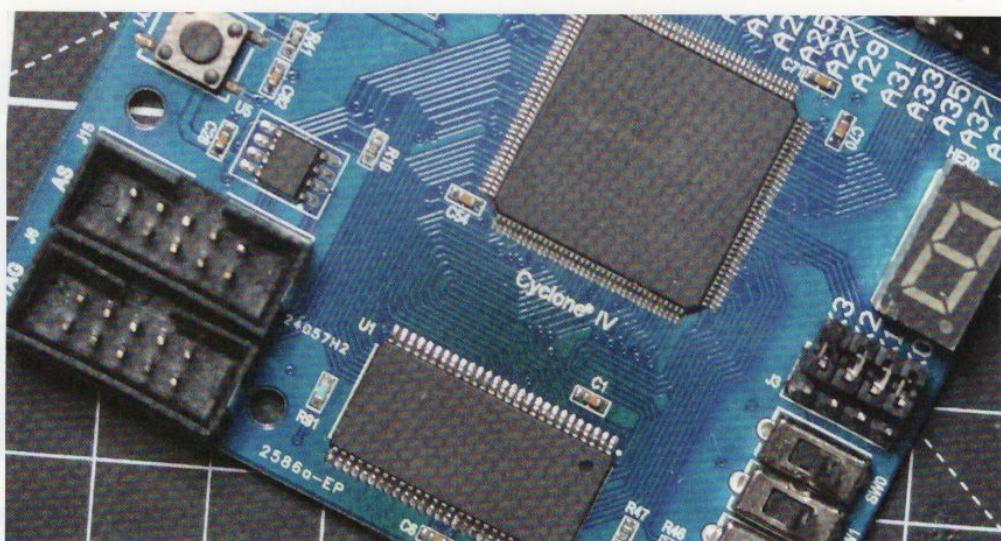

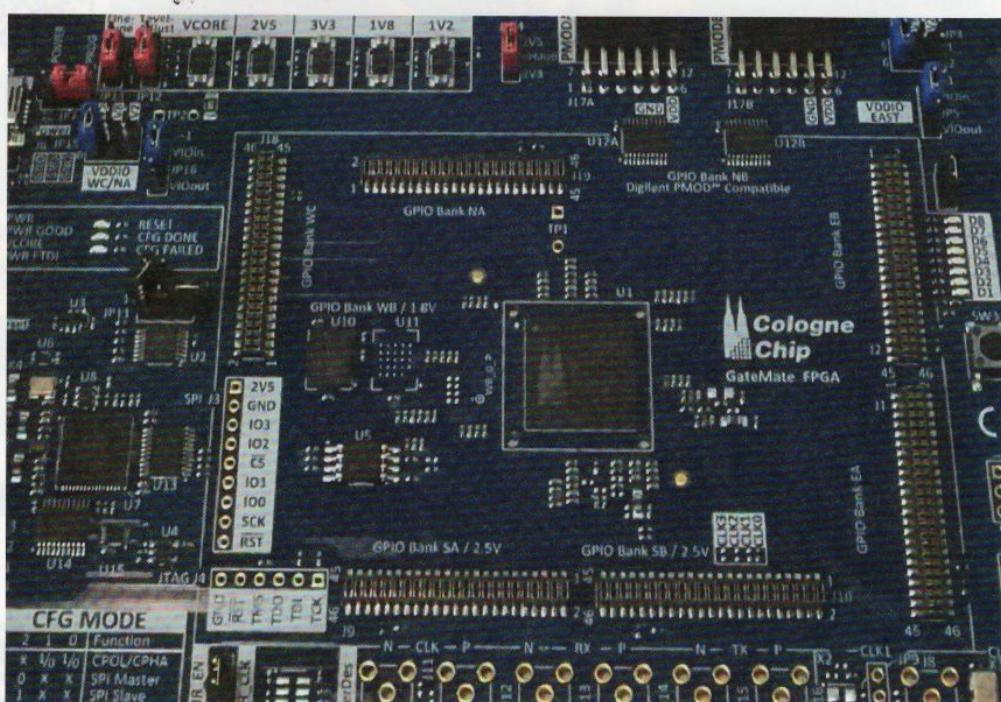

## VHDL / SDRAM / Z80

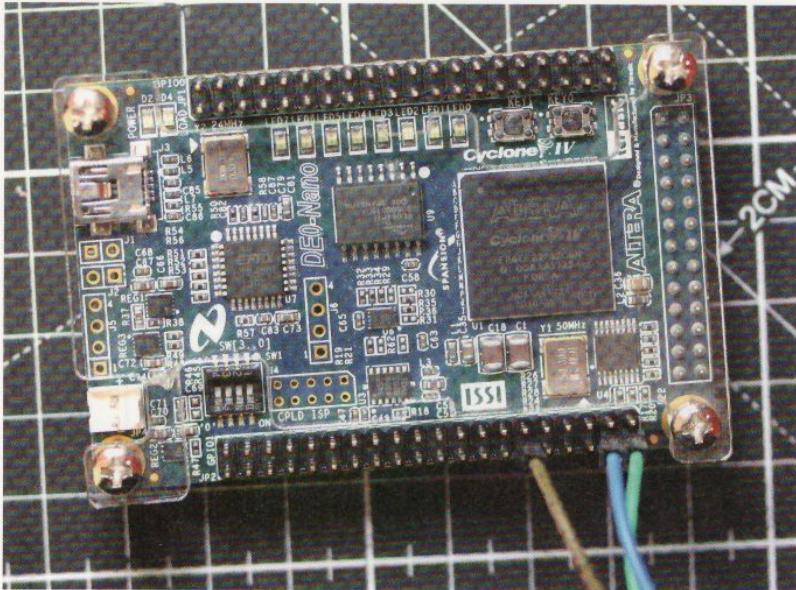

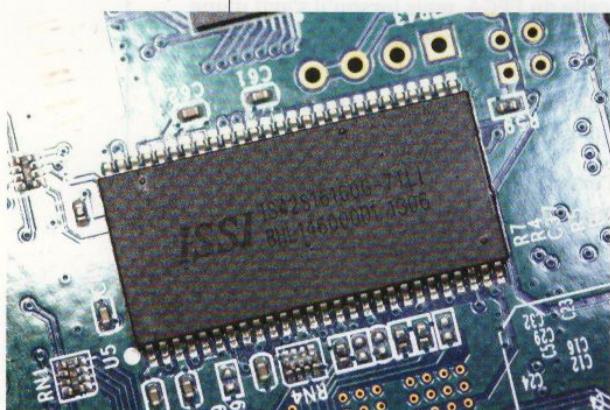

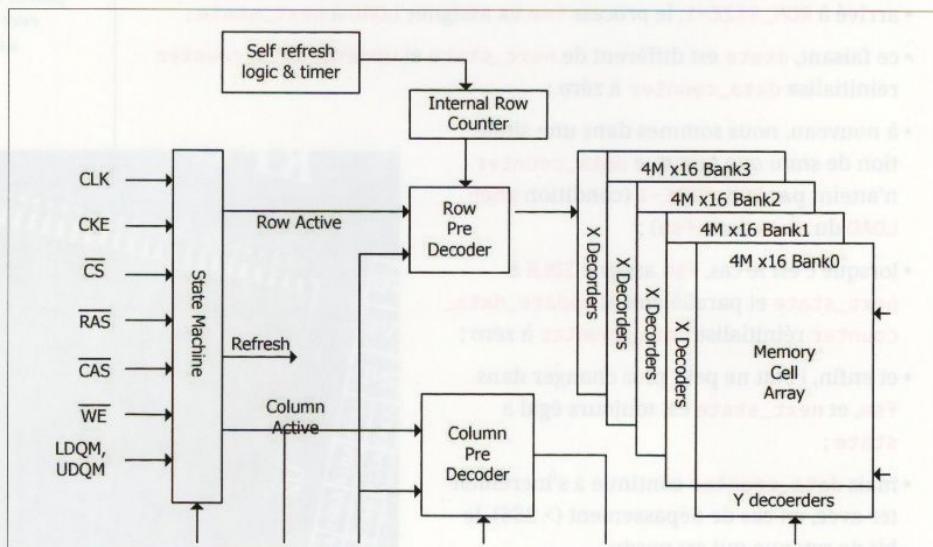

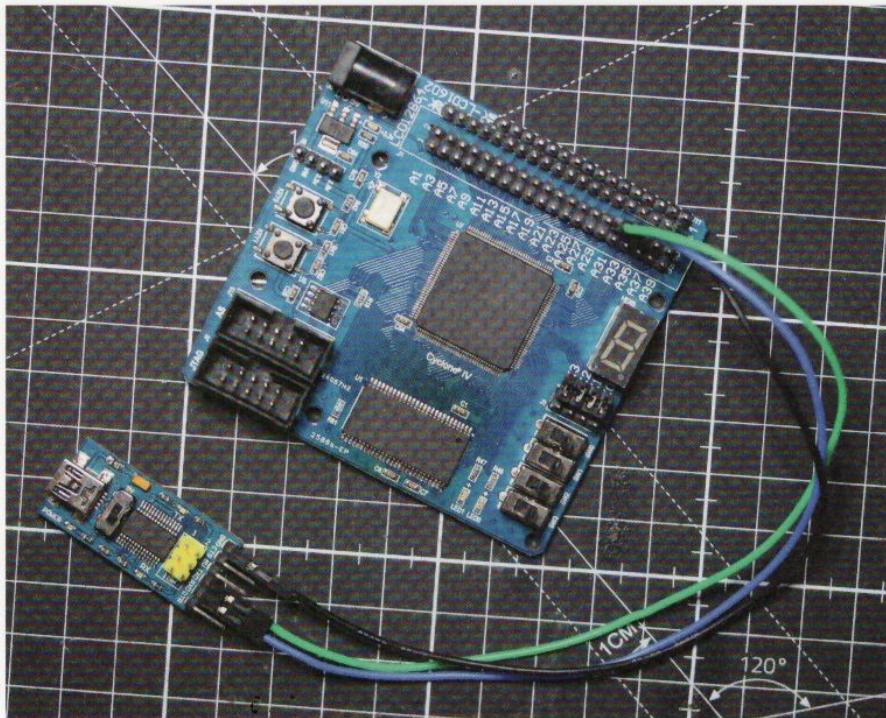

Apprenez à utiliser la SDRAM des kits de développement FPGA pour booster vos projets p.46

## AUTHENTIFICATION / FIDO2 / FIDO U2F

# PROTÉGEZ-VOUS CONTRE L'USURPATION D'IDENTITÉ !

Créez votre Passkey avec une Raspberry Pi Pico ! p.36

- Comprendre le jargon

- Construire et adapter le firmware

- Utiliser et gérer votre Passkey pour sécuriser vos comptes web

## RP2040 / USB

Maîtrisez TinyUSB sur Raspberry Pi Pico et créez votre tout premier périphérique USB p.16

## SDR / CPU / GPU

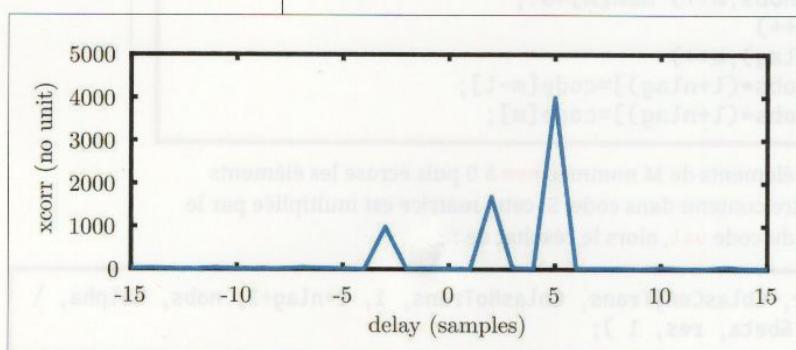

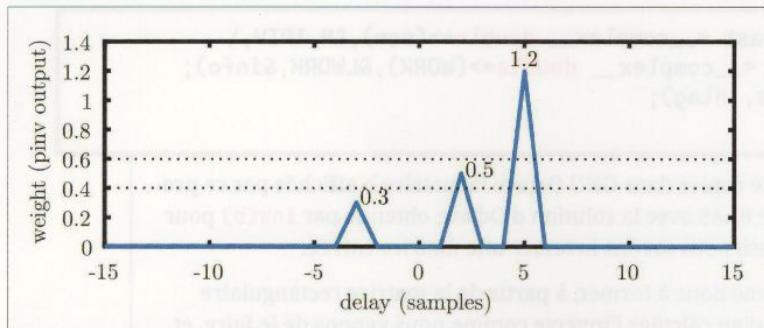

Exploration pratique des solutions de calcul linéaire pour le traitement de signaux radio p.88

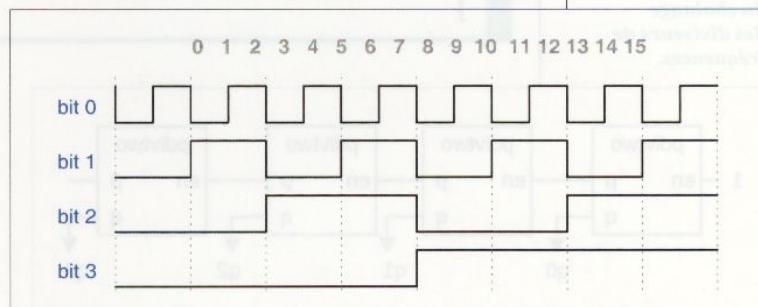

## FPGA / COMPTEURS

Optimisons un compteur HDL et comparons ses performances sur différents modèles de FPGA p.64

ÉDITION

**#4**

**OPEN SOURCEZ

VOS SOLUTIONS IT**

# OPEN SOURCE EXPERIENCE

**PARIS**

**04 & 05

DÉCEMBRE 2024**

- PALAIS

DES CONGRÈS

**90 EXPOSANTS 100 CONFÉRENCES 125 SPEAKERS**

[www.opensource-experience.com](http://www.opensource-experience.com)

Suivez-nous       #OSXP2024

Un événement  organisé par

NOUVEAU

CETTE ANNÉE !

Aux mêmes dates

et lieu que

**DEVOPS REX**

LA CONFÉRENCE DEVOPS

FRANCOPHONE

100% retour d'expérience

# ÉDITO

## Le problème de RISC-V...

Comme vous le savez sans doute, RISC-V (RISC « five ») est une ISA, ou architecture de jeu d'instructions, ouverte et libre, issue de l'UC Berkeley (encore et toujours eux) permettant aux constructeurs d'implémenter leurs processeurs sans avoir à payer des droits, comme c'est le cas pour ARM, par exemple.

De plus en plus de SoC, de MCU et de processeurs RISC-V sont conçus, produits, distribués et intégrés à des cartes et devkits. SiFive, Espressif,

Allwinner, StarFive, Nvidia... sont autant de noms qui reviennent lorsqu'on parle de cette alternative au duo x86/ARM. Et la sélection de SBC relativement économiques commence à s'étoffer très sérieusement, tout comme la gamme de systèmes utilisables sur ces plateformes ou d'outils de développement compatibles.

Comme il s'agit surtout de SoC et de SBC, la dépendance entre carte et système est très forte et c'est là, entre autres, que le bât blesse. Chaque constructeur y va de sa petite version maison de GNU/Linux, tantôt avec des contributions *upstream*, mais le plus souvent oubliée dès qu'une nouvelle carte, plus puissante et plus rapide, est mise en vente.

C'est encore plus clairement visible avec des systèmes/projets comme OpenBSD, FreeBSD et NetBSD, pour qui choisir une ou plusieurs plateformes de référence est impossible. À peine une carte est-elle supportée qu'elle devient obsolète et se voit remplacée par sa grande soeur, et le cycle recommence. Ceci est moins appa<sup>ffent</sup> pour GNU/Linux, car c'est généralement le constructeur qui publie au moins une version du système, mais est tout aussi vrai. Il n'y a presque jamais de mise à jour, passé cette version initiale, parfois incomplète.

Ce qu'il manque, c'est une « Raspberry Pi du RISC-V ». Je n'ai pas dit « Raspberry Pi avec un RISC-V », car peu importe qui sera le porte-étandard, du moment qu'il existe et assure la pérennité des développements. Mais oui, une Pi avec un RISC-V, même à un seul cœur et avec 1 Gio de RAM, à moins de 70 € serait vraiment très efficace...

Denis Bodor

## Hackable Magazine

est édité par Les Éditions Diamond

BP 20142 - 67602 SELESTAT CEDEX - France

E-mail : [lecteurs@hackable.fr](mailto:lecteurs@hackable.fr)

Service commercial : [cial@ed-diamond.com](mailto:cial@ed-diamond.com)

Sites : [hackable.fr](http://hackable.fr) - [ed-diamond.com](http://ed-diamond.com)

Directeur de publication : Arnaud Metzler

Rédacteur en chef : Denis Bodor

Réalisation graphique : Kathrin Scali

Régie publicitaire :

Valérie Fréchard - Tél. : 03 67 10 00 27

Service abonnement : Les Éditions Diamond

BP 20142 - 67602 SELESTAT CEDEX, France, Tél. : 03 67 10 00 20

Impression : Westermann Druck | PVA,

Braunschweig, Allemagne

Distribution France :

(uniquement pour les dépositaires de presse)

MLP Réassort : Plate-forme de Saint-Barthélemy-d'Anjou. Tél. : 02 41 27 53 12

Plate-forme de Saint-Quentin-Fallavier.

Tél. : 04 74 82 63 04

Service des ventes :

Abomarque - Tél. : 06 15 46 15 88

IMPRIMÉ en Allemagne - PRINTED in Germany

Dépôt légal : À partur

N° ISSN : 2427-4631

CPAP : K92470

Périodicité : bimestriel - Prix de vente : 14,90 €

La rédaction n'est pas responsable des textes, illustrations et photos qui lui sont communiqués par leurs auteurs. La reproduction totale ou partielle des articles publiés dans Hackable Magazine est interdite sans accord écrit de la société Les Éditions Diamond. Sauf accord particulier, les manuscrits, photos et dessins adressés à Hackable Magazine, publiés ou non, ne sont ni rendus, ni renvoyés. Les indications de prix et d'adresses figurant dans les pages rédactionnelles sont données à titre d'information, sans aucun but publicitaire. Toutes les marques citées dans ce numéro sont déposées par leur propriétaire respectif. Tous les logos représentés dans le magazine sont la propriété de leur ayant droit respectif.

Suivez-nous sur Twitter

## SOMMAIRE

### HACK & UPCYCLING

- 04** Alimentation DP100 : creusons un peu...

### MICROCONTROLEURS & ARDUINO

- 16** Créez vos périphériques USB avec Raspberry Pi Pico

### SÉCURITÉ

- 36** Une Raspberry Pi Pico pour remplacer vos mots de passe

### FPGA & GATEWARE

- 46** Z80 dans un FPGA : vers l'utilisation de SDRAM

- 64** Pimp my LED counter, un compteur ultrarapide

### RADIO & FREQUENCES

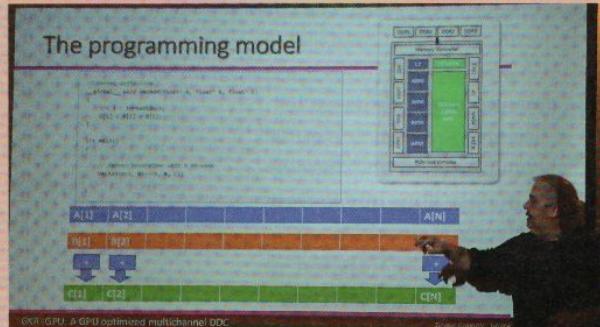

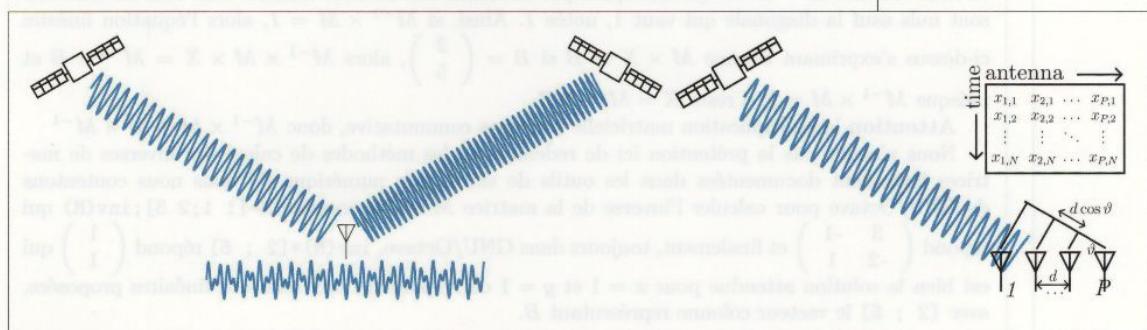

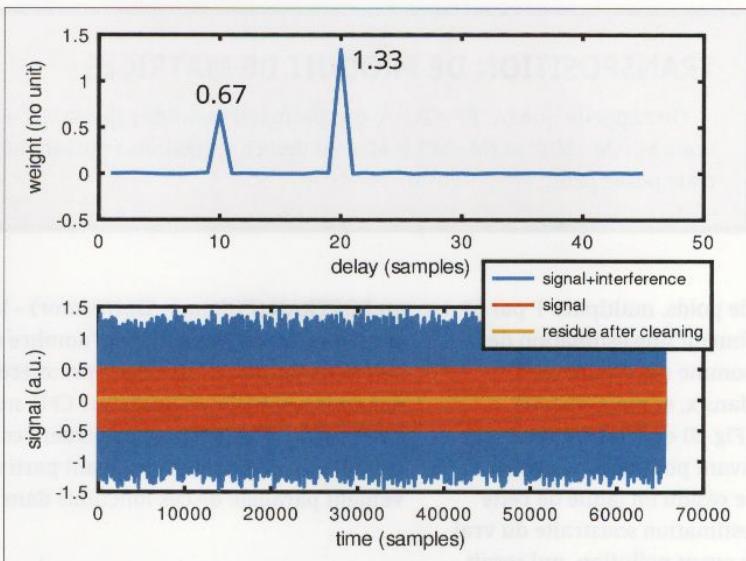

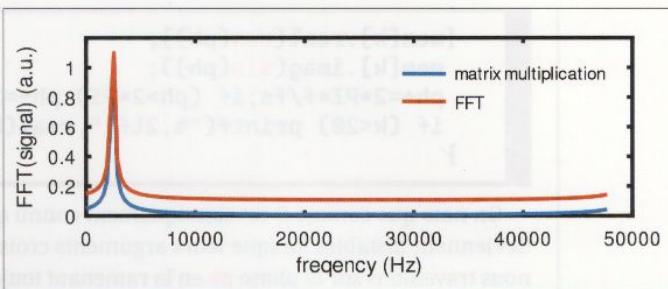

- 88** Algèbre linéaire rapide : BLAS, GSL, FFTW3, CUDA et autre bestiaire de manipulation de matrices dans le traitement de signaux de radio logicielle

### ABONNEMENT

- 75** Abonnement

#### RETROUVEZ CE NUMÉRO ET BIEN PLUS ENCORE SUR

#### CONNECT

- » articles gratuits

- » contenu premium

- » listes de lecture...

[CONNECT.ed-diamond.com](http://CONNECT.ed-diamond.com)

#### À PROPOS DE HACKABLE...

#### HACKS, HACKERS & HACKABLE

Ce magazine ne traite pas de piratage. Un **hack** est une solution rapide et bricolée pour régler un problème, tantôt élégante, tantôt brouillonne, mais systématiquement créative. Les personnes utilisant ce type de techniques sont appelées **hackers**, quel que soit le domaine technologique. C'est un abus de langage médiatisé que de confondre « pirate informatique » et « hacker ». Le nom de ce magazine a été choisi pour refléter cette notion de **bidouillage créatif** sur la base d'un terme utilisé dans sa définition légitime, véritable et historique.

# ALIMENTATION DP100 : CREUSONS UN PEU...

Denis Bodor

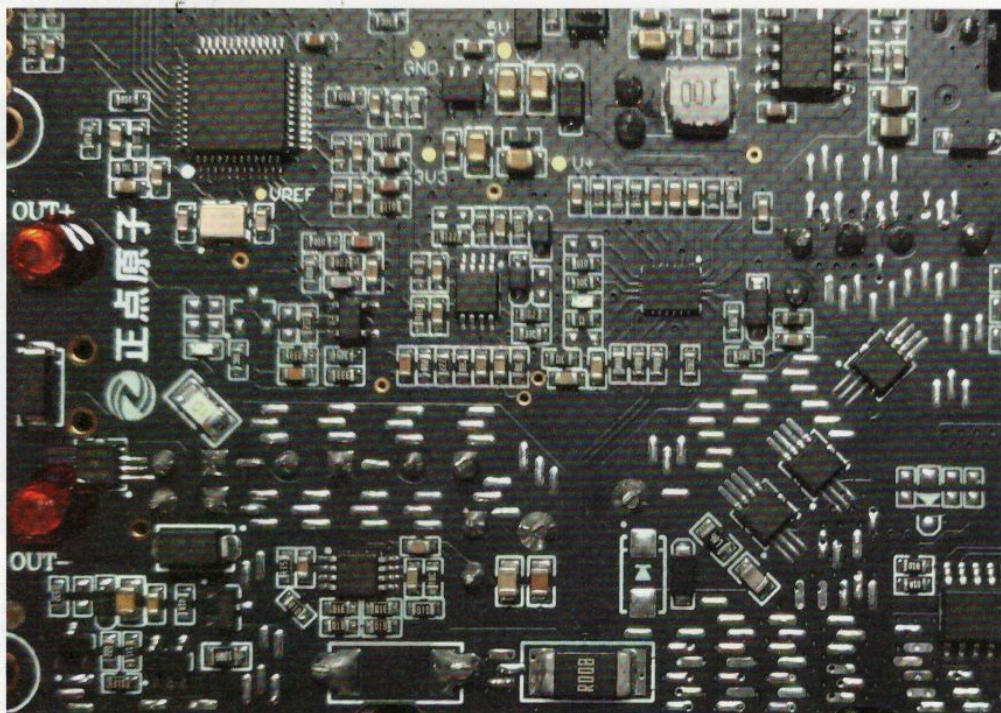

Dans un précédent article, nous avons découvert l'alimentation DP100 d'ALIENTEK, pris en main son fonctionnement de base, utilisé un outil écrit en Rust pour contrôler son comportement depuis un PC ou un SBC et avons même poussé le vice jusqu'à en faire un périphérique utilisable via le réseau grâce à USBIP. Ayant de grands projets pour cet appareil, je pense qu'il est temps de fouiller un peu davantage dans son fonctionnement, et le protocole qu'il utilise via USB...

– Alimentation DP100 : creusons un peu... –

**A** la fin de l'article précédent, je vous expliquais que mes connaissances en Rust, ainsi que mon intérêt pour ce langage étaient relativement limités. Le code, c'est comme les légumes, il y a ceux qu'on aime, ceux sans grand attrait, mais vis-à-vis desquels on « fait avec » et ceux qu'on trouve totalement repoussants (par définition le céleri, donc). C'est une question de goût et de syntaxe. Difficile donc, pour moi, de construire sur le code de *lessu* [1] et de faire évoluer ce qui semble surtout être un PoC (*Proof of concept*), vers quelque chose pouvant transformer le DP100 en une alimentation réellement programmable. Plusieurs options s'offraient à moi en termes de langages, mais une seule concernant l'approche elle-même : comprendre le protocole utilisé entre le PC/SBC et le DP100 pour, 1, obtenir des informations de l'appareil et 2, pouvoir contrôler son fonctionnement. Ceci, avec l'objectif premier de pouvoir prendre des mesures récurrentes et les stocker dans un format utilisable par la suite, et de pousser la notion de scriptabilité le plus loin possible.

C'est donc avec ces objectifs en tête que je me suis attelé à la tâche, grandement facilitée par la présence d'un fichier **DP100\_Protocol.md**

dans le dépôt de *lessu*, même si celui-ci est partiellement en chinois et que sa traduction automatique (avec des choses comme DeepL) est parfois assez déroutante. Découvrant la logique étrange derrière le protocole, il me semble intéressant de partager cette expérience, tant pour la méthode que pour le résultat.

**Le DP100 d'ALIENTEK** est un sympathique équipement de relativement bonne facture (voire très bonne facture). Le protocole qu'il utilise en USB, en revanche, est... étrangement incohérent.

## 1. USB HID

Nous l'avons vu la dernière fois, le DP100 se présente comme un périphérique USB HID lorsqu'il est connecté à un hôte (PC, Mac, SBC ou autre) et que son connecteur USB-A femelle est configuré en mode *device*. Ce périphérique est automatiquement pris en charge par un pilote générique USB HID avec un système GNU/Linux (ou FreeBSD, d'ailleurs) et vous vous retrouverez avec une interface que vous pourrez directement utiliser. HID, pour *Human Interface Device*, est généralement associé aux périphériques d'entrée comme les claviers, les souris, les tablettes graphiques ou encore d'autres pseudo-claviers comme le Stream

## HACK & UPCYCLING

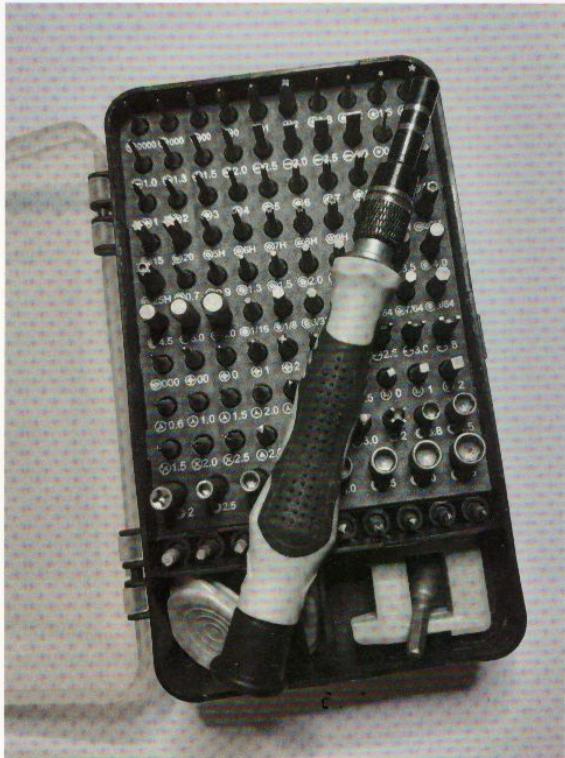

Les vis qui tiennent le boîtier fermé, et se trouvent sous les petits patins en mousse, nécessitent un embout TORX T6H, car elles ont un petit ergot en leur centre. Ce type de vis est relativement peu courant et vous devrez sortir vos outils de compétition...

Deck d'Elgato. Mais ce protocole, et donc ce type de matériel, va beaucoup plus loin puisqu'il décrit non seulement la manière d'échanger des données avec un périphérique au plus bas niveau, mais intégrer, en plus, une solution pour obtenir, directement du périphérique lui-même, la structure des données qu'il faut utiliser. Les constructeurs peuvent alors implémenter ce qui leur chante, tout en respectant un standard et en disposant, au final, d'une solution qui « se décrit elle-même ». C'est pourquoi USB HID est également utilisé pour tout un tas d'autres appareils allant du gadget lumineux aux clés de sécurité type Yubikey, et ce, non seulement sur PC et tablettes/smartphones, mais également avec des consoles de jeu, comme nous avons pu le voir avec le *Toy Pad LEGO Dimensions* dans le numéro 50 [2].

Si nous nous penchons sur le DP100 connecté à un PC GNU/Linux, nous constatons qu'il est effectivement listé parmi les périphériques HID du système :

```

$ ls -F /sys/bus/hid/devices/

0003:046A:0023.0002@

0003:046A:0023.0003@

0003:093A:2510.0004@

0003:0D8C:0014.0001@

0003:2E3C:AF01.0013@

```

La dernière ligne, présentant les ID USB du matériel ALIENTEK, est un lien symbolique vers un répertoire listant, entre autres choses, un fichier contenant le descripteur de rapport HID (*USB HID Report Descriptor*) :

```

$ hd /sys/bus/hid/devices/0003\:2E3C\:AF01.0013/report_descriptor

00000000 06 ff 00 09 01 a1 01 15 00 25 ff 75 08 95 40 09 |.....%.u..@.|

00000010 01 81 02 95 40 09 01 91 02 95 01 09 01 b1 02 c0 |....@.....|

00000020

```

Il s'agit là de la fameuse structure de données à utiliser pour échanger (par envoi et réception de « rapports » HID) des informations avec le périphérique. En l'état, ce n'est qu'un lot de valeurs binaires, mais en utilisant un outil en ligne [3], on peut facilement obtenir quelque chose de plus intelligible :

- Alimentation DP100 : creusons un peu... -

```

0x06, 0xFF, 0x00, // Usage Page (Reserved 0xFF)

0x09, 0x01, // Usage (0x01)

0xA1, 0x01, // Collection (Application)

0x15, 0x00, // Logical Minimum (0)

0x25, 0xFF, // Logical Maximum (-1)

0x75, 0x08, // Report Size (8)

0x95, 0x40, // Report Count (64)

0x09, 0x01, // Usage (0x01)

0x81, 0x02, // Input (Data,Var,Abs,No Wrap,Linear,

// Preferred State,No Null Position)

0x95, 0x40, // Report Count (64)

0x09, 0x01, // Usage (0x01)

0x91, 0x02, // Output (Data,Var,Abs,No Wrap,Linear,

// Preferred State,No Null Position,Non-volatile)

0x95, 0x01, // Report Count (1)

0x09, 0x01, // Usage (0x01)

0xB1, 0x02, // Feature (Data,Var,Abs,No Wrap,Linear,

// Preferred State,No Null Position,Non-volatile)

0xC0, // End Collection

// 32 bytes

```

On voit ici qu'il n'y a qu'un jeu de données (une collection), sans usage standardisé (souris, clavier, etc.), sans ID de rapport et se limitant à 64 valeurs de 8 bits. Pour communiquer avec ce périphérique, nous devons échanger 64 octets sans structures normalisées. Attention, ceci est à prendre au sens HID du terme et signifie uniquement que ces 64 octets répondent à un format et une organisation qui est propre au matériel et non une classe de matériel. USB HID est utilisé ici comme simple vecteur de communication, évitant au constructeur de devoir développer un pilote de périphérique et se contentant de créer une application qui pourrait tout aussi bien faire de même via une communication série par exemple, ce serait exactement le même principe.

Le point suivant consiste donc à savoir comment sont organisés ces 64 octets et ce qu'ils signifient, dans un sens (hôte vers périphérique) ou dans l'autre (périphérique vers hôte).

## 2. PROTOCOLE DE BASE

Pour cette partie, nous n'avons pas beaucoup de solutions et, en l'absence d'autres sources d'informations, ce qui n'est heureusement pas le cas ici, nous n'aurions d'autre choix que d'analyser les communications entre le logiciel propriétaire (et pour Windows) du constructeur et le périphérique. Pour cela, plus d'une technique peut être mise en œuvre, allant de celle purement logicielle (espionner ce que fait le pilote USB au travers d'une émulation Windows, par exemple) à celle reposant sur un analyseur logique ou un outil dédié comme le très coûteux Beagle USB 480 de Total Phase. Fort heureusement pour nous, *lassu* a déjà fait ce travail et résumé son analyse dans le fichier [DP100\\_Protocol.md](#).

## HACK & UPCYCLING

De plus, nous avons également les sources Rust de son outil et, même s'il n'est pas facile de s'y retrouver dans le code lorsqu'on n'est pas coutumier du langage (c'est d'ailleurs l'un de mes griefs à l'encontre de Rust que je trouve syntaxiquement horrible), nous avons un atout de taille dans notre manche : [src/lib.rs](#). Et plus exactement, ces deux groupes de lignes en commentaire dans la fonction `session` :

```

// print!("Write:");

// for d in output{

//     print!("{:02x}",d);

// }

// println!();

[...]

// print!("Read:");

// for d in input{

//     print!("{:02x}",d);

// }

// println!();

```

Nous pouvons décommenter ces lignes, puis recompiler l'outil, avant de tenter une nouvelle exécution, et :

```

$ ./target/debug/cli status

Write: fb10000030c50000000000000000000000000000000

000000000000000000000000000000000000000000000000000

000000000000000000000000000000000000000000000000000

000000000000000000000000000000000000000000000000000

Read:fa10002841544b2d445031303000ffff

ffffffff0e000e000b00aa0071351400

00c026220aa71805e807040343ef0000

000000000000000000000000000000000000000000000000000

Device 0 name:ATK-DP100

Write:fb300000310f00000000000000000000000000000000

000000000000000000000000000000000000000000000000000

000000000000000000000000000000000000000000000000000

000000000000000000000000000000000000000000000000000

Read:fa300010024e0000000aa4b43014201

c813020029520e000b00aa0071351400

00c026220aa71805e807040343ef0000

000000000000000000000000000000000000000000000000000

Basic Info:

vin:19.97V

vout:0V

iout:0A

vo_max:19.37V

temp1:32.3°C

temp2:32.2°C

dc_5v:5.064V

```

## alimentation

- Alimentation DP100 : creusons un peu... -

```

out_mode:2

work_st:0

Write:fb35000180ce28000000000000000000000000

000000000000000000000000000000000000000000

000000000000000000000000000000000000000000

000000000000000000000000000000000000000000

Read:fa35000a0300d00764002477ba133626

c813020029520e000b00aa0071351400

00c026220aa71805e807040343ef0000

000000000000000000000000000000000000000000

Basic Set <3>: Off

vo_set:2V

io_set:0.1A

ovp_set:0.1V

ocp_set:5.05A

```

En plus des informations décodées par l'outil, nous voyons également à présent les 64 octets envoyés (**Write**) et reçus (**Read**) lors de chaque transaction. Ceci s'avérera fort utile pour comprendre le sens de l'étrange contenu de **DP100\_Protocol.md**, y compris ce qui y est spécifié en anglais, mais n'a absolument aucun sens (comme **moon** pour la commande **DEVICE\_INFO** qui en réalité est **month**, le « mois » d'une date).

Pour commencer, parlons des fameux blocs de 64 octets et des différentes parties qui les composent. Certaines valeurs et positions sont fixes et d'autres dépendent de la taille des données. Nous avons dans l'ordre :

- Une direction (1 octet) : avec **0xfb** pour hôte vers périphérique et **0xfa** pour le sens inverse. Tous les messages que nous enverrons depuis le PC/SBC débuteront par **0xfb** et les réponses obtenues par **0xfa**. Pourquoi ? Aucune idée, le protocole fonctionnerait tout aussi bien sans cet octet.

- L'opération ou commande (1 octet) : cet octet correspond à un ordre passé au périphérique qui peut être une demande d'information ou d'action. Le périphérique répond toujours en répétant l'octet en question à la même position.

- Octet **0x00** qui ne semble jamais changer, sans doute réservé pour un futur usage.

- Une taille (1 octet) qui correspond au nombre d'octets qui vont suivre et qui forment les arguments d'une commande ou les données d'une réponse. Ce champ est également toujours présent dans une réponse. Notez que cette taille peut parfaitement être zéro.

- Les données (*x* octets) dont la taille dépend de la commande utilisée ou de la requête effectuée.

- Une somme de contrôle ou plus exactement un CRC (2 octets) : il s'agit d'un CRC-16/MODBUS calculé sur l'ensemble des octets de **0xfb/0xfa** à la fin des données. Le CRC est intégré en *little endian* avec les huit bits de poids faible en premier, puis les huit bits de poids fort.

## HACK & UPCYCLING

Les commandes utilisables, telles que listées dans [DP100\\_Protocol.md](#), ne sont pas toutes clairement détaillées. Certaines sont des suppositions non testées et d'autres sont presque parfaitement décrites. *lessu* semble avoir extrait ces informations d'un désassemblage de l'application Windows et non via une écoute du trafic USB entre le PC et l'appareil. Ceci est heureusement suffisant pour gérer ce qui nous intéresse et nous avons donc :

- **0x10 : DEVICE\_INFO**, permet d'obtenir des informations de base sur le matériel comme son nom, numéro de série ou encore la version du *firmware* utilisé.

- **0x12 : START\_TRANS**, non documenté.

- **0x13 : DATA\_TRANS**, non documenté.

- **0x14 : END\_TRANS**, non documenté.

- **0x15 : DEV\_UPGRADE**, non documenté, mais en rapport avec la mise à jour du *firmware* faite avec l'application du constructeur. Pas nécessairement quelque chose avec quoi expérimenter si l'on ne veut pas transformer son DP100 en presse-papier.

- **0x30 : BASIC\_INFO**, retourne différentes informations sur l'état du matériel, dont la tension et le courant mesurés en sortie, la tension en entrée (USB-PD), la mesure des deux capteurs de température internes, etc.

- **0x35 : BASIC\_SET**, à la fois une commande pour s'enquérir des réglages en cours d'utilisation, ceux des 10 profils enregistrés et pour procéder à des modifications de ces derniers. C'est aussi cette commande qui permet d'activer et désactiver la sortie du DP100 (cf. ci-après).

- **0x40 : SYSTEM\_INFO**, permet d'obtenir quelques réglages des préférences accessibles via la double pression sur « carré » comme l'intensité de l'écran ou le volume du bip.

- **0x45 : SYSTEM\_SET**, non documenté. Très certainement le réglage des préférences lié à *SYSTEM\_INFO*.

- **0x50 : SCAN\_OUT**, non documenté, mais la signification des arguments de la commande est listée et ils nous permettent de supposer qu'il s'agit d'une sorte d'automatisation visant à définir des valeurs successives de tension ou de courant sur une plage de temps donnée.

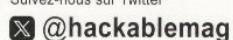

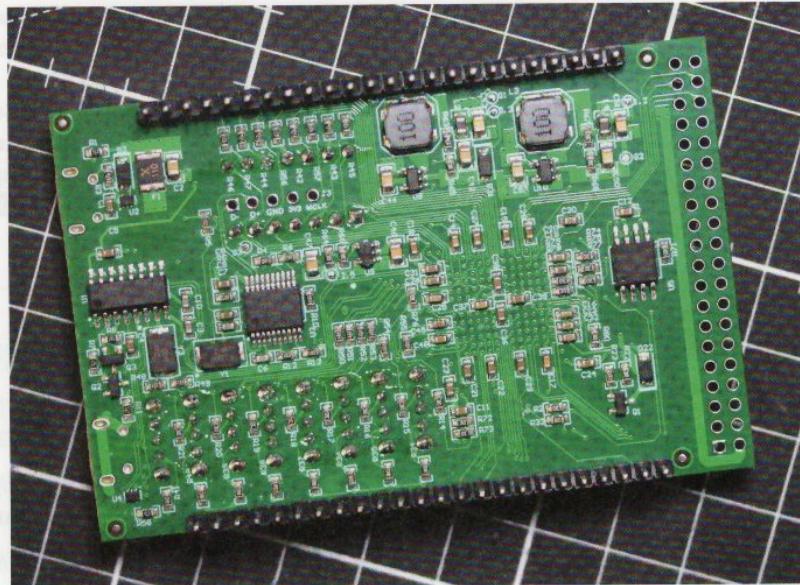

L'ouverture du produit révèle une qualité surprenante et on comprend mieux pourquoi le produit n'est pas dans la gamme de prix qu'on trouve généralement sur AliExpress.

## - Alimentation DP100 : creusons un peu... -

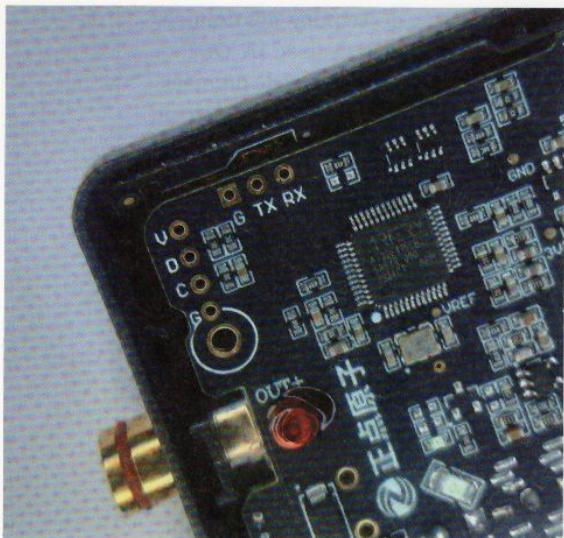

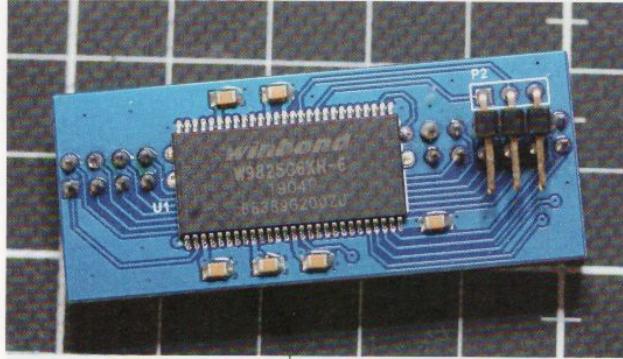

- **0x55** : *SERIAL\_OUT*, non documenté, mais là encore, nous avons la description des données en argument, qui laisse penser que c'est peut-être une mécanique inverse de *SCAN\_OUT* avec des mesures successives ou éventuellement la configuration d'une source de données série pour le même type d'opération. Le terme « *SERIAL* » est probablement en lien avec un emplacement à souder, disponible à l'intérieur de l'appareil, libellé « G TX RX » (juste à côté d'un autre, marqué « V D C G », certainement pour *Vcc*, *Data*, *Clock*, *Ground* (du SPI ? I2c ?)).

- **0x80** : *DISCONNECT*, non documenté.

Nous avons là les briques nécessaires pour réimplémenter l'outil de *lessu* dans n'importe quel langage disposant d'une bibliothèque capable d'envoyer et de recevoir des rapports HID. Ceci, bien entendu, en plus de ce qui est nativement disponible sur le système d'exploitation utilisé. GNU/Linux, par exemple, comme FreeBSD, met à disposition une entrée dans `/dev` et un certain nombre d'IOCTL permettant de totalement se passer de bibliothèque dédiée (comme *hidapi* [4], par exemple), même si cela reste la solution généralement la plus « portable ».

Le reste de [DP100\\_Protocol.md](#) détaille relativement bien les arguments et données envoyés et retournés pour chaque commande, avec un type (`uint8/uint16`) et une description. Deux points cependant sont à noter pour ne pas perdre son temps : les données 16 bits sont toujours en *little endian* et, plus important, les valeurs à virgule flottante (tension, courant, etc.) n'en sont pas, il s'agit de valeurs entières 16 bits à diviser par 1000 ou par 10 (température).

À titre d'exemple, voici ce que retourne la commande *BASIC\_INFO* composée ainsi :

```

fb 30 00 00 310f

```

Nous avons donc **0xfb** pour la direction hôte->périphérique, **0x30** pour *BASIC\_INFO*, **0x00** toujours à **0x00** et **0x00** pour la taille des données. Le tout terminé par le CRC16. En retour, nous obtenons :

```

fa 30 00 10 e54d48071000aa4b46014a01d1130000 e913

```

- **e54d** -> **0x4de5** -> 19941 -> 19,941 V, tension en entrée ;

- **4807** -> **0x0748** -> 1864 -> 1,864 V, tension mesurée en sortie ;

- **1000** -> **0x0010** -> 16 -> 0,016 A, courant mesuré en sortie ;

- **aa4b** -> **0x4baa** -> 19370 -> 19,370 V, tension maximum ;

- **4601** -> **0x0146** -> 326 -> 32,6 °C, température 1 ;

- **4a01** -> **0x014a** -> 330 -> 33,0 °C, température 2 ;

- **d113** -> **0x13d1** -> 5073 -> 5,073 V, tension mesurée pour le 5 V DC ;

- **0x00** -> sortie active en mode courant constant (c'est une LED rouge qui impose actuellement les 1,864 volt sur la sortie), **0x02** indique une sortie inactive et **0x01** une sortie pilotée en tension constante ;

- **0x00** -> aucune idée, mais un libellé « *workst* » est indiqué dans [DP100\\_Protocol.md](#) (*working status*, peut-être ?).

L'inspection du circuit révèle la présence d'un emplacement pour une liaison série (RX/TX est relativement explicite) et ce qui semble être une connectivité SPI ou i2c avec « D » pour « data » et « C » pour « clock » (en plus de G pour la masse et V pour Vcc).

Le même genre de dissection peut être opéré avec *DEVICE\_INFO* et *SYSTEM\_INFO* et nous pouvons donc déjà atteindre un premier objectif : écrire un outil qui va automatiquement procéder à ces requêtes de manière récurrente, décoder l'information et l'afficher, avec un horodatage à la milliseconde, dans une sortie type CSV. Celle-ci pourra ensuite être retraitée avec un utilitaire ou une application pour produire, par exemple, un joli graphique.

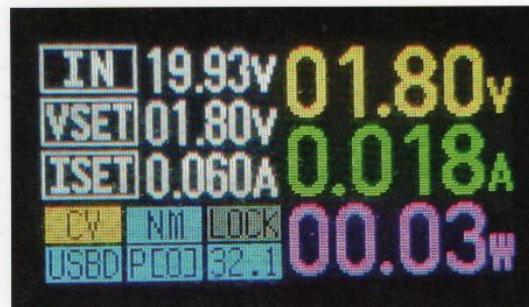

À noter que chaque transaction en USB bloque l'interface utilisateur physique sur le DP100. Celui-ci notifie ce blocage en mettant en surbrillance le mot « LOCK » à l'écran et les boutons n'ont alors plus aucun effet. Ceci signifie que, en cas de mesures répétées rapidement, il n'est pas possible d'activer ou de désactiver la sortie ou de procéder à tout autre réglage. Il nous faut donc, pour bien faire, disposer d'un moyen de gérer cela via USB et donc comprendre comment donner des ordres au DP100.

### 3. GESTION DES PROFILS ET ACTIVATION

C'est là que les choses deviennent un peu... étranges, du point de vue des choix faits dans le protocole. En effet, vous remarquerez que le résultat de la commande *BASIC\_INFO* ne retourne absolument pas les paramètres (tension et courant) choisis pour configurer la sortie, uniquement les mesures lorsque cette sortie est active. Ceci alors même qu'il est possible, sur le DP100, de régler ces paramètres directement sur l'écran principal, sans avoir à éditer et à modifier l'un des 10 profils de configuration stockés en mémoire.

La clé de ce mystère réside précisément dans la gestion de ces profils, accessibles via une pression longue sur le bouton « triangle droit ». En réalité, lorsqu'on ajuste les paramètres de sortie sur l'écran principal (avec une pression longue sur le bouton carré), un profil est actif et celui-ci est affiché sur le bas de l'écran sous la forme « P[n] » avec « n » une valeur entre 0 et 9. Un ajustement des paramètres ne fait pas que changer les valeurs courantes, ceci modifie également celles du profil actif, **s'il s'agit du profil 0**, qui se trouve alors mis à jour et enregistré dans le même temps.

Du point de vue de la commande via USB HID, ceci signifie donc qu'il n'est pas possible d'influer sur les réglages courants et qu'il faut passer obligatoirement par une modification de profil, et éventuellement son activation (comprendre « en faire le profil actuellement utilisé »). Pire encore, le constructeur a fait un choix étrange concernant l'un des éléments de configuration de ces profils.

## alimentation DAH

- Alimentation DP100 : creusons un peu... -

En effet, même si l'écran d'édition de profils du DP100 ne vous présente que 4 paramètres, tension (« VSET »), tension max (« OVP »), courant (« ISET ») et courant max (« OCP »), les données enregistrées en contiennent deux autres. Et ce n'est pas tout, la commande *BASIC\_SET*, en fonction de la longueur des données (arguments) qui l'accompagnent, agit soit comme une requête pour lire un profil, soit comme une action pour le modifier. Ainsi, si nous utilisons :

```

fb 35 00 01 80 ce28

```

Nous recevons en retour :

```

fa 35 00 0a 0300d00764002477ba13 3626

```

La commande **0x35**, *BASIC\_SET*, accompagnée de l'argument **0x80** nous renvoie le profil actif et ses paramètres ainsi :

- **03** -> index ;

- **00** -> état ;

- **d007** -> **0x07d0** -> 2000 -> 2,000 V, tension réglée ;

- **6400** -> **0x0064** -> 100 -> 0,100 A, courant réglé ;

- **2477** -> **0x7724** -> 30500 -> 30,500, tension max (« OVP ») ;

- **ba13** -> **0x13ba** -> 5050 -> 5,050 A, courant max (« OCP »).

C'est « index », en position 0 des données, qui indique le numéro du profil actuellement actif, et une variation de la commande, en remplaçant simplement **0x80** par une valeur entre **0x00** et **0x09**, permet de s'enquérir des paramètres d'un profil arbitrairement désigné et non nécessairement actif. Mais le plus troublant est le second octet qui, en lecture, est à **0x01** si la sortie est activée, et à **0x00** dans le cas contraire. Mais ceci **uniquement** en utilisant **0x80** pour la demande et non un numéro du profil, auquel cas c'est toujours **0x00**.

À ce stade, on se demande naturellement comment simplement activer la sortie via USB HID et la réponse consiste à tout bonnement retirer le « simplement » de la question. En effet, on ne peut pas « juste » impacter l'état de la sortie, il faut :

- s'enquérir sur le profil actif (index et paramètres) ;

- conserver les données obtenues ;

- les réutiliser à l'identique tout en modifiant le second octet pour influer sur la sortie et compléter la valeur d'index par un *OU* logique et **0x20** ;

- et enfin, utiliser ces données avec la commande *BASIC\_SET*.

En d'autres termes, on lit les paramètres du profil courant et on les réécrit au même endroit après ajustement. D'après *lessu*, les 4 bits de poids fort de l'index précisent l'action à opérer sur le profil avec **0x20** pour une modification, **0x80** pour une activation et **0xa** pour les deux combinés (**0x20 + 0x80**). Mais, en réalité, ce n'est pas tout à fait le cas. En expérimentant, on se rend compte que **0x80** permet effectivement de passer d'un profil actif à un autre et **0x20** prend en compte l'état pour piloter la sortie. Mais, en jouant sur les valeurs des paramètres, on se rend rapidement compte que l'affichage à l'écran change, sans que le profil désigné soit réellement modifié. Une petite pression longue sur le triangle droit nous montre les anciens paramètres et

un retour à l'écran principal les restaure en guise de valeurs actives. En revanche, et on sort alors de l'analyse de *lessu*, en utilisant **0x40** en lieu et place de **0x20**, là, les paramètres enregistrés changent, même si le profil n'est pas celui actif. Comment cette valeur est-elle arrivée là ? J'ai tout simplement essayé chaque bit de poids fort (et je ne sais pas ce que fait **0x10**).

Vous l'aurez compris, changer de profil actif suivra donc la même logique de lecture/écriture d'un profil. Ce qui est tout aussi tarabiscoté que l'activation de la sortie.

### 4. QUELQUES MOTS SUR L'IMPLÉMENTATION

Pour mon implémentation en C [5], qui est pour le moment loin d'être finie, le problème de l'accès au périphérique USB HID s'est naturellement posé. Qu'il s'agisse de GNU/Linux ou de FreeBSD, le système met généralement à disposition une interface aisément accessible sans avoir recours à une bibliothèque tierce. Cependant, en termes de portabilité, il faut alors adapter le code aux IOCTL disponibles et commencer à s'amuser avec des macros **#ifdef/#else** qui deviennent vite pénibles à gérer.

Le problème s'était déjà posé avec le périphérique LEGO Dimensions dans un précédent article et la solution a naturellement été la même : *HIDAPI* [4]. Cette bibliothèque présente une API unique permettant une utilisation sans modification du code, et ce pour GNU/Linux, Windows, macOS et FreeBSD. La documentation est conséquente, intelligible et les exemples étoffés. C'est donc la base choisie pour mon outil.

L'objectif, à terme, est de fournir un utilitaire proposant les mêmes fonctionnalités que le code Rust de *lessu*, mais complété d'une possibilité de faire des mesures récurrentes directement via des options en ligne de commandes (déjà implémenté à ce jour). Ceci permettra de simplement surveiller un montage et de collecter des données à court, moyen et long terme.

Mais l'étape suivante est, je pense, ce qui permettra de tirer le meilleur de ce que le DP100 peut offrir : une solution entièrement scriptable pour mettre en place des scénarios, un peu à la manière des courbes des fours à refusion pour

la soudure de composants CMS/SMD. Plutôt que d'implémenter cela avec une gestion de scripts propre à l'outil, l'idée est de simplement s'en remettre à un langage parfaitement prévu pour cela, c'est Lua. Intégrer l'interpréteur Lua dans un code en C et lui fournir des directives/fonctions permettant d'étendre ses fonctionnalités n'est vraiment pas difficile (voir article sur le sujet dans GNU/Linux Magazine 269 [6]) et ouvre des perspectives très intéressantes.

Le PoC, ou plus exactement la démonstration que l'objectif sera atteint, se résume à charger un accusateur LiPo avec le DP100 via un script Lua. En effet, ce type de batteries se charge via un système CC/CV où, durant une première phase, le composant est chargé avec un courant constant tout en surveillant la tension, puis une fois la tension nominale atteinte, celle-ci est maintenue alors que le courant est progressivement réduit.

Enfin, une autre idée qui me traîne en tête depuis que je me penche sur les *smart-cards* et que j'ai constaté un comportement très étrange lors de l'implémentation d'un lecteur basé sur une Raspberry Pi Pico (voir article dans le numéro 54 [7] : utiliser le DP100 comme

- Alimentation DP100 : creusons un peu... -

outil pour procéder à des attaques par canaux auxiliaires et plus particulièrement mettre en œuvre une attaque par *glitching* en jouant sur le courant fourni à la cible. En effet, avec la Pico, l'alimentation d'une *smartcard* via une broche GPIO est incapable de fournir le courant d'alimentation (VCC) nécessaire, et conduisait à des réponses pseudoaléatoires très suspectes. Je ne pense pas arriver à quelque chose de réellement exploitable en termes de temporation, le DP100 réagissant assez lentement, mais explorer le sujet peut être très intéressant, quitte à coupler l'appareil avec un montage complémentaire (à base de FPGA ?).

travail concurrent de plusieurs dévelopeurs ? Mystère...

Quoi qu'il en soit, grâce au travail accompli par *lessu* pour son code en Rust, nous avons pu explorer facilement le protocole utilisé et réimplémenter un outil répondant plus précisément à nos besoins. On ne peut donc que le remercier grandement d'avoir ouvert ce qui était, comme très souvent avec ce type de produits, une boîte noire aux possibilités d'évolution totalement limitées. De plus, cela prouve très agréablement que, quel que soit le lieu, l'origine, la langue ou tout autre critère de différenciation typiquement humain, la curiosité et le partage de connaissances est, et je l'espère restera toujours, la trame qui tient unis tous les (vrais) développeurs et bidouilleurs du monde entier. ■ DB

L'écran du DP100 présente, en bas à gauche, le profil de paramètre actif (« P[0] » ici pour le profil 0) ainsi que, juste au-dessus et à droite la mention « LOCK » qui passe en orange à chaque transaction USB, bloquant l'utilisation des boutons.

## 5. POUR FINIR

Cette petite exploration soulève bien des questions et je ne parle pas des éléments qui sont encore inconnus à ce stade (*SYSTEM\_SET*, *SERIAL\_OUT*, *DATA\_TRANS*, etc.). On se demande pourquoi cette logique de gestion de profils a été implémentée de la sorte et pourquoi *BASIC\_SET* sert à plusieurs usages, variant en fonction de l'index fourni. Est-ce un héritage d'un précédent modèle ? Le recyclage du code d'un *firmware* préexistant ? La conséquence du

## RÉFÉRENCES

- [1] [https://github.com/lessu/open\\_dp100](https://github.com/lessu/open_dp100)

- [2] <https://connect.ed-diamond.com/hackable/hk-050/jouons-aux-lego...-avec-des-tags-nfc>

- [3] <https://eleccelerator.com/usbdescreqparser/>

- [4] <https://github.com/libusbhidapi>

- [5] <https://gitlab.com/0xDRRB/dp100controler>

- [6] <https://connect.ed-diamond.com/gnu-linux-magazine/glmf-269/embarquez-un-peu-de-lua-dans-vos-projets-c>

- [7] <https://connect.ed-diamond.com/hackable/hk-054/carte-a-puce-et-microcontroleur>

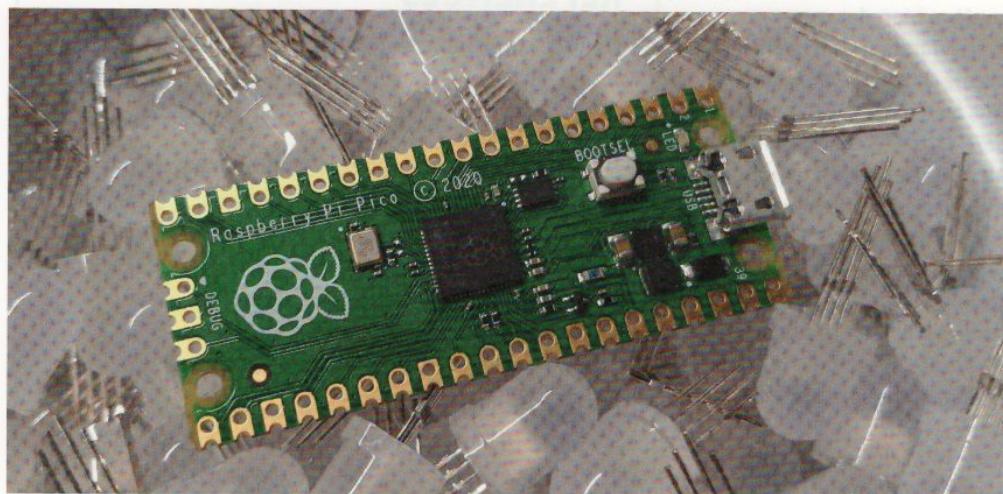

# CRÉEZ VOS PÉRIPHÉRIQUES USB AVEC RASPBERRY PI PICO

Denis Bodor

Lorsqu'on souhaite faire communiquer un périphérique de sa création avec un ordinateur, le réflexe est souvent de simplement utiliser un convertisseur USB/série. Parfois, celui-ci est d'ailleurs directement intégré à la carte de développement, comme c'est le cas pour de nombreux Arduino. Il y a cependant là quelque chose de fondamentalement inefficace, voire, d'un certain point de vue, de totalement obsolète. Un « vrai » périphérique, au sens « manufacturé » du terme, repose rarement sur une liaison série et préfère une solution plus contemporaine : l'USB. Fort heureusement pour nous, et même si le bus USB ne brille pas par sa simplicité, c'est quelque chose de parfaitement accessible avec une carte Raspberry Pi Pico...

Créez vos périphériques USB avec Raspberry Pi Pico

**U**n capteur quelconque, un montage pilotant un composant spécifique, une interface pour piloter des indicateurs ou des moteurs... les exemples de réalisations ayant besoin de communiquer avec un ordinateur, PC, Mac ou SBC, sont legion. La liaison série est un classique que l'on retrouve sur quasiment tous les microcontrôleurs du marché, en compagnie du bus SPI et de l'i2c, mais il ne s'agit pas d'une solution autre que simplement arrangeante, car excessivement facile à mettre en œuvre, du moins côté MCU. Car, en effet, en dehors d'échanges textuels entre le microcontrôleur et l'ordinateur, l'utilisation d'un port série, quel que soit le système d'exploitation utilisé, ce n'est pas vraiment une partie de plaisir dès lors qu'il s'agit de programmation. Certes, des langages bien adaptés au prototypage, comme Python, Lua ou JS (node), facilitent la tâche, mais supposent de surcharger son projet avec interpréteur. Là, je vous parle de C et donc de légèreté, mais aussi de développement bas niveau, voire de l'implémentation d'un support dans un noyau sous

la forme d'un pilote de périphérique. Point de Python à ce niveau, et si vous avez déjà fait l'expérience des communications série en C, vous devinez que ce n'est pas un chemin qu'on souhaite nécessairement arpenter...

Précisons tout de même que la notion de communication série, au sens Arduino du terme, n'est pas pour autant totalement à exclure. Elle a ses qualités et ses usages, mais ceci se limite principalement aux utilisations interactives, via un « moniteur série » comme Minicom, GNU Screen ou encore PuTTY sous Windows. Il existe d'ailleurs des bibliothèques et implémentations d'interfaces en ligne de commande (REPL, *Read Evaluate Print Loop*) pour ce type de choses, comme l'excellent et très portable *Tokenline* [1] [2], utilisé par exemple dans le firmware HydraBus que nous avons exploré dans le numéro 53 [3].

Mais en dehors de cela, quand une machine veut communiquer avec un périphérique, et plus exactement quand un programme sur un ordinateur veut échanger des données avec du matériel externe, en dehors de l'USB, aujourd'hui, point de salut. À noter qu'il en va de même à l'intérieur des machines, où PCIe est la norme désormais, même SATA laisse peu à peu la place à NVMe, et donc à PCIe.

## 1. USB ?

Je ne doute pas un instant que vous savez ce qu'est l'USB. Il est présent partout, sur votre PC/Mac, votre smartphone, vos SBC, vos cartes à microcontrôleur et sur n'importe quel gadget qui de près ou de loin a un vague rapport avec un ordinateur. Ce standard, quelle que soit sa version, est omniprésent et en termes d'utilisations pures, la difficulté réside principalement dans la connectique et donc la version des spécifications utilisées. Bref, on branche et ça marche sans qu'on ait besoin de se poser trop de questions. Cette polyvalence est sans nul doute ce qui a fait le succès de l'USB, car c'est un bus universel (le « U » de USB), capable de s'adapter à presque tous les périphériques imaginables, souris, claviers, stockage, adaptateurs, instruments de mesure, sondes, systèmes d'affichage, caméras, lecteurs avec ou sans contact, etc.

Comment fonctionne un bus USB et comment écrire son code ?

## 1.1 Échange de données

Nous n'allons pas ici entrer dans le détail des spécifications et aborder des points qui ne sont pas vraiment importants pour la tâche qui nous intéresse, comme les caractéristiques électriques, le format des connecteurs, etc. La Raspberry Pi Pico, comme bien d'autres cartes à microcontrôleur, dispose de tout le nécessaire pour s'occuper de cela à notre place, nous laissant nous concentrer sur la partie de plus haut niveau des protocoles. En effet, USB, comme d'autres standards, est un modèle à couche, avec des spécifications pour chacune d'elles. Ici, ce qui nous intéresse, ce ne sont pas les signaux au plus bas niveau, car nous ne comptons pas implémenter un contrôleur USB, mais simplement utiliser celui à notre disposition via une bibliothèque livrée avec le SDK Pico, à savoir TinyUSB [4].

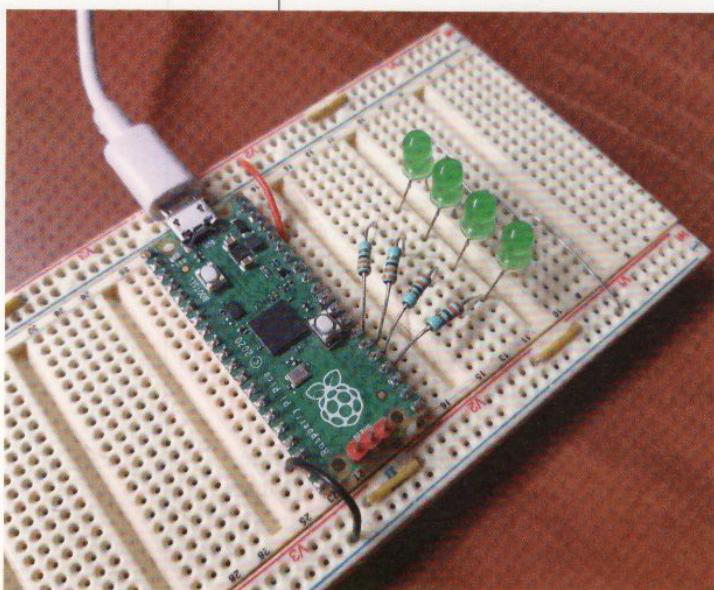

*Voici la victime de nos petites expérimentations sur une platine à essais. Nous n'utilisons qu'une seule LED dans notre exemple, mais étendre le code pour en gérer plusieurs sera un jeu d'enfant.*

Cependant, la terminologie utilisée, reprise dans le code, nous oblige à tout de même comprendre quelques éléments structurels du bus. Premièrement, les échanges entre l'hôte et le périphérique prennent la forme de transactions composées de paquets de données intégrant un entête, des données et un ensemble de champs définissant, entre autres, le type de transaction dont il s'agit. Il existe 4 types de paquets USB, pouvant former une transaction ou trame :

- les paquets *token* forment l'entête et précisent le type de transaction qui s'en suit ;

- les paquets de données (*data*), optionnels, qui véhiculent les informations, ou dans le jargon qui convient, la charge utile, ou *payload* en anglais ;

- les paquets d'état ou de négociation, permettant de valider les transactions via des accusés de réception, par exemple ;

- et enfin, les paquets SOF (*Start of Frame*) destinés à maintenir la communication entre l'hôte et le périphérique sous forme d'échanges réguliers, avec une fréquence dépendante de la vitesse de communication.

Seuls deux de ces éléments nous intéressent à notre niveau, c'est le type de transaction et le *payload*. Le reste est parfaitement pris en charge automatiquement pour nous et il en va de même pour le formatage, la composition et le décodage de ces trames ou transactions. Ces différents types se divisent ensuite en sous-types. Les paquets *token*, par

– Créez vos périphériques USB avec Raspberry Pi Pico –

exemple, peuvent être des *tokens* d'entrée, de sortie ou de configuration. Un champ particulier, nommé PID (*Packet ID*) identifie le type et sous-type sur 4 bits.

Le standard USB va beaucoup plus loin, en spécifiant non seulement tout ceci, mais en définissant également un certain nombre de protocoles reposant sur ce que nous venons de voir. L'objectif est d'uniformiser et de normaliser les informations échangées, du moins pour ce qui concerne certains types de périphériques. Ces standards supplémentaires sont précisément ce qui permet à un périphérique USB de fonctionner sur plusieurs architectures et systèmes, sans nécessiter l'installation d'un pilote spécifique. Inversement, un système sachant prendre en charge un type ou une classe de périphériques précis sera alors en mesure d'également gérer tous les matériels qui répondent aux spécifications établies, indépendamment du constructeur. Voilà pourquoi une clé USB de stockage donnée pourra facilement être utilisée sur n'importe quel hôte et un hôte précis, comme votre PC, SBC ou smartphone ne fera aucune différence entre une clé de stockage Samsung, SanDisk, Corsair, Kingston, Philips ou Lexar...

Il existe des classes pour un grand nombre de périphériques, imprimantes, stockage, caméras, hubs, périphériques d'entrée (claviers, souris, etc.), communication série, audio (micros, sorties HP, etc.), mais là encore, ce n'est pas vraiment ce qui nous occupe ici. Non seulement créer un périphérique d'une classe existante n'est que peu intéressant en soi (sauf cas particulier), mais ceci est généralement très bien pris en charge par les bibliothèques courantes comme TinyUSB, avec un minimum d'efforts à fournir. C'est d'ailleurs ce que fait le RP2040 des Pico en mode *BOOTSEL*, se présentant comme un périphérique de stockage (classe *Mass Storage Device*). Non, ce que nous voulons, nous, c'est communiquer avec notre propre « protocole » construit sur les spécifications existantes, pas recréer un périphérique qui existe déjà.

## 1.2 Plug'n'play

La question que vous devez sans doute vous poser maintenant, du moins je l'espère, est la suivante : comment l'hôte détermine-t-il la façon de communiquer avec le périphérique en fonction de sa classe ? La réponse tient en un unique mot : « énumération ». L'énumération USB est le processus permettant à l'hôte d'obtenir tout ce qu'il doit savoir d'un périphérique qui vient d'apparaître sur le bus. Voici, sommairement ce qui se passe :

- connexion du périphérique sur l'hôte (port USB ou hub, peu importe) ;

- détection de la présence du périphérique par l'hôte ;

- identification de la vitesse de communication à utiliser ;

- obtention du(des descripteur(s) de périphérique ;

- reset du périphérique et attribution d'une adresse sur le bus ;

- obtention du(des descripteur(s) de configuration ;

- obtention du(des descripteur(s) d'interface ;

- chargement du pilote (s'il existe) ;

- utilisation par le système.

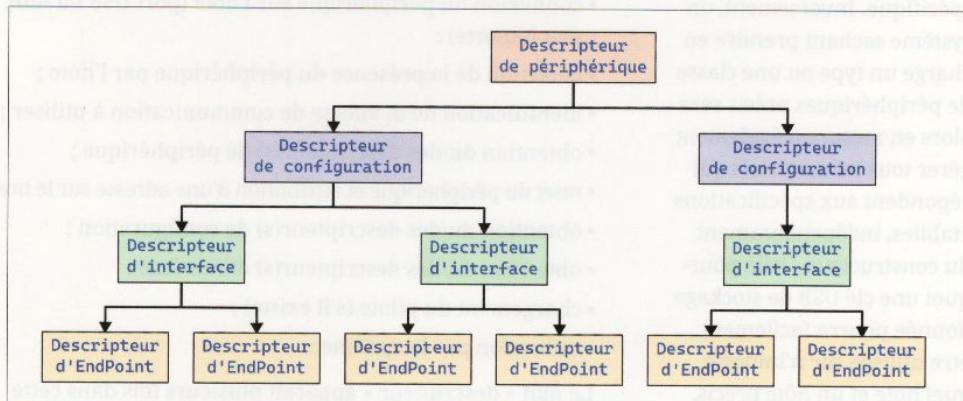

Le mot « descripteur » apparaît plusieurs fois dans cette procédure qui, dans sa majorité, ne nous concerne pas, tout ceci est automatique et surtout, relève de la responsabilité de l'hôte. Ce qui est capital en revanche, c'est précisément ce que contiennent ces fameux descripteurs. Pour le savoir, il est important avant toute chose de comprendre qu'un périphérique USB est en réalité une arborescence d'éléments.

# MICROCONTRÔLEURS & ARDUINO

- Le descripteur de périphérique regroupe les informations concernant tout le périphérique comme ses ID (vendeur et produit), des chaînes de caractères décrivant le constructeur, produit et numéro de série, la version USB et le nombre de configurations présentes.

- Le ou les descripteurs de configuration contiennent des informations sur la manière d'alimenter le périphérique et les interfaces qu'il contient. L'hôte est ainsi informé non seulement des interfaces présentes, mais également des besoins en énergie lorsqu'une configuration est activée. La plupart du temps, les périphériques ne contiennent qu'une seule configuration.

- Le ou les descripteurs d'interface qui, comme le nom l'indique, informent sur les interfaces utilisables pour dialoguer avec le périphérique. S'il existe plusieurs interfaces, l'hôte peut choisir celle qu'il souhaite utiliser pour accéder aux fonctionnalités de son choix. Ce descripteur précise également la classe et sous-classe de l'interface ainsi que les descripteurs d'Endpoints qui y sont rattachés (techniquement, une interface est une collection d'Endpoints).

- Les descripteurs d'Endpoints, ou de points de terminaison. Un Endpoint (ou EP) est une source ou une cible pour les échanges de données et l'élément terminal de la communication. Un Endpoint est unidirectionnel, ce qui signifie donc que vous aurez toujours une paire d'Endpoints, un OUT pour recevoir des données et un IN pour en envoyer (plus exactement, pour que l'hôte les récupère, puisque c'est lui qui contrôle le bus). Notez que les termes « OUT » et « IN » sont définis du point de vue de l'hôte, « OUT » signifiant « en sortie de l'hôte » et « IN », « en entrée ». Les Endpoints sont numérotés, et EP0IN/EP0OUT sont réservés aux données de contrôle du périphérique, utilisées en particulier durant la phase d'énumération. Du point de vue de notre développement, encore une fois, vous n'avez pas à vous soucier de ces EP là.

Un périphérique USB contient une représentation de ce qu'il est et la propose sous la forme de descripteurs agencés en une arborescence.

Créer un périphérique USB, sur base RP2040 (ou d'autres MCU), nécessite donc la rédaction des descripteurs, en particulier celui du périphérique et au moins un descripteur de configuration (et par conséquent un descripteur d'interface et deux pour les Endpoints, même si, en pratique tout est lié). Pour asséoir ces notions, on pourra consulter les informations d'un périphérique USB existant très simplement sur un SBC Raspberry Pi, par exemple avec :

## CHUCA TinyUSB / Pico

- Créez vos périphériques USB avec Raspberry Pi Pico -

```

$ lsusb -v -d 1fd3:0608

Bus 003 Device 009: ID 1fd3:0608 ASK LoGO

Device Descriptor:

bLength          18

bDescriptorType   1

bcdUSB         2.00

bDeviceClass       0

bDeviceSubClass     0

bDeviceProtocol      0

bMaxPacketSize0      8

idVendor        0x1fd3

idProduct        0x0608

bcdDevice        2.07

iManufacturer      1 ASK

iProduct          2 LoGO

iSerial            0

bNumConfigurations    1

Configuration Descriptor:

bLength          9

bDescriptorType   2

wTotalLength     0x0020

bNumInterfaces     1

bConfigurationValue  1

iConfiguration      0

bmAttributes        0x80

(Bus Powered)

MaxPower        300mA

Interface Descriptor:

bLength          9

bDescriptorType   4

bInterfaceNumber     0

bAlternateSetting    0

bNumEndpoints       2

bInterfaceClass     255 Vendor Specific Class

bInterfaceSubClass  255 Vendor Specific Subclass

bInterfaceProtocol  255 Vendor Specific Protocol

iInterface          0

Endpoint Descriptor:

bLength          7

bDescriptorType   5

bEndpointAddress  0x04 EP 4 OUT

bmAttributes        2

Transfer Type      Bulk

Synch Type        None

Usage Type        Data

wMaxPacketSize      0x0040 1x 64 bytes

bInterval           4

```

```

Endpoint Descriptor:

bLength          7

bDescriptorType 5

bEndpointAddress 0x84  EP 4 IN

bmAttributes     2

Transfer Type   Bulk

Sync Type       None

Usage Type      Data

wMaxPacketSize   0x0040  1x 64 bytes

bInterval        4

```

Nous voyons clairement la hiérarchie en place via l'indentation de la sortie de la commande `lsusb` et on constate que nous avons un descripteur de périphérique indiquant les ID `0x1fd3:0x0608`, un constructeur `ASK` et un produit `LoGO` (c'est un lecteur NFC). Nous avons un seul descripteur de configuration, référençant un descripteur d'interface de classe *Vendor Specific* et deux *Endpoints* (numérotés `4`), acceptant au maximum 64 octets. Remarquez que les *Endpoints* `0` ne sont pas listés, même s'ils sont bien là. Une commande équivalent pour FreeBSD (voir l'article dans le numéro 47 [5] si FreeBSD sur SBC vous intéresse) serait `usbconfig -v -d ugen2.4`, par exemple.

Le lecteur NFC ASK LoGO, comme d'autres périphériques, est un excellent sujet de démonstration, car les classes utilisées sont exactement celles qui nous intéressent : *Vendor Specific Class*, *Vendor Specific Subclass* et *Vendor Specific Protocol*. En d'autres termes, nous sommes seuls maîtres à bord et le système n'associera pas automatiquement de pilote générique (rattaché à une classe) à notre périphérique, exactement comme il le fait avec ce lecteur NFC, utilisable via la libNFC (qui repose sur la libUSB).

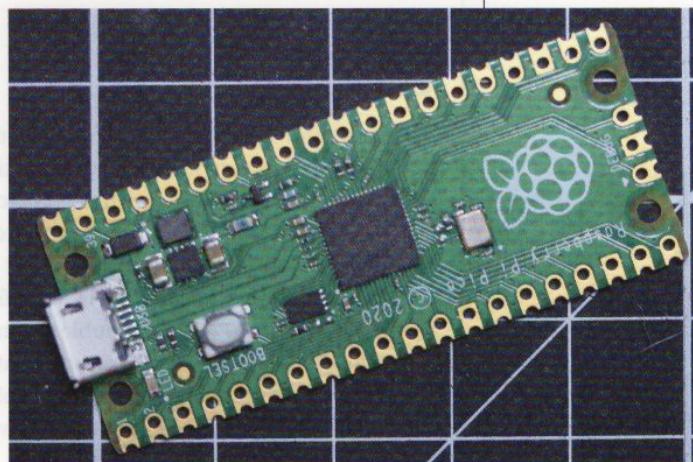

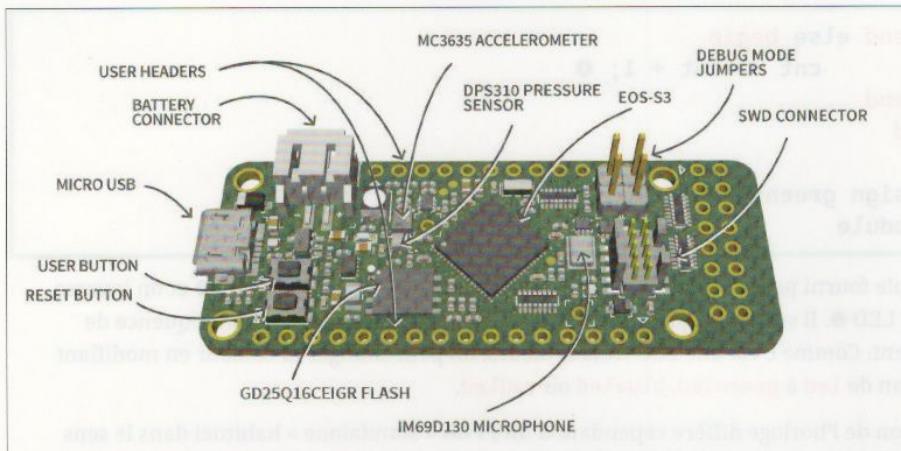

Le RP2040 est un microcontrôleur intégrant un contrôleur USB capable à la fois de fonctionner en mode hôte pour contrôler des périphériques et en mode périphérique pour s'interfacer avec un hôte comme un PC, un SBC ou même un smartphone.

## 2. PICO ET TINYUSB

Nous avons à présent toutes les connaissances nécessaires pour créer notre périphérique sur base Raspberry Pi Pico et savons ce que nous avons à faire. Une carte Raspberry Pi Pico est construite autour d'un microcontrôleur RP2040, lui-même basé sur un double cœur ARM Cortex M0+. Ce MCU intègre nombre de périphériques (GPIO, timers, UART, ADC, etc.) dont un contrôleur USB intégrant un PHY (pour *PHysical layer*, la partie chargée de la liaison physique dans un modèle ISO). Ce contrôleur peut être configuré comme hôte, pour gérer des périphériques ou comme un périphérique, pour apparaître comme tel lors d'une connexion et une énumération par un hôte, typiquement un PC ou un SBC.

Pour gérer ce contrôleur, le SDK [6] intègre une implémentation de la bibliothèque TinyUSB [4], accompagnée d'une poignée d'exemples dans `pico-examples/` [7]. Il sera cependant intéressant

## TinyUSB / Pico

– Créez vos périphériques USB avec Raspberry Pi Pico –

de consulter également le dépôt GitHub du projet TinyUSB [4], regroupant dans **examples/device** une myriade d'exemples bien plus étoffés que ceux du SDK Pico.

En débutant un nouveau projet Pico, la seule chose à faire pour bénéficier de ce support USB sera de bien spécifier les bibliothèques utilisées, sous la forme d'un bloc comme celui-ci dans son **CMakeLists.txt** :

```

target_link_libraries(${NAME}

pico_stlalib

tinyusb_device

tinyusb_board

)

```

Note : si vous rencontrez des problèmes lors de la compilation, signalant que certains fichiers sont introuvable ou manquants, vous avez probablement oublié de cloner les sous-modules Git du SDK Pi Pico. Vous rendre dans le répertoire **pico-sdk/** et vous plier d'un **git submodule update --init** réglera le problème (comme précisé dans la doc officielle [8], mais pas dans le **README.md** GitHub).

Profitons-en pour directement évoquer les deux fichiers sources qui seront utilisés :

```

add_executable(${NAME}

main.c

usb_descriptors.c

)

```

En effet, comme l'ensemble des exemples du SDK et de TinyUSB, nous séparons la partie configuration des descripteurs de la partie « active » du programme, puisque la première (**usb\_descriptors.c**) est créée une seule fois pour un périphérique et ne changera probablement plus, alors que la seconde (**main.c**) regroupe ce que fait effectivement le périphérique et sera mise au point au fil du temps.

Ce n'est pas tout, l'intégration de TinyUSB dans un projet, quel que soit le microcontrôleur utilisé, suppose de créer un « fichier de configuration »

pour la bibliothèque, appelée **tusb\_config.h**. Cette approche, peu conventionnelle, part du principe que la configuration de TinyUSB se fait via un ensemble de macros présentes dans ce fichier, qui est inclus automatiquement lors de la construction du *firmware* (cf. **pico-sdk/lib/tinyusb/hw/bsp/rp2040**). La façon la plus simple de composer ce fichier, et étant donné que la quasi-totalité des macros définies concerne le fonctionnement général de TinyUSB, est de tout simplement copier l'exemplaire présent dans les exemples Pico (dans **pico-examples/usb/device/dev\_hid\_composite**).

Une fois celui-ci placé en compagnie de **usb\_descriptors.c** et de **main.c** dans votre projet, éditez-le et ajustez simplement la partie **DEVICE CONFIGURATION**, et en particulier les valeurs associées aux macros **CFG\_TUD\_\***, ainsi :

```

//----- CLASS -----//

#define CFG_TUD_HID      0

#define CFG_TUD_CDC      0

#define CFG_TUD_MSC      0

#define CFG_TUD_MIDI     0

#define CFG_TUD_VENDOR   1

```

Ces macros, avec **TUD** pour *TinyUSB Device*, nous permettent de spécifier le nombre de périphériques (ou plus exactement d'interfaces) qui seront utilisés. L'exemple Pico concerne un périphérique composite (clavier, souris, gamepad) de classe USB-HID avec, donc, **CFG\_TUD\_HID** à 1. Mais nous souhaitons travailler « hors classe » et passons donc cette macro à 0 pour mettre **CFG\_TUD\_VENDOR** à 1.

Je n'aime pas particulièrement cette façon de structurer du code et d'avoir, en dur, une configuration et un fichier d'entête avec un nom imposé, car inclus

automatiquement. Mais je suppose que c'est là la conséquence directe d'avoir à gérer presque 70 microcontrôleurs différents (jetez un œil à [pico-sdk/lib/tinyusb/hw/bsp](#)) dans un unique framework.

## 2.1 Une simple LED : les descripteurs

Ce point de configuration réglé, nous pouvons à présent nous pencher sur [usb\\_descriptors.c](#) qui, comme le nom l'indique, contient tout le nécessaire pour définir les descripteurs de notre futur périphérique. Fournir ces descripteurs à l'hôte se fait en définissant des fonctions *callback* appelées automatiquement par l'implémentation TinyUSB qui, elles-mêmes, utilisent des structures de données que nous devons créer.

Nous débutons donc notre code avec quelques déclarations :

```

#include "bsp/board.h"

#include "tusb.h"

enum {

STRING_DESC = 0,

STRING_DESC_MANUFACTURER,

STRING_DESC_PRODUCT,

STRING_DESC_VENDOR,

STRING_DESC_SERIAL

};

char const *string_desc_arr[] = {

(const char[]){0x09, 0x04}, // 0: English (0x0409)

"Hackable Magazine", // 1: Manufacturer

"Test device", // 2: Product

"Test interface", // 3: (vendor) interface

"12345678", // 4: serial

};

static uint16_t _desc_str[32];

```

L'énumération nous permet d'avoir un peu de souplesse, dans le sens où il nous suffira de l'ajuster si l'ordre des chaînes change, mais la partie la plus importante est, bien entendu, le tableau de pointeurs vers des chaînes de caractères, agencées dans le même ordre que l'énumération. Ceci servira de base pour créer le corps de la fonction *callback tud\_descriptor\_string\_cb()*, chargé de retourner les chaînes de caractères en question à la demande de l'hôte (requête [GET STRING DESCRIPTOR](#)):

```

uint16_t const* tud_descriptor_string_cb(uint8_t index, uint16_t langid)

{

uint8_t chr_count;

const char* str = string_desc_arr[index];

uint8_t i;

if (index == STRING_DESC) {

memcpy(&_desc_str[1], string_desc_arr[0], 2);

```

## TinyUSB / Pico

- Créez vos périphériques USB avec Raspberry Pi Pico -

```

chr_count = 1;

} else {

// ASCII en UTF-16

if (!(index < sizeof(string_desc_arr) / sizeof(string_desc_arr[0]))) {

return NULL;

}

chr_count = strlen(str);

if (chr_count > 31) chr_count = 31;

for (i = 0; i < chr_count; i++) {

_desc_str[1 + i] = str[i];

}

}

// first byte is length (including header), second byte is string type

// (Endian)

_desc_str[0] = (TUSB_DESC_STRING << 8) | (2 * chr_count + 2);

return _desc_str;

}

```

Cette fonction retourne un pointeur (qui doit être valide le temps de la transaction) vers un tableau formant un descripteur de chaînes, qui n'est qu'un joli nom pour un groupe de caractères (31 au maximum) sur 16 bits précédés d'un mot combinant un type et une taille (attention à l'*endianess*, ou au « boutisme » en horrible français). Notez que `_desc_str[]` est un tableau de `uint16_t`, car l'encodage des chaînes en USB est de l'UTF-16 et non de l'ASCII ou de l'UTF-8. Pourquoi ? Parce que Microsoft a joué de ses tentacules lors de la création des spécifications USB et qu'à cette époque Windows avait choisi UTF-16LE/UCS-2 (*little endian*). Cet encodage surprenant explique également que nous devons procéder à une conversion, assez simple, en attribuant 16 bits (2 octets) pour chaque caractère `char` dans une boucle `for`. Notez que rien ne vous empêche de directement spécifier des tableaux avec des données en UTF-16LE pour ajouter des caractères rigolos dans les chaînes (voir mon article dans Linux Magazine 269 [9] torturant abjectement un adaptateur USB/série FTDI FT232R).

Dans les grandes lignes donc, tout ce que fait cette fonction est de retourner un

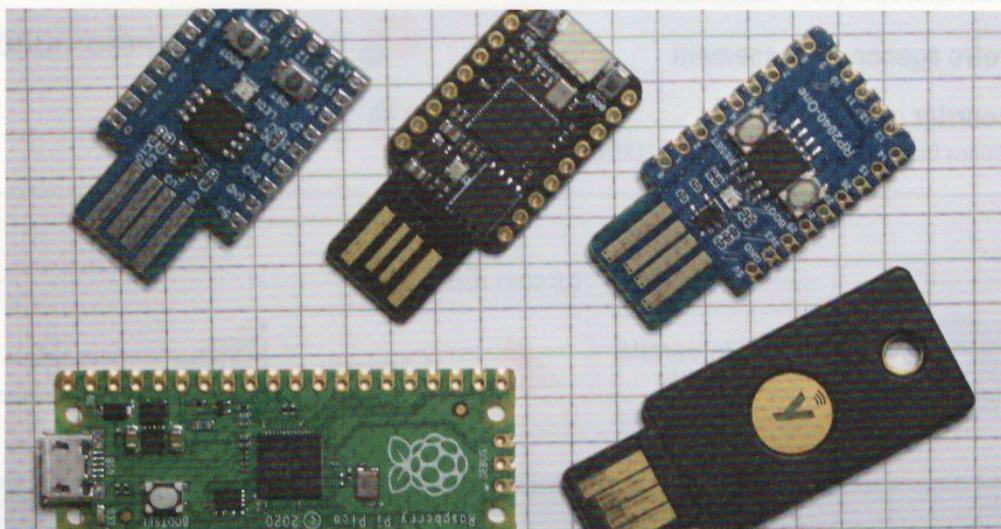

Une Raspberry Pi Pico et une tripotée de LED RGB adressables de 8 mm... Je vous laisse imaginer le nombre de possibilités et de projets qu'il devient possible d'envisager, dès lors qu'on sait transformer la carte en un véritable périphérique USB...

## MICROCONTRÔLEURS & ARDUINO

pointeur vers des données converties et complétées d'un entête, sur la base d'un index fourni en argument. La question est donc : quel index ? Et la réponse est liée avec l'énumération du début. En effet, c'est dans le descripteur de périphérique (structure `tusb_desc_device_t`) que nous faisons correspondre les chaînes qui peuvent être demandées avec les données pointées dans notre `string_desc_arr[]`. Voici notre descripteur :

```

tusb_desc_device_t const desc_device = {

.bLength          = sizeof(tusb_desc_device_t),

.bDescriptorType = TUSB_DESC_DEVICE,

.bcdUSB           = 0x0210,

.bDeviceClass     = TUSB_CLASS_MISC,

.bDeviceSubClass  = MISC_SUBCLASS_COMMON,

.bDeviceProtocol  = MISC_PROTOCOL_IAD,

.bMaxPacketSize0 = CFG_TUD_ENDPOINT0_SIZE,

.idVendor          = 0x1209,

.idProduct         = 0x0001,

.bcdDevice         = 0x0100,

.iManufacturer     = STRING_DESC_MANUFACTURER,

.iProduct          = STRING_DESC_PRODUCT,

.iSerialNumber     = STRING_DESC_SERIAL,

.bNumConfigurations = 0x01

};

```

Bon nombre de valeurs proviennent de macros définies par TinyUSB, notre `tusb_config.h` ou la présence de la source C. C'est le cas par exemple de `CFG_TUD_ENDPOINT0_SIZE`, valant 64 et correspondant à la taille des données maximales pour les *EndPoints* 0, mais aussi, et surtout les index pour les chaînes précédemment décrites. Le mécanisme est relativement simple, puisque lorsqu'un `GET DEVICE DESCRIPTOR` arrive, nous retournerons ces informations qui seront réutilisées par l'hôte pour demander les chaînes en question (que nous fournissons via `tud_descriptor_string_cb()`). Mais, je pense, la partie la plus importante concerne la classe et la sous-classe du périphérique, ainsi que les ID identifiant le matériel. Ici, j'utilise `1209:0001`, correspondant à un *VendorID* réservé pour les projets *open hardware*, avec un *ProductID* entre `0000` et `0FFF`.

Notez que ces identifiants sont originellement la propriété de la société InterBiometrics et que les droits sur cet identifiant ont été repris par `pid.codes` [10] dans le but de fournir à la communauté de créateurs, développeurs, *startups* et hobbyistes des ID USB légitimement utilisables. `pid.codes` maintient un registre des identifiants de périphériques pour les projets *open source* et *open hardware*, et il est possible de soumettre une demande pour enregistrer un projet gratuitement (mais sous condition). Ici, bien sûr, nous n'avons pas cette prétention, mais les ID produits `0000` à `0010` sont réservés pour les tests, sans risquer un conflit avec un pilote préexistant. C'est donc ce que nous utilisons ici, `1209:0001`.

Associée avec cette structure arrive une autre fonction *callback*, retournant tout simplement un pointeur vers `desc_device` en réponse à une requête `GET DEVICE DESCRIPTOR` :

```

uint8_t const* tud_descriptor_device_cb(void)

{

return (uint8_t const*) &desc_device;

}

```

## TinyUSB / Pico

– Créez vos périphériques USB avec Raspberry Pi Pico –

Nous avons presque fini, il ne nous reste plus qu'à nous charger du descripteur de configuration regroupant, avec TinyUSB, également les descripteurs d'interface et d'*EndPoints*. Pour cela, nous aurons besoin de quelques macros supplémentaires :

```

#define CFG_TOT_LEN (\

TUD_CONFIG_DESC_LEN + \

(CFG_TUD_VENDOR * TUD_VENDOR_DESC_LEN))

#define EPNUM_VENDOR_OUT 0x01

#define EPNUM_VENDOR_IN  0x81

```

Ceci nous permettra de calculer la taille du descripteur (variant en fonction des interfaces présentes et de leur classe) et de spécifier les numéros des *Endpoints* que nous comptons utiliser. Notez que ce numéro est ici **1**, à la fois pour *IN* et *OUT*, mais que la macro **EPNUM\_VENDOR\_IN** précise **0x81**, correspondant en réalité à **0x01** avec le bit de poids le plus fort à 1 pour signifier un *EndPoint IN*.

Ces macros peuvent ensuite être utilisées pour créer un tableau d'octets regroupant la réponse à une requête **GET\_CONFIGURATION\_DESCRIPTOR** qui, contrairement à ce que le nom laisse penser, informe également l'hôte sur le/les descripteur(s) d'interface et les *Endpoints* :

```

uint8_t const desc_fs_configuration[] = {

TUD_CONFIG_DESCRIPTOR(

1,           // numéro de configuration

1,           // nombre d'interfaces

0,           // index chaîne

CFG_TOT_LEN, // taille totale

0x00,         // attribut

100),        // puissance en mA

TUD_VENDOR_DESCRIPTOR(

0,           // numéro d'interface

STRING_DESC_VENDOR, // index chaîne

EPNUM_VENDOR_OUT,   // adresse EP Out

EPNUM_VENDOR_IN,   // adresse EP In

32),          // taille données EP

};

```

Deux macros (encore ?!) fournies par **pico-sdk/lib/tinyusb/src/device/usbd.h** permettent de formater les données en correspondance avec le standard, tout en nous permettant d'utiliser des arguments intelligibles. Les commentaires ajoutés devraient suffire, tout en précisant que le numéro de configuration (ici, **1**) correspond au *bConfigurationValue* du protocole, un paramètre utilisé par l'hôte pour demander l'activation de cette configuration, mais que pour **TUD\_VENDOR\_DESCRIPTOR**, et donc l'interface fille de cette configuration, le numéro (*bInterfaceNumber*) est censé débuter à **0** et s'incrémenter pour chaque interface supplémentaire.

Remarquez **STRING\_DESC\_VENDOR** qui est un index de chaîne de caractères, comme pour le descripteur de périphérique. Cette chaîne correspond à la ligne **iInterface** dans la sortie de **lsusb** et sera potentiellement très utile si vous étayez ce premier code en multipliant les interfaces.

Et finalement, pour répondre au **GET CONFIGURATION DESCRIPTOR**, nous avons l'indispensable fonction *callback* associée :

```

uint8_t const* tud_descriptor_configuration_cb(uint8_t index)

{

return desc_fs_configuration;

}

```

Ce qui clôt notre **usb\_descriptors.c**.

Il faut avouer que ceci n'est pas forcément ce qu'il y a de plus simple à configurer, même en partant d'une base existante ou des exemples fournis avec TinyUSB. En vérité, la quasi-absence de documentation, si ce n'est les commentaires dans les **.h**, n'aide pas à l'affaire. Les mauvaises langues diront sans doute que ceci n'a, non seulement, rien de bien étonnant, mais n'est pas sans rappeler un autre projet également financé par Adafruit, la *NeoPixel Library*, rendue depuis quasi-obsolète par FastLED [11], d'un tout autre niveau de qualité. Cependant, le fait est de constater que maintenir un tel projet pour un grand nombre de MCU n'est pas facile et nécessite quelques raccourcis (et macros, plein de macros). Ce qui, toutefois, n'excuse pas le fait d'oublier totalement l'existence de choses comme Doxygen, qui rendrait cela tellement plus agréable à prendre en main.

## 2.2 Une simple LED : main()

Le plus gros du travail est fait et je pèse mes mots. Tout ce qu'il nous reste à faire est de gérer les requêtes qui nous parviennent et réagir en conséquence. Étant donné la manière donc nous avons configuré nos descripteurs et les tâches que va effectuer pour nous TinyUSB, ceci s'avère étonnamment simple. En effet, les requêtes peuvent être grossièrement classées en trois catégories :

- Les requêtes standard qui sont décrites dans les spécifications USB et sont utilisées pour obtenir des informations d'un périphérique, gérer les configurations, configurer les interfaces et les *EndPoints*, etc. Le destinataire de ce type de requêtes peut être le périphérique lui-même, une interface ou un *EndPoint*. Tout ceci est géré pour nous par TinyUSB, du moins pour un usage courant (voir [pico-examples/usb/device/dev\\_lowlevel/](#) pour quelque chose de plus spécifique).

- Les requêtes de classe sont structurées selon les spécifications d'une classe de périphérique et d'interface. C'est la fameuse universalité qui permet à des pilotes de gérer n'importe quel matériel USB répondant aux spécifications, indépendamment du constructeur. Ceci ne nous concerne pas ici.

- Les requêtes dites « Vendor » qui sont totalement hors spécifications. Dans ce cas, qui est le nôtre, le constructeur (nous) choisit la manière dont les échanges sont structurés et la signification des données échangées.

Nous avons le champ libre et décidons donc d'utiliser des transactions (ou transferts) de contrôle, généralement destinées à l'exécution de commandes ou la consultation d'un état. C'est précisément ce qu'il nous faut, puisque nous voulons contrôler une simple LED et éventuellement

## TinyUSB / Pico

– Créez vos périphériques USB avec Raspberry Pi Pico –

obtenir un octet d'état (ceci est très secondaire dans notre exemple). Un transfert de contrôle peut avoir jusqu'à trois étapes : *setup* qui est la requête elle-même, *data* pour échanger des données et *status* pour rendre compte du déroulement de toute l'opération.

Nous n'avons pas de données à échanger à proprement parler, du moins pas au sens USB du terme, et l'étape *setup* nous suffira pour transmettre une commande (**bRequest**) sur 8 bits, accompagnée d'une valeur (**wValue**) sur 16 bits. Valeur qu'il faut plutôt voir comme un argument ou une option, que comme une donnée transmise.

Nous décidons que notre protocole sera constitué de deux commandes, une pour changer l'état de la LED (**0x08**) et une autre (**0x03**) pour obtenir une valeur d'état. Nous concrétisons ces choix dès le début de notre **main.c** :

```

#include <stdlib.h>

#include <string.h>

#include <bsp/board.h>

#include <pico/stdlib.h>

#include <tusb.h>

// GPIO led

#define DALED 18

// commandes

#define CMD_GET_STATUS 3

#define CMD_SET_LED 8

// valeur d'état

static uint8_t status = 0x42;

```

Une fois n'est pas coutume, les échanges et transactions avec TinyUSB prennent la forme de fonctions *callback* à implémenter. Si nous ne le faisons pas, TinyUSB se chargera d'opter pour un comportement par défaut, qui est le plus souvent de signaler une erreur lors des opérations. Dans notre cas, nous implémentons **tud\_vendor\_control\_xfer\_cb()**, la fonction appelée lors de la réception d'une requête de type *VENDOR* :

```

bool tud_vendor_control_xfer_cb(

uint8_t rhport,

uint8_t stage,

tusb_control_request_t const* request)

{

// étape setup ?

if (stage != CONTROL_STAGE_SETUP)

return true;

// requête vendor ?

if (request->bmRequestType_bit.type == TUSB_REQ_TYPE_VENDOR) {

switch (request->bRequest) {

// contrôle de la led

case CMD_SET_LED:

// tout sauf 0 = led allumée

if (request->wValue != 0)

```

## MICROCONTRÔLEURS & ARDUINO

```

gpiod_put(DALED, 1);

else

gpiod_put(DALED, 0);

return tud_control_status(rhport, request);

// demande d'état

case CMD_GET_STATUS:

return tud_control_xfer(rhport, request,

(void*) &status, sizeof(status));

}

}

return false;

}

```

Le cœur de la fonction tient dans un simple `switch/case` basé sur le contenu de `bRequest`, la commande reçue, et `wValue`, la valeur en argument. Nous utilisons cette valeur pour déterminer si nous devons allumer ou éteindre la LED, à l'aide d'un simple `gpiod_put()`. Dans le cas de la requête de contrôle de la LED, nous n'oubliions pas de transmettre, en retour, un paquet d'état pour accuser réception de la commande. Pour une requête de demande d'état de notre périphérique, nous répondons avec un autre transfert de contrôle constituant la réponse à la demande initiale, en spécifiant un pointeur vers la donnée et une taille. TinyUSB se charge du reste. Notez que notre fonction `callback` doit retourner `true` en cas de succès et `false` en cas d'erreur, ce qui aura pour effet de provoquer une erreur USB côté hôte.

C'est tout. Ceci suffit à implémenter notre projet et à créer un périphérique avec une LED, contrôlée en USB. Bien entendu, il nous faut un `main()` et faire en sorte que TinyUSB soit non seulement initialisé correctement, mais ait également l'opportunité de faire son travail :

```

int main(void)

{

// initialisation TinyUSB

board_init();

tusb_init();

// initialisation GPIO/led

gpiod_init(DALED);

gpiod_set_dir(DALED, GPIO_OUT);

gpiod_put(DALED, 0);

// boucle principale

while (1) {

// gestion TinyUSB

tud_task();

}

return 0;

}

```

En l'absence d'OS (typiquement FreeRTOS sur Pico), nous devons continuellement appeler `tud_task()` pour gérer les transactions et donc provoquer les appels aux fonctions `callback`. Il faudra donc faire très attention de ne pas perturber ce *polling* en utilisant, par ailleurs, des

fonctions bloquantes. Si ceci est un problème pour votre projet, le plus simple est d'utiliser un RTOS et de faire de ce *polling* une tâche s'exécutant en parallèle de vos fonctions potentiellement bloquantes. Une autre approche est de jouer avec le multi-tâche et les deux coeurs du RP2040.

### 2.3 Un petit client avec libUSB

Pour tester notre petite création et après avoir compilé le code et flashé la Pico, nous devons créer un code « client ». Cependant, si vous utilisez GNU/Linux (sur PC ou Pi)

pour vos développements Pico, vous pouvez déjà avoir une petite idée du bon fonctionnement de l'ensemble, puisque le système aura immédiatement détecté le périphérique après son reset (sortie de `dmesg`) :

```

new full-speed USB device number 23 using xhci_hcd

unable to get BOS descriptor or descriptor too short

New USB device found, idVendor=1209,

idProduct=0001, bcdDevice= 1.00

New USB device strings: Mfr=1, Product=2,

SerialNumber=4

Product: Test device

Manufacturer: Hackable Magazine

SerialNumber: 12345678

```

C'est bon signe, mais pour aller plus loin, nous devons créer un programme. Plusieurs approches sont envisageables, allant du script Python au pilote noyau, mais nous opterons ici pour une utilisation en espace utilisateur via un code en C reposant sur la libUSB (paquet `libusb-1.0-0-dev`). Nous débutons notre programme en déclarant macros et variables :

```

#include <stdlib.h>

#include <stdio.h>

#include <unistd.h>

#include <err.h>

#include <libusb.h>

#define VID 0x1209

#define PID 0x0001

#define CMD_SET_LED 8

int main (int argc, char**argv)

{

```

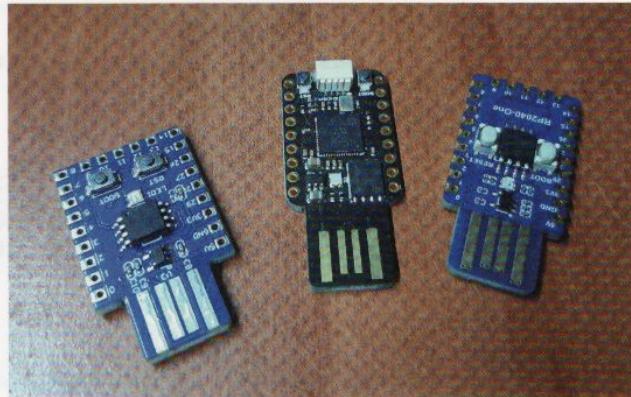

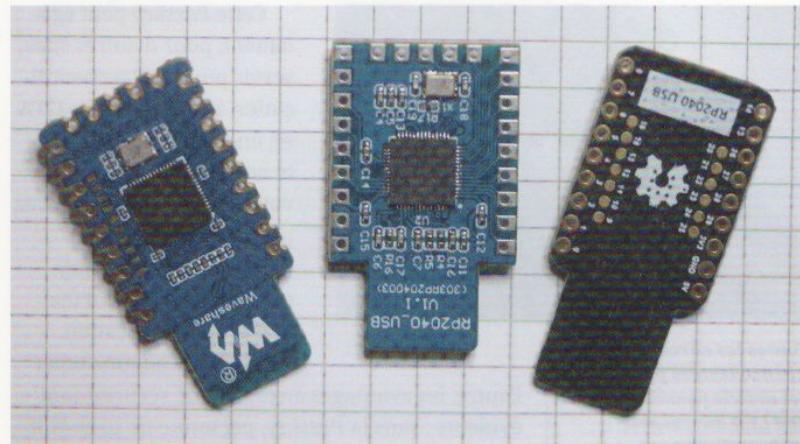

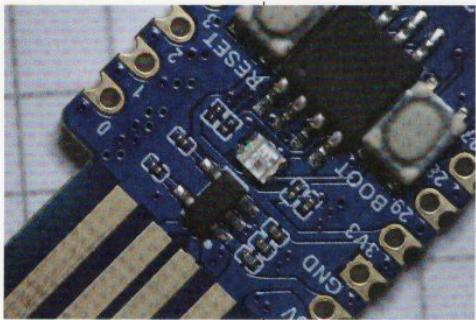

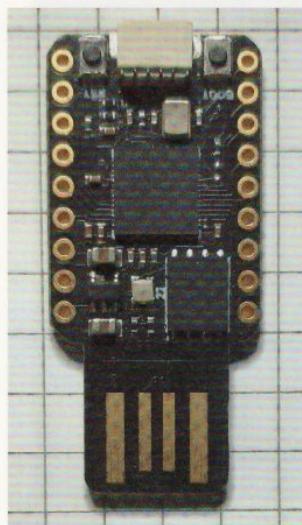

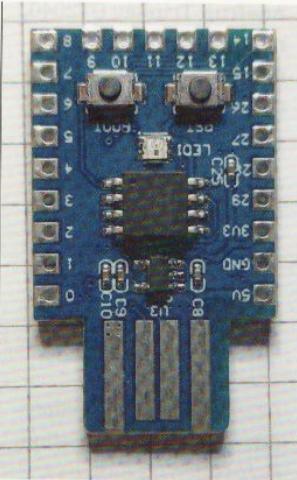

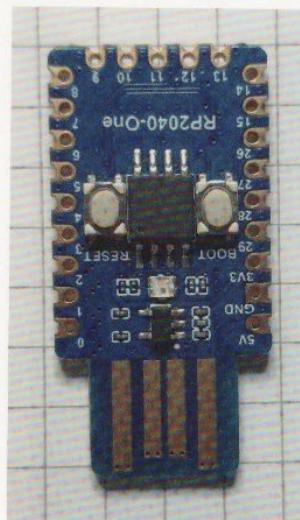

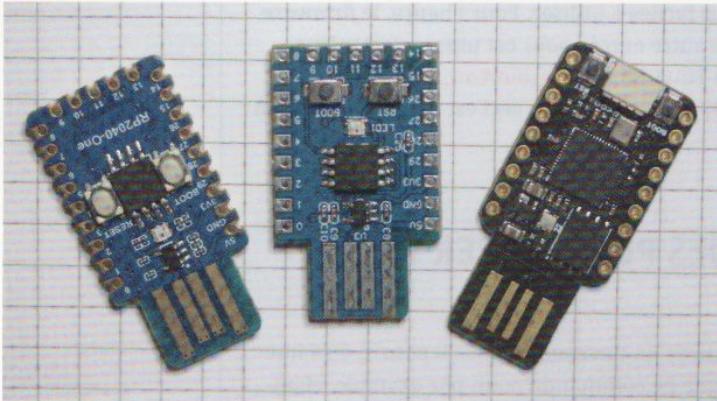

Une Pico standard fera parfaitement l'affaire pour utiliser TinyUSB en mode périphérique, mais certaines cartes, comme cette petite sélection acquise sur AliExpress, se présentent sous un format bien plus adapté. Je n'ai pas trouvé, cependant, d'équivalent décliné en USB-C, dommage.

## MICROCONTRÔLEURS & ARDUINO

```

libusb_context *ctx;

libusb_device_handle *handle;

int ret;

uint8_t bmRequestType = (

LIBUSB_REQUEST_TYPE_VENDOR

| LIBUSB_RECIPIENT_INTERFACE

| LIBUSB_ENDPOINT_OUT);

uint8_t bRequest = CMD_SET_LED;

uint16_t wValue = 0x00ff;

uint16_t wIndex = 0;

unsigned char *data = NULL;

uint16_t wLength = 0;

```

Contrairement à TinyUSB, la libUSB n'utilise pas une structure pour composer une requête, mais un ensemble d'arguments à passer aux fonctions. De plus, le type de requête est assemblé à partir d'un groupe de macros avec ici, dans l'ordre, un type « Vendor », à destination d'une interface et d'un *EndPoint OUT*. La requête est **CMD\_SET\_LED (0x08)** et la valeur initialement définie à **0x00ff**, mais n'importe quelle valeur supérieure à 0 fera l'affaire. Notez que cette requête, comme détaillée précédemment, n'embarque pas de données (\***data** est **NULL** et la taille est zéro).

Nous poursuivons en initialisant la libUSB et en recherchant notre périphérique par ces ID :

```

if ((ret = libusb_init(&ctx)) < 0)

err(ret, "LibUSB initialisation error");

if ((handle = libusb_open_device_with_vid_pid(ctx, VID, PID)) == NULL) {

libusb_exit(ctx);

errx(EXIT_FAILURE, "Unable to find device");

}

```

Immédiatement ensuite, nous envoyons notre première requête pour allumer la LED :

```

printf("led ON\n");

if ((ret = libusb_control_transfer(handle, bmRequestType,

bRequest, wValue, wIndex, data, wLength, 2000)) < 0)

warnx("libusb_control_transfer() failed");

```

puis marquons une petite pause avant de l'éteindre, en réutilisant les mêmes informations, mais en changeant la valeur :

```

usleep(1000*500);

wValue = 0x0000;

printf("led OFF\n");

if ((ret = libusb_control_transfer(handle, bmRequestType,

bRequest, wValue, wIndex, data, wLength, 2000)) < 0)

warnx("libusb_control_transfer() failed");

```

Et terminons le programme proprement :

```

libusb_close(handle);

libusb_exit(ctx);

return(EXIT_SUCCESS);

}

```

Ce code, que nous stockons dans un `main.c` pourra être compilé avec `gcc main.c -o picoledusb `pkg-config --cflags --libs libusb-1.0``, même s'il est plus judicieux de créer un `Makefile` pour l'occasion. Avec une configuration par défaut, il est fort probable que vous soyez obligé d'utiliser `sudo` (ou `doas`) pour l'exécution, qui devrait donc allumer et éteindre la LED avec une timide sortie à l'écran. L'alternative à ce problème de permissions est de composer rapidement une règle `udev` comme `SUBSYSTEMS=="usb", ATTRS{idVendor}=="1209", MODE=="0660", GROUP="plugdev"`, à glisser dans un `/etc/udev/rules.d/picousb.rules` par exemple (et mettre l'utilisateur courant dans le groupe `plugdev` si ce n'est pas déjà le cas).

## CONCLUSION