CPPAP : K92470

## ACTUALITÉ / SDR / RADIO

Retour sur les conférences European GNU Radio Days 2024 et l'annonce de **GNU Radio 4.0** p.04

## FPGA / FRAMEWORK

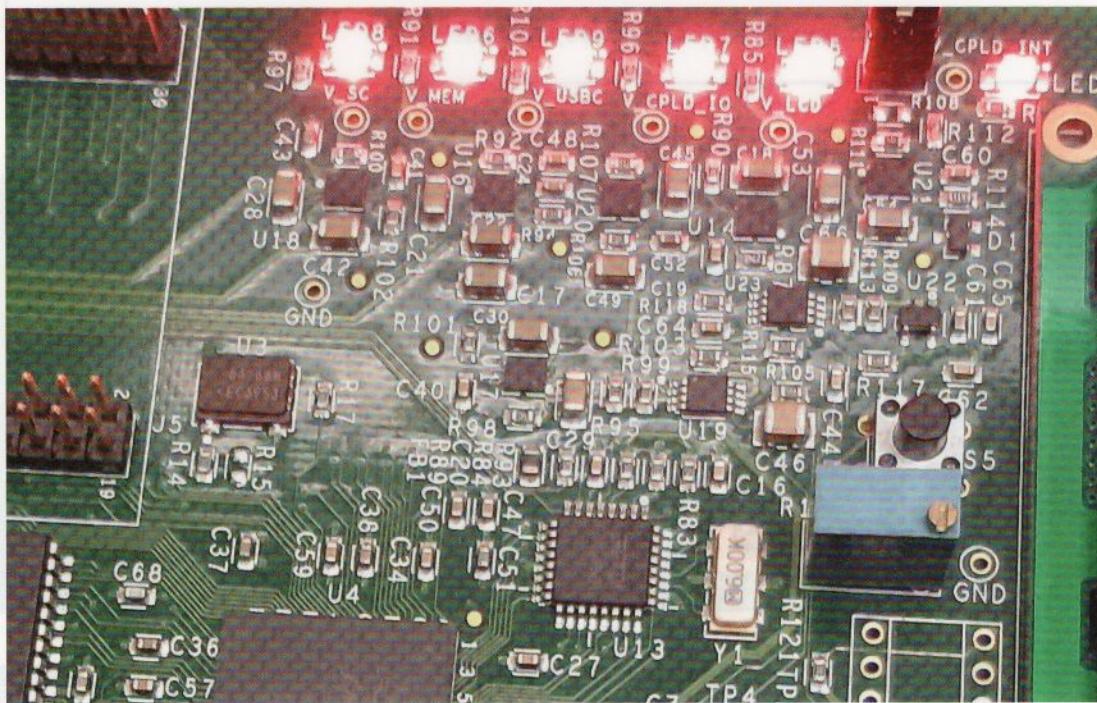

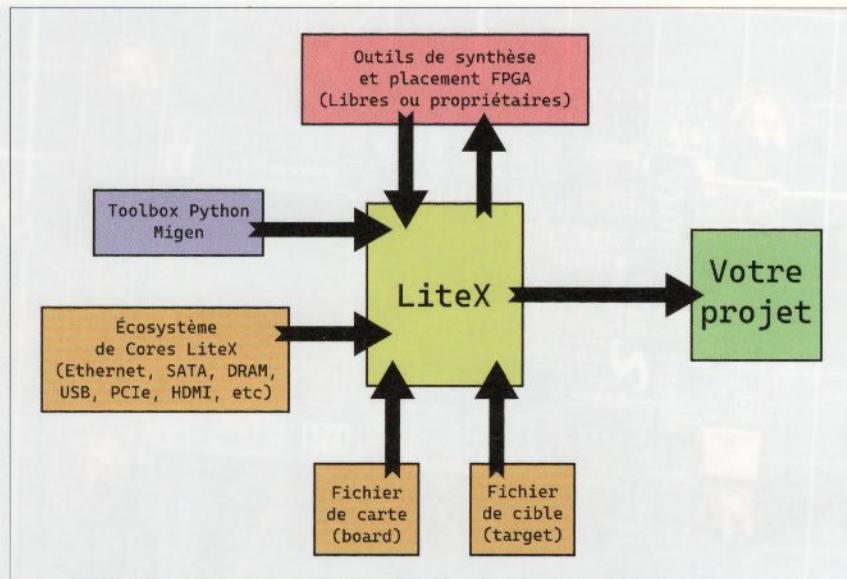

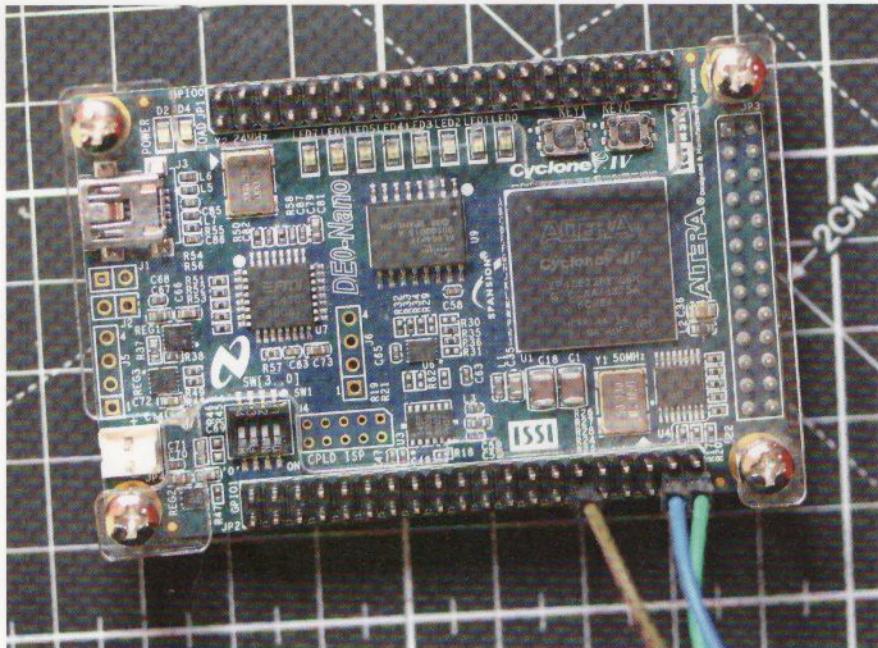

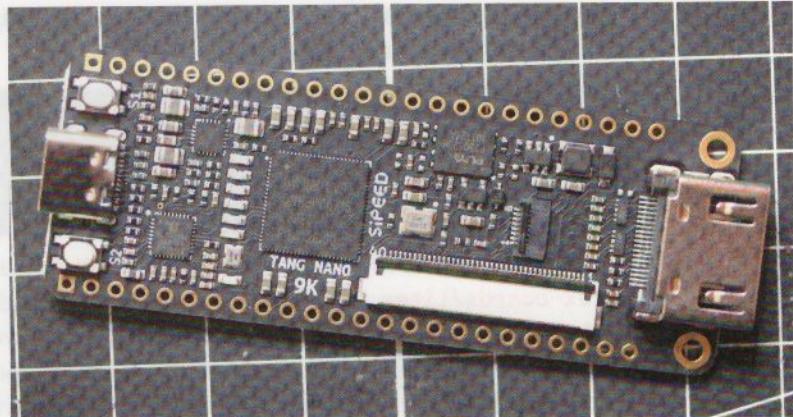

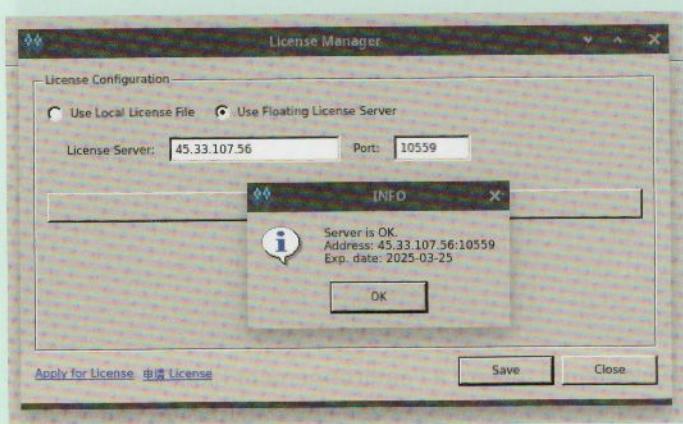

Créez vos périphériques et SoC sur FPGA sans une seule ligne de VHDL/Verilog grâce à LiteX p.68

**RASPBERRY PI / DÉCENTRALISATION / PEER-TO-PEER**

Comment échapper à la surveillance et protéger votre vie privée ?

**ANONYMISEZ ET SÉCURISEZ VOS CONNEXIONS ...AVEC I2P** p.38

- Comprenez les limitations des VPN

- Rejoignez l'Internet invisible

- Transformez votre RPi en routeur I2P

- Créez des tunnels entre vos machines

## TEST / OUTILS

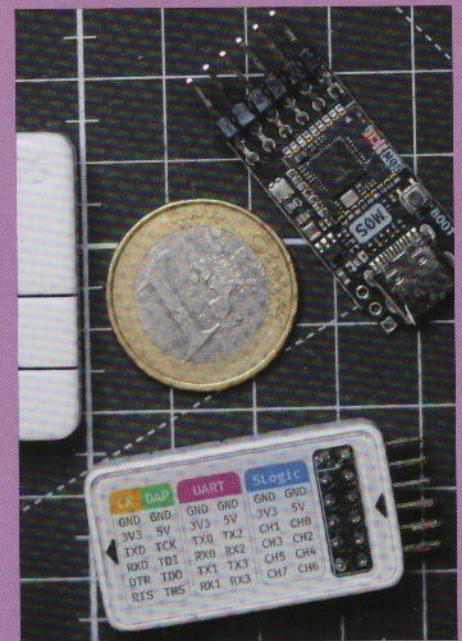

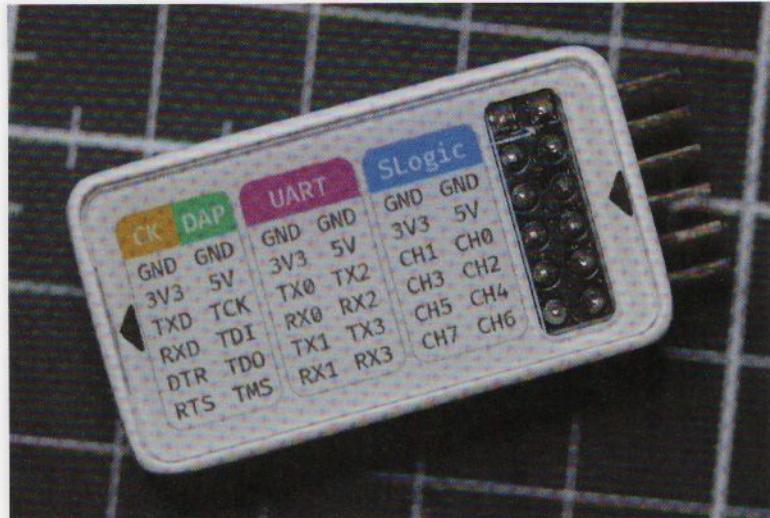

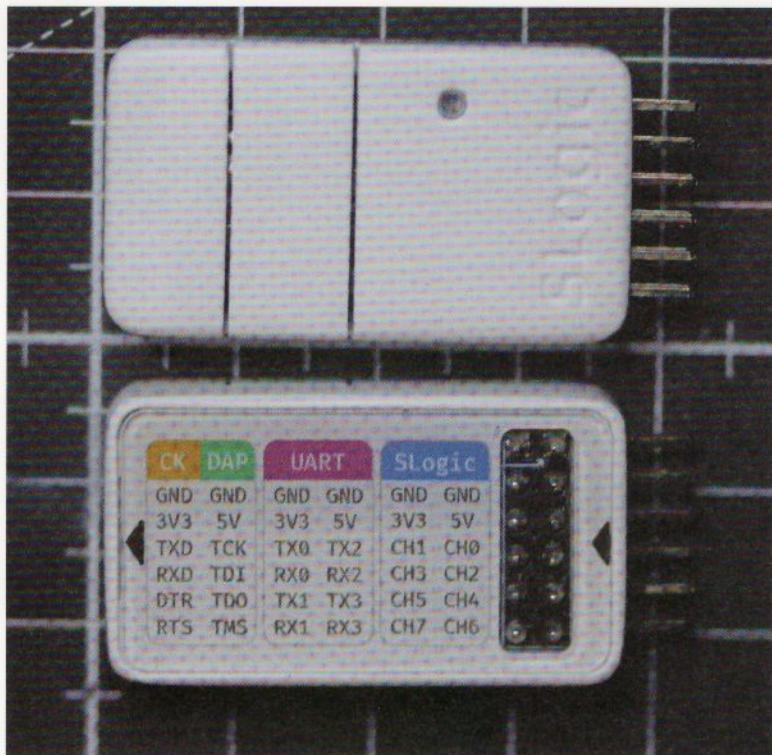

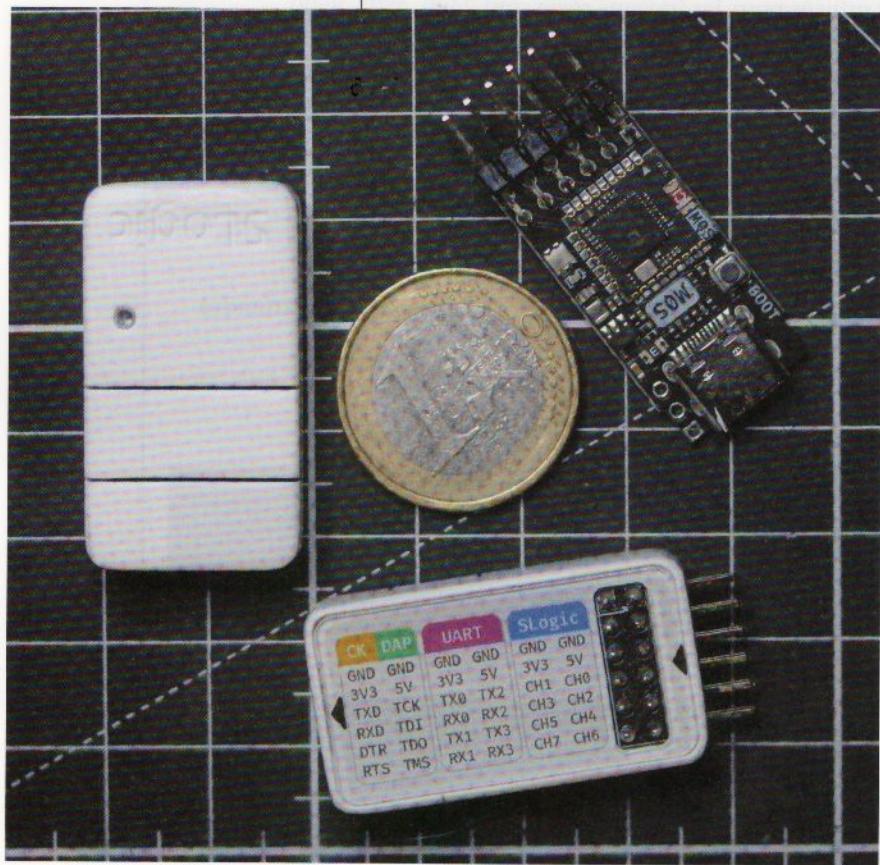

**SLogic Combo 8** : Adaptateurs USB/série, programmeur JTAG et analyseur logique en un seul outil p.58

## USB / MCU / GNSS

Utilisez un **microcontrôleur Cypress FX2LP** pour créer un récepteur radio logiciel USB p.88

## RISC-V / OPENBSD

Installez et configurez un système sécurisé sur une **carte MangoPi MQ-Pro D1** à moins de 30 € p.18

ÉDITION

#4

OPEN SOURCEZ

VOS SOLUTIONS IT

# OPEN SOURCE EXPERIENCE

PARIS

04 & 05

DÉCEMBRE 2024

- PALAIS

DES CONGRÈS

90 EXPOSANTS 100 CONFÉRENCES 125 SPEAKERS

Inscription gratuite pour les conférences et le salon

sur [www.opensource-experience.com](http://www.opensource-experience.com) avec le code invitation P-LINUOSXP24

Suivez-nous  #OSXP2024

Un événement

organisé par  infoprodigital

NOUVEAU

CETTE ANNÉE !

Aux mêmes dates

et lieu que

DEVOPS REX

LA CONFÉRENCE DEVOPS

FRANCOPHONE

100% retour d'expérience

# ÉDITO

Ils l'ont fait !

Au moment où je rédige ceci, le Super Heavy Booster de Starship vient tout juste de se poser délicatement sur Mechazilla, la tour de lancement équipée de « bras » et située à Starbase, la plateforme de lancement de SpaceX à Boca Chica, Texas. Voir ce moment réellement historique et presque irréel, en direct, est un événement en soi. C'est être témoin de la progression technologique humaine, qui, on ne peut le nier, ne cesse de s'accélérer.

L'impact de ces images est évident, même pour une personne n'ayant aucune affinité ou connaissance dans le domaine spatial, aéronautique ou technologique de manière générale. Mais elles sont encore plus impressionnantes lorsqu'on se doute du nombre incroyable de problématiques à régler pour arriver à un tel résultat. Je parle, bien évidemment, d'un point de vue électronique et informatique. La masse de calculs nécessaires et la précision à atteindre dépassent presque l'entendement. Imaginez un instant la tâche à accomplir : poser un cylindre de 70 mètres de haut et de 9 mètres de diamètre en le positionnant à l'aide de trois moteurs Raptor (sur les 33 utilisés au lancement), montés sur un cardan en assurant l'orientation. Le tout après une descente de quelque 70 kilomètres avec un pic de vitesse à 4000 km/h.

C'est un exploit d'ingénierie, bien sûr, tout autant que scientifique, mathématique, physique... Mais pour moi, c'est aussi, et surtout, une démonstration de ce que permettent de faire les technologies informatiques, électroniques et embarquées aujourd'hui.

Je ne sais plus quel scientifique (peut-être Carl Sagan) s'est vu poser la question de savoir si, du fait d'avoir la connaissance nécessaire à comprendre le mécanisme de formation des arcs-en-ciel, cela rendait le phénomène moins appréciable, moins magique. Chose à quoi il a répondu que non, bien au contraire, le fait de savoir, de comprendre, ne fait que rendre le moment encore plus unique et merveilleux.

Il en va de même ici. Tenter d'imaginer, en plus du spectacle époustouflant, le nombre de systèmes, de sous-systèmes, de capteurs, de MEMS et la masse de données à traiter, avec des contraintes physiques énormes, donne le vertige. Et pourtant, pourtant... ils l'ont fait. Et nous, nous vivons tous une époque incroyable...

Denis Bodor

## Hackable Magazine

est édité par Les Éditions Diamond

BP 20142 - 67602 SELESTAT CEDEX - France

E-mail : [lecteurs@hackable.fr](mailto:lecteurs@hackable.fr) -

Service commercial : [cial@ed-diamond.com](mailto:cial@ed-diamond.com)

Sites : [hackable.fr](http://hackable.fr) - [ed-diamond.com](http://ed-diamond.com)

Directeur de publication : Arnaud Metzler

Rédacteur en chef : Denis Bodor

Réalisation graphique : Kathrin Scali

Régie publicitaire :

Valérie Fréchard - Tél. : 03 67 10 00 27

Service abonnement : Les Éditions Diamond

BP 20142 - 67602 SELESTAT CEDEX, France,

Tél. : 03 67 10 00 20

Impression : Westermann Druck | PVA,

Braunschweig, Allemagne

Distribution France :

(uniquement pour les dépositaires de presse)

MLP Réassort : Plate-forme de Saint-

Barthélémy-d'Anjou. Tél. : 02 41 27 53 12

Plate-forme de Saint-Quentin-Fallavier.

Tél. : 04 74 82 63 04

Service des ventes :

Abomarque - Tél. : 06 15 46 15 88

IMPRIMÉ en Allemagne - PRINTED in Germany

Dépôt légal : À parution

N° ISSN : 2427-4631

CPPAP : K92470

Périodicité : bimestriel - Prix de vente : 14,90 €

La rédaction n'est pas responsable des textes, illustrations et photos qui lui sont communiqués par leurs auteurs. La reproduction totale ou partielle des articles publiés dans Hackable Magazine est interdite sans accord écrit de la société Les Éditions Diamond.

Sauf accord particulier, les manuscrits, photos et dessins adressés à Hackable Magazine, publiés ou non, ne sont ni rendus ni renvoyés. Les indications de prix et d'adresses figurant dans les pages rédactionnelles sont données à titre d'information, sans aucun but publicitaire. Toutes les marques citées dans ce numéro sont déposées par leur propriétaire respectif. Tous les logos représentés dans le magazine sont la propriété de leur ayant droit respectif.

### POUR DEVENIR AUTEUR

Contactez : [contrib@hackable.fr](mailto:contrib@hackable.fr)

Consultez :

## SOMMAIRE

### ACTUALITÉ

- 04 Conférence European GNU Radio Days 2024 : annonce de GNU Radio 4.0 et tutoriel sur les blocs de traitement Python

### SBC & RASPBERRY PI

- 18 Effort maximum : OpenBSD sur une carte RISC-V 1 GHz/1 Mio à 30 €

- 38 RPi & I2P : anonymiser son trafic avec l'Internet invisible

### OUTILS & LOGICIELS

- 50 Cross-compilation d'OpenBSD : c'est mal (tm), mais c'est pas grave...

- 58 Sipeed SLogic Combo 8 : un multioutil très utile... un jour

### FPGA & GATEWARE

- 68 FPGA facile : petite présentation et prise en main de LiteX

### MICROCONTROLEURS & ARDUINO

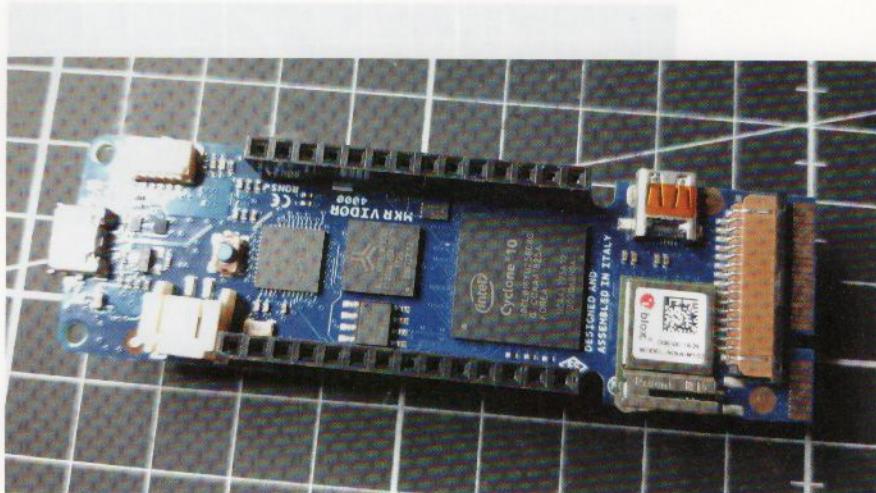

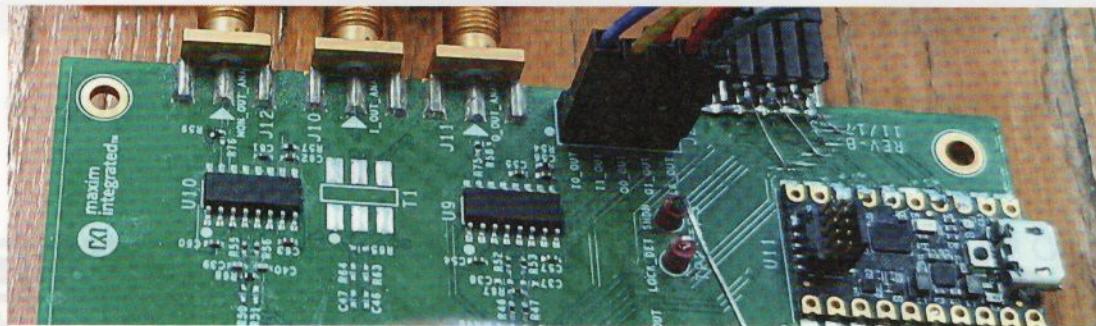

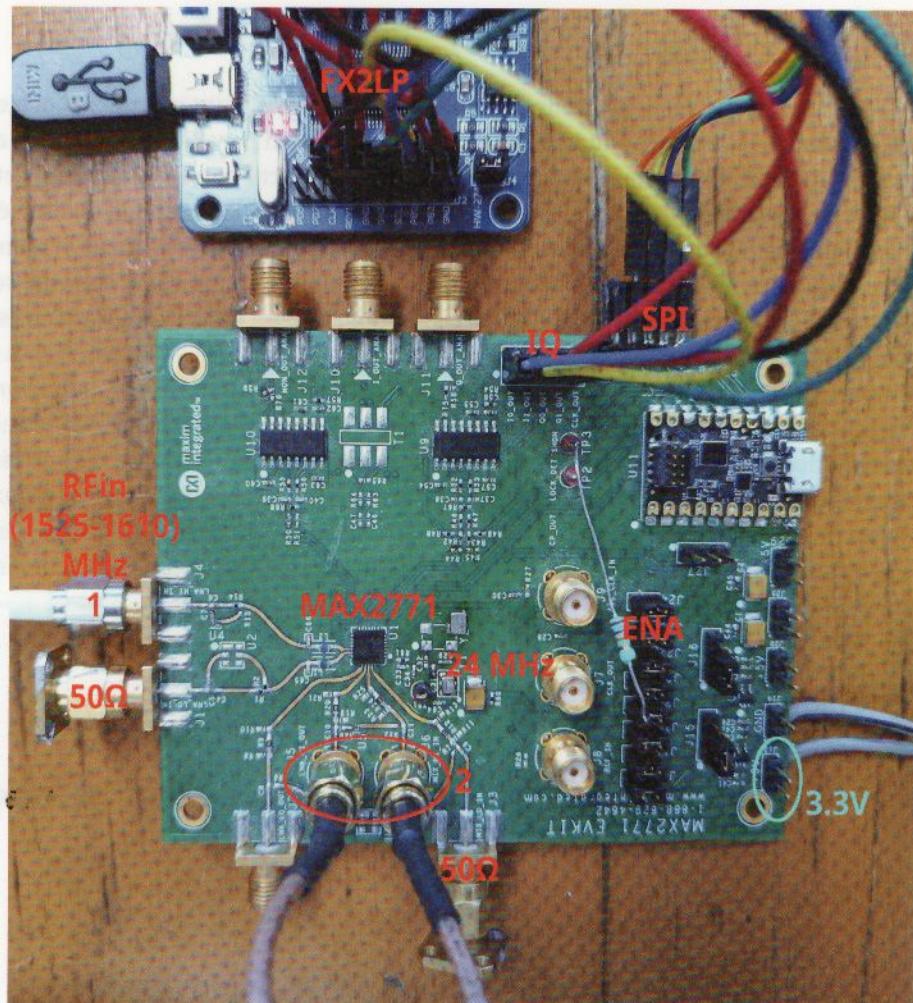

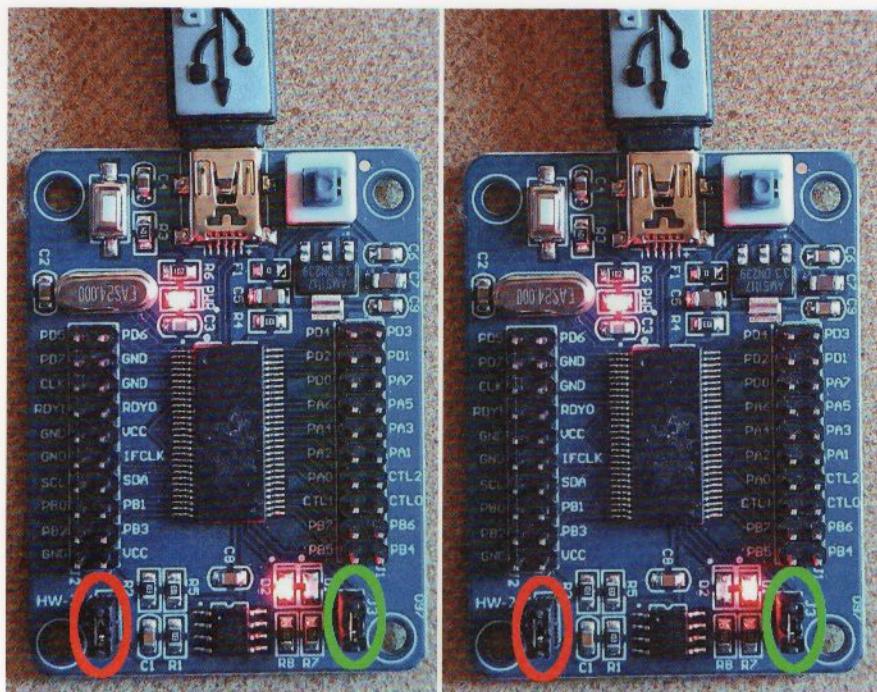

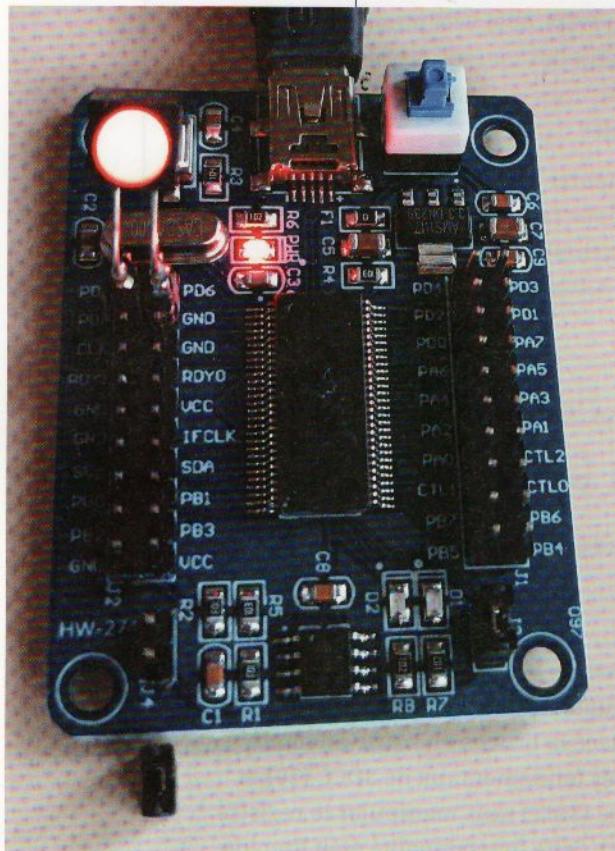

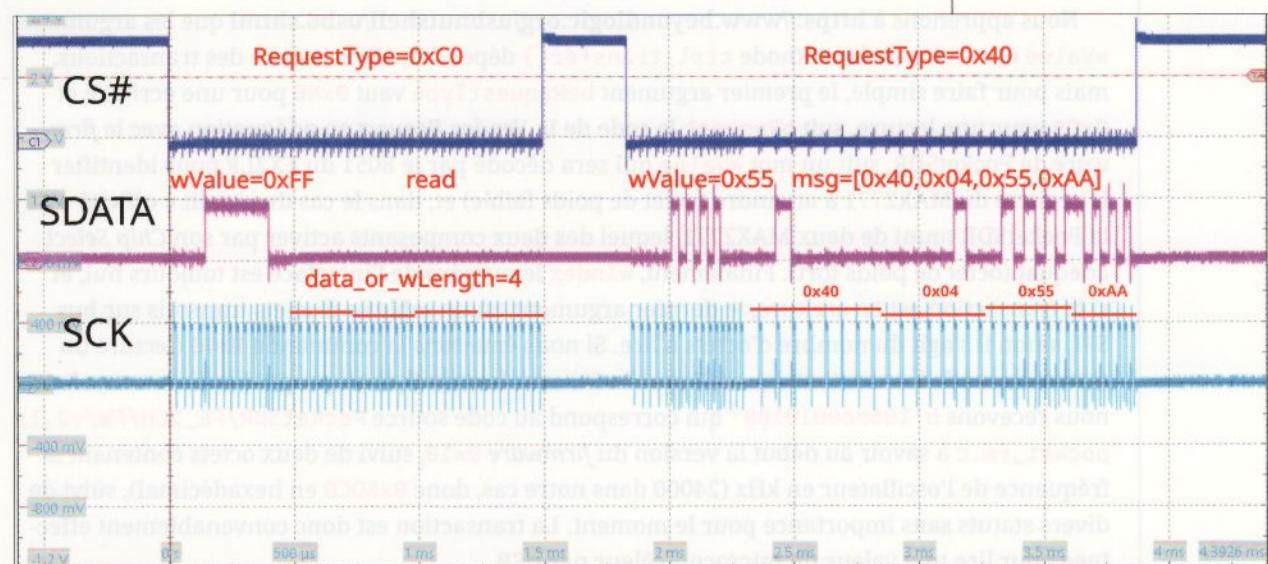

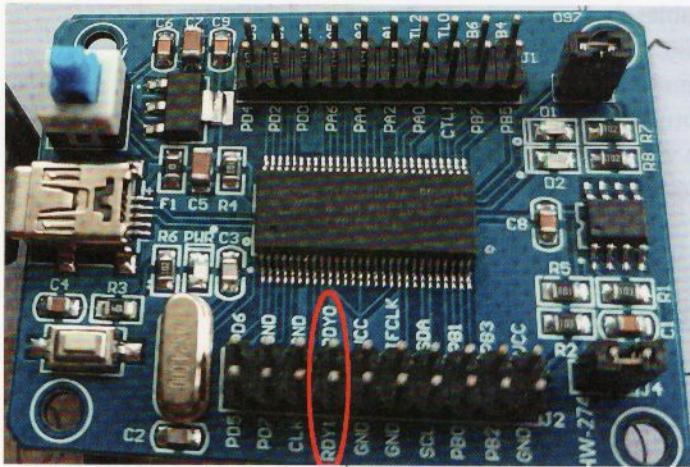

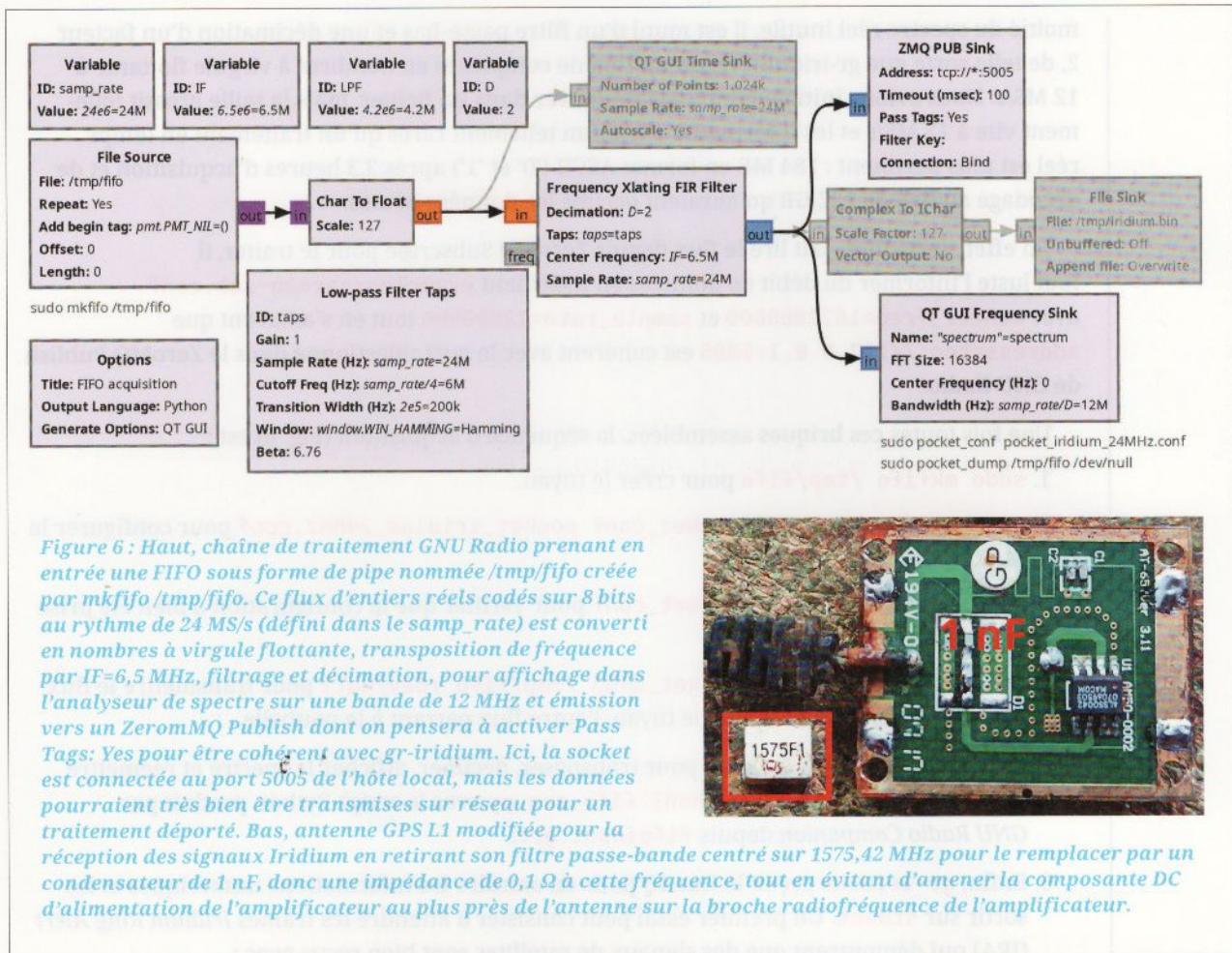

- 88 Programmation USB sous GNU/Linux : application du FX2LP pour un récepteur de radio logicielle dédié aux signaux de navigation par satellite (1/2)

### ABONNEMENT

- 79 Abonnement

**RETROUVEZ CE NUMÉRO ET BIEN PLUS ENCORE SUR CONNECT**

- » articles gratuits

- » contenu premium

- » listes de lecture...

**CONNECT.ED-DIAMOND.COM**

### À PROPOS DE HACKABLE...

#### HACKS, HACKERS & HACKABLE

Ce magazine ne traite pas de piratage. Un **hack** est une solution rapide et bricolée pour régler un problème, tantôt élégante, tantôt brouillonne, mais systématiquement créative. Les personnes utilisant ce type de techniques sont appelées **hackers**, quel que soit le domaine technologique. C'est un abus de langage médiatisé que de confondre « pirate informatique » et « hacker ». Le nom de ce magazine a été choisi pour refléter cette notion de **bidouillage créatif** sur la base d'un terme utilisé dans sa définition légitime, véritable et historique.

# CONFÉRENCE EUROPEAN GNU RADIO DAYS 2024 :

## ANNONCE DE GNU RADIO 4.0 ET TUTORIEL SUR LES BLOCS DE TRAITEMENT PYTHON

Jean-Michel Friedt

**Quelques retours sur la conférence européenne dédiée au logiciel libre de traitement de signaux radiofréquences échantillonnés en temps discret GNU Radio, et le développement de blocs Python dédiés au traitement du signal en flux tendu.**

# GNU Radio 4.0

– Conférence European GNU Radio Days 2024 : annonce de GNU Radio 4.0 et tutoriel... –

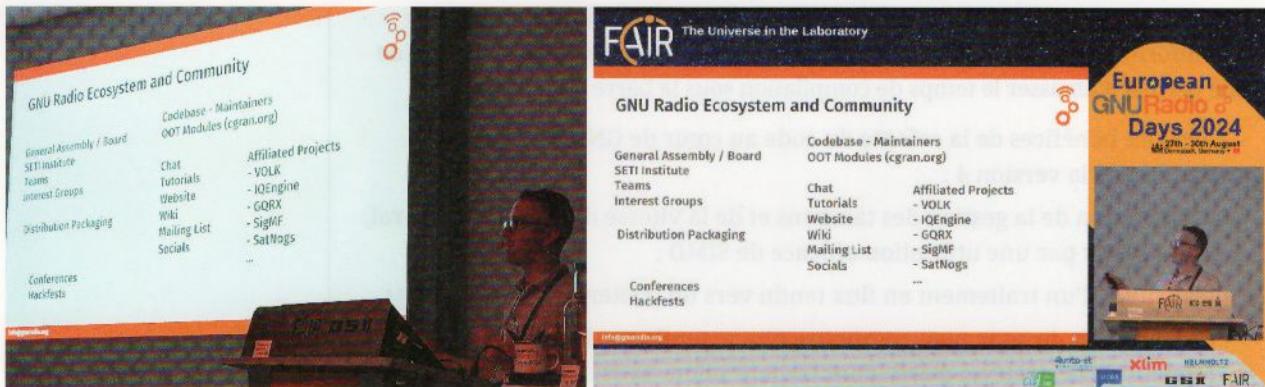

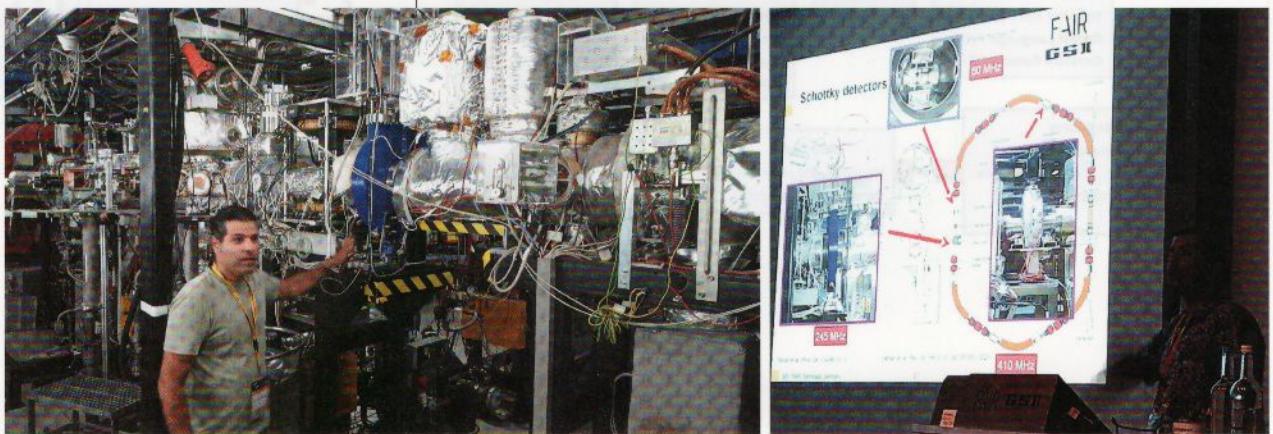

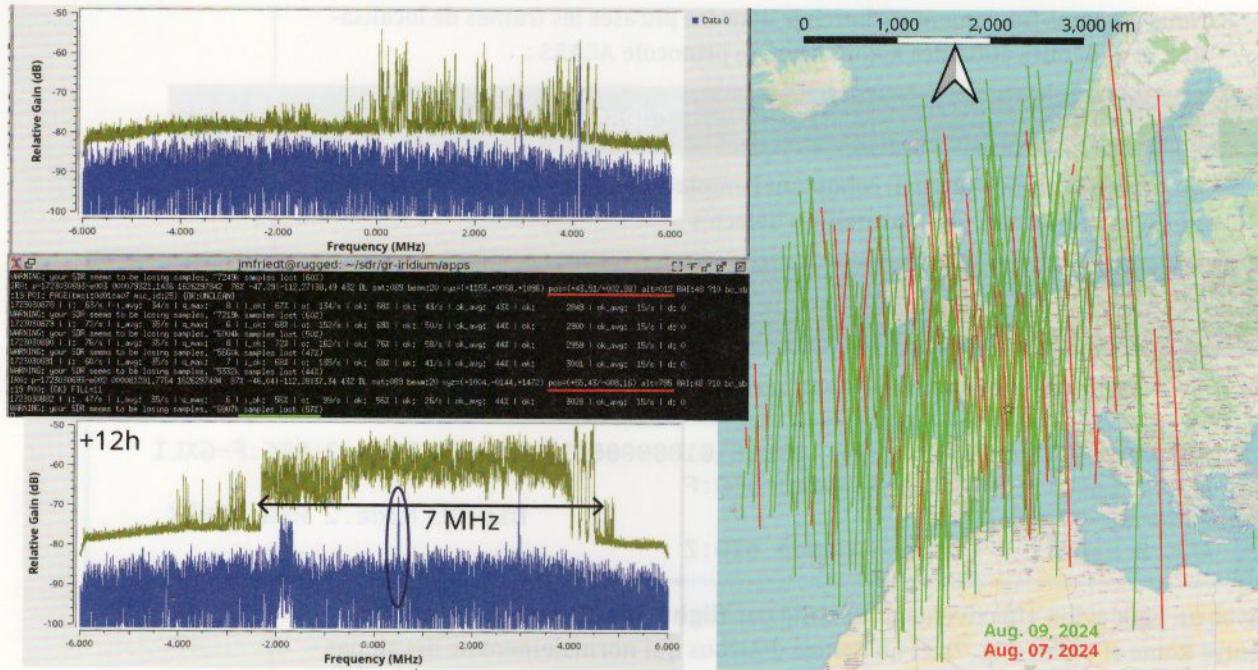

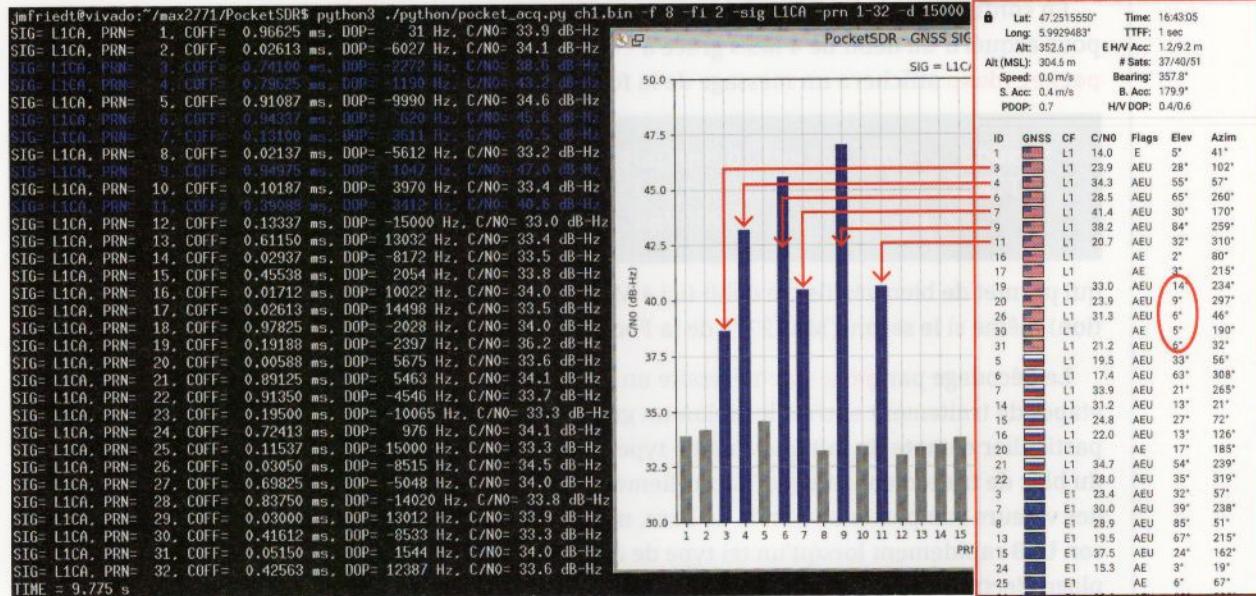

**L**a conférence European GNU Radio Days (Fig. 1), qui vise à regrouper les utilisateurs et développeurs de l'infrastructure libre de traitement numérique de signaux radiofréquences GNU Radio, a vu sa septième édition organisée en Allemagne dans les locaux de l'accélérateur d'ions GSI (*GSI Helmholtzzentrum für Schwerionenforschung*) près de Darmstadt. Ce grand instrument est en effet utilisateur de GNU Radio dans sa gestion des signaux radiofréquences nécessaires à accélérer les ions, et plusieurs centaines de points de mesure à base de systèmes commerciaux accessibles au grand public sont disséminés sur les accélérateurs linéaire et circulaire pour surveiller les instruments qui ne sont pas munis par défaut de systèmes de supervision. Alors que GNU Radio est l'héritage d'un long développement initié en 2001, un développement totalement innovant est engagé comme une potentielle refonte de GNU Radio. Josh Morman en particulier, maintenant président du projet GNU Radio, a participé à la réflexion sur l'architecture des interfaces et du code. La conférence, qui s'est tenue pendant la dernière semaine d'août au GSI/FAIR, fut l'opportunité d'annoncer

officiellement le développement de GNU Radio 4.0 et introduire les développeurs aux nouveaux concepts [1] proposés dans cette refonte de notre infrastructure favorite de traitement de signaux radiofréquences échantillonnes en temps discret.

Figure 1 :

Logo de l'édition

2024 de European

GNU Radio Days

qui s'est tenue

cette année en

Allemagne.

## 1. ASPECTS HISTORIQUES

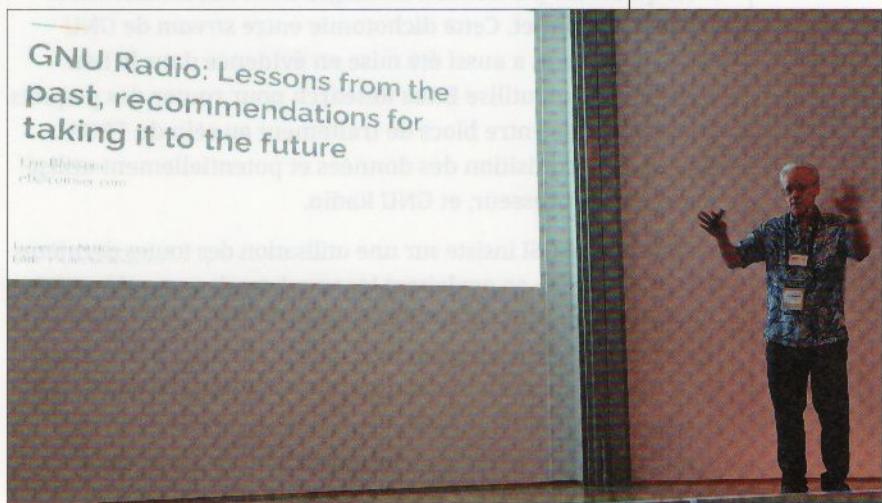

Après plusieurs mises en contexte de la recherche sur les ions et l'état exotique de la matière dans des situations aussi variées que les premières étapes de l'expansion de l'univers aux étoiles les plus denses, sujets d'étude de GSI [2, 3], la parole fut donnée à Eric Blossom (Fig. 2), créateur de la première version de GNU Radio [4]. Son travail, hérité d'un premier travail mené au MIT nommé *pspectra* dont les sources ont maintenant disparu, fut poursuivi sous les auspices bienveillants de John Gilmore, fondateur de l'EFF. Eric insiste sur l'aspect collaboratif du travail qui passe par des relations personnelles autant que sur des aspects techniques, et décrit l'évolution de ses collaborations au cours de développement de GNU Radio et en particulier la nécessité de trouver

Figure 2 :

Eric Blossom,

fondateur de GNU

Radio, présente

l'histoire du projet

depuis 2001 et ses

recommandations

pour les évolutions

futures, en insistant

sur l'aspect

collaboratif et

les relations

personnelles entre

développeurs et

utilisateurs.

un financement pérenne – potentiellement étatique, mais aussi de mécénat – pour développer un projet aussi important qu'une infrastructure de radio logicielle qu'un bénévole, aussi motivé fût-il, ne pourrait probablement pas mener à terme. Eric est désormais employé par Planet Labs [5], société qui lance des essaims de satellites en orbite basse pour la prise de vues depuis l'espace : la radio logicielle n'a pas encore sa place sur les véhicules spatiaux, mais deux présentations portent sur le prototypage rapide de stations au sol pour la réception de signaux venus de l'espace [6, 7].

Du point de vue de GSI/FAIR, l'intérêt pour la radio logicielle vient de l'ambition de surveiller l'accélérateur en temps réel, notamment par la signature électromagnétique des ions en mouvement, et réagir à des événements. Une dichotomie est mise en évidence entre le principe sous-jacent de la radio logicielle et de GNU Radio en particulier qu'est le flux continu de données acquises par le convertisseur analogique numérique – mode *streaming* – et l'encapsulation d'informations dans des paquets disjoints. La gestion des paquets – PDU pour *Protocol Data Unit* – a été ajoutée de façon quelque peu ad hoc dans GNU Radio et la refonte de GNU Radio 4 vise à corriger une telle déficience. Dans le cas de GSI, un PDU est la détection d'un événement qu'il faut propager le long de la chaîne de traitement. Dans le cas d'une communication numérique, il s'agit de la détection du préambule d'un paquet, par exemple par son mot de synchronisation, qui déclenche le décodage de l'en-tête qui contient les informations pour ensuite décoder le contenu du message. GNU Radio 4 étend le PDU à tout type de structure, dont la valeur scalaire (entier, réel ou complexe) n'est qu'un cas particulier, et intègre donc naturellement le concept de paquet. Cette dichotomie entre *stream* de GNU Radio et paquets a aussi été mise en évidence dans le lien entre RFNoC qu'utilise Ettus Research pour router des paquets d'informations entre blocs de traitement au sein du FPGA chargé de l'acquisition des données et potentiellement utilisé comme co-processeur, et GNU Radio.

L'équipe de GSI insiste sur une utilisation des toutes dernières moutures du C++ en exploitant les *templates* dans un objectif de vitesse en optimisant le code au travers des blocs individuels de traitement et en visant à tirer le meilleur parti des instructions SIMD par le processeur, et non par une bibliothèque dédiée telle que le propose VOLK actuellement. Cette approche, bien que démontrant d'excellentes performances en termes de temps d'exécution [1], présente pour le moment un inconvénient réd-

hibitoire : toute la chaîne de traitement doit être recompliée à chaque modification, et compte tenu du nombre d'optimisations possibles en observant ce qui se passe dans l'ensemble de la chaîne et pas juste dans chaque bloc individuel, ainsi que la multiplication des types de variables supportés par types polymorphes (PMT), la compilation s'avère très longue, de plusieurs minutes à plusieurs dizaines de minutes. Cet aspect pourrait passer anodin, si ce n'est que GNU Radio est promu comme un environnement de prototypage rapide et interactif : modifier un paramètre de bloc et relancer le traitement dans GNU Radio Companion est instantané lors de la génération du code Python qui instancie les bibliothèques contenant les méthodes de chaque bloc de traitement. Ce problème devra être réglé pour que GNU Radio 4 soit exploitable : des pistes pourraient venir de LLVM avec Clang qui met moins de la moitié du temps de compilation que GCC pour un exécutable au moins aussi rapide, mais trop long pour considérer le développement de la chaîne de traitement comme interactif. Le lien entre C++ et Python, tel qu'il existe aujourd'hui dans GNU Radio 3.x, fournira une capacité d'intégrer les blocs de traitement sous forme de greffons

## GNU Radio 4.0

– Conférence European GNU Radio Days 2024 : annonce de GNU Radio 4.0 et tutoriel... –

précompilés et retrouver l'interactivité actuelle. Les auteurs de GNU Radio 4.0 nous informent que désactiver les diverses optimisations et analyses statiques de code permet d'abaisser le temps de compilation sous la barre des 2 minutes.

Parmi les bénéfices de la refonte du code au cœur de GNU Radio avec la proposition de la version 4 :

- accélération de la gestion des tampons et de la vitesse de calcul en général, notamment par une utilisation efficace de SIMD ;

- transition d'un traitement en flux tendu vers un traitement par paquets ;

- organisation du code pour permettre une reconfiguration par le développeur de la stratégie d'ordonnancement selon divers critères (débit, latences, prise en compte des ressources matérielles). Les auteurs de GNU Radio 4.0 prévoient d'ouvrir un concours pour sélectionner le meilleur ordonnanceur ;

- intégration aisée dans tout matériel, indépendant d'une dépendance à un fournisseur spécifique, et en particulier en visant les applications embarquées, même en l'absence de système d'exploitation ;

- exploitation des dernières évolutions du C++ pour produire un code plus « propre » visant une meilleure accessibilité aux utilisateurs et développeurs de modules hors cœur (*Out Of Tree modules*) ;

et ce, avec une diffusion des codes en suivant la philosophie promue par la FSFE (Free Software Foundation Europe) de *Public Money, Public Code* [8] par des auteurs financés par un institut de recherche public (Fig. 3).

Les développeurs de GNU Radio 4.0 envisagent de passer en licence LGPL dans l'espoir d'attirer des utilisateurs et donc potentiellement des contributeurs de sociétés privées. Cette ouverture des logiciels libres vers les acteurs privés ne me semble pas souhaitable. En effet, il me semble que cette idée que des sociétés privées – et en particulier du complexe militaro-industriel français – vont contribuer à du logiciel libre me paraît non seulement naïve et contraire aux observations, mais dangereuses pour le logiciel libre puisque la société privée s'approprie les quelques projets qui ont péniblement émergé, pour suffisamment en modifier l'API ou le protocole pour garantir un monopole et une incompatibilité avec la solution originale qui va être noyée dans le marketing faute de ressources d'une communauté de libristes obsédés par la technique, tel que nous le constatons par exemple pour White Rabbit. Une GPLv3 garantit au moins la protection de la FSF ([https://en.wikipedia.org/wiki/Free\\_Software\\_Foundation,\\_Inc.\\_v.\\_Cisco\\_Systems,\\_Inc.](https://en.wikipedia.org/wiki/Free_Software_Foundation,_Inc._v._Cisco_Systems,_Inc.)), quitte à repousser les contributeurs privés, qui sont de toute façon peu enclins à participer activement à des développements libres. On notera que GSI/FAIR – comme nombre d'accélérateurs de particules et détecteurs distribués de rayons cosmiques – est contributeur et développeur de plateformes White Rabbit dédiées à leur contrôle

Figure 3 : L'initiative « *Public Money, Public Code* » de la Free Software Foundation Europe (FSFE) qui encourage les projets financés par de l'argent public à libérer leur code, proposition suivie par bien peu de projets français, mais qui fut au moins discutée en Allemagne... sans beaucoup plus de résultats d'après <https://fsfe.org/news/2022/news-20220315-01.en.html>, mais avec quelques succès tout de même, si l'on en croit la présentation « *Some updates on public code in Germany* » au FOSDEM 2024.

**Figure 4 :**

Josh Morman,

président de

GNU Radio, résume

les principales

évolutions du projet

au cours de l'année

et la vision pour les

futures évolutions.

de l'accélérateur sous forme de cartes PCIe. Les développeurs autour de Dietrich Beck ont eu la gentillesse de me prêter gracieusement certaines de ces cartes pour que je puisse illustrer le bénéfice mutuel de GNU Radio et White Rabbit pour former un système distribué cohérent et synchrone de génération et d'acquisition de signaux radiofréquences, démontré avec la mesure de direction d'arrivée de signaux issus du RADAR GRAVES et réfléchis par des avions, depuis un site situé à une quarantaine de kilomètres de l'émetteur [9].

Josh Morman, président actuel de GNU Radio, fait un récapitulatif de l'état d'avancement du logiciel [10], avec la promesse de maintenir 3.10 aussi longtemps que nécessaire tant que 4 ne sera pas utilisable (Fig. 4) et que les blocs de traitement actuels n'auront pas été implémentés pour la nouvelle version, puisque rien n'est compatible, de l'API existante aux chaînes décrites pour le moment en YAML dans GNU Radio Companion. GSI dédie actuellement du personnel à ce projet, mais en vue de répondre aux besoins de l'accélérateur : la communauté de développeurs devra mettre la main à la pâte pour obtenir les liens vers Python ou une interface graphique comparable à GNU Radio Companion. En vue d'évaluer l'utilisation de GNU Radio 4.0, l'auteur expérimenté qu'est Daniel Estévez est financé pour démontrer le gain en débit d'un radio-modem numérique sous GNU Radio 4.0 et fait part de son expérience [11].

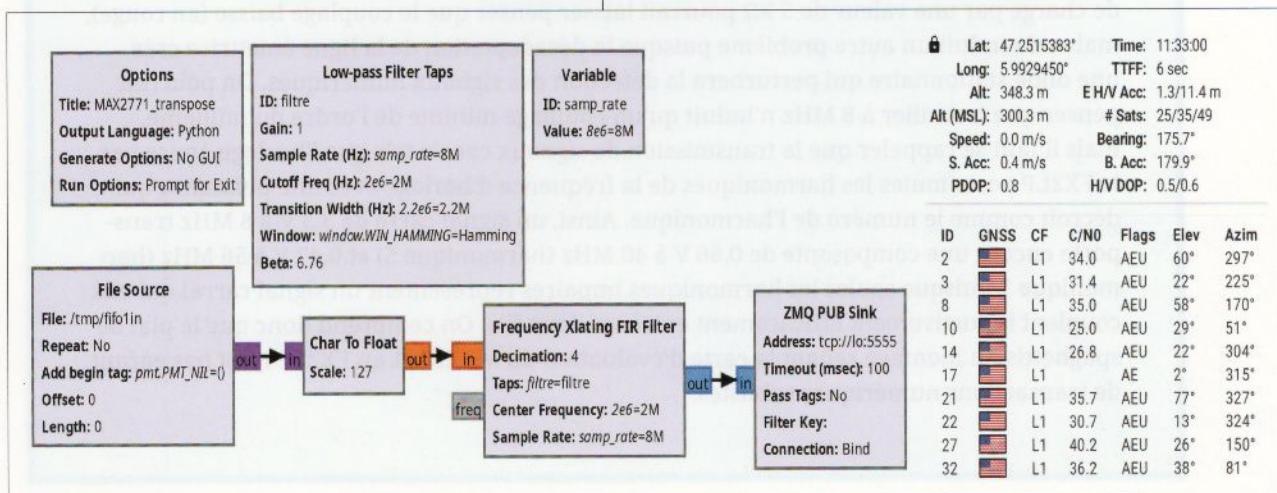

## 2. TUTORIELS

Pour entrer dans des considérations plus techniques, l'auteur de cette prose a été sollicité pour introduire GNU Radio 3.10 aux non-développeurs de la conférence, et en particulier les chercheurs et ingénieurs de GSI qui auraient entendu parler du logiciel sans s'en être approprié les concepts et le maniement. Il est intéressant de noter que le changement de paradigme qui semblait avoir repoussé certains de ces utilisateurs est le passage au traitement d'un flux continu de données par des blocs agencés séquentiellement, plutôt que par un programme statique bouclant sur des paquets d'éléments acquis par une interface de conversion analogique numérique. Ainsi, l'objectif était d'attirer des utilisateurs qui connaissent déjà la programmation Python, qui post-traitent déjà des fichiers de données,

# GNU Radio 4.0

– Conférence European GNU Radio Days 2024 : annonce de GNU Radio 4.0 et tutoriel... –

mais cette fois les amener à du traitement temps réel bénéficiant de la mise en forme et du prétraitement par une chaîne GNU Radio.

Après une rapide introduction des concepts de base – couleurs associées aux types de données transmises entre blocs de traitement, échantillonnage en temps discret, tension imaginaire et fréquence négative, repliement spectral – nous avons abordé trois types d’interaction de GNU Radio avec Python :

1. L’insertion de quelques lignes de code Python dans la chaîne de traitement produite par GNU Radio Companion.

2. L’insertion d’un code conséquent Python dans le code source produit par GNU Radio Companion.

3. Le traitement du flux IQ par un bloc de traitement écrit en Python.

Ces trois points définissent la séquence des sections qui suivent pour en développer les principes.

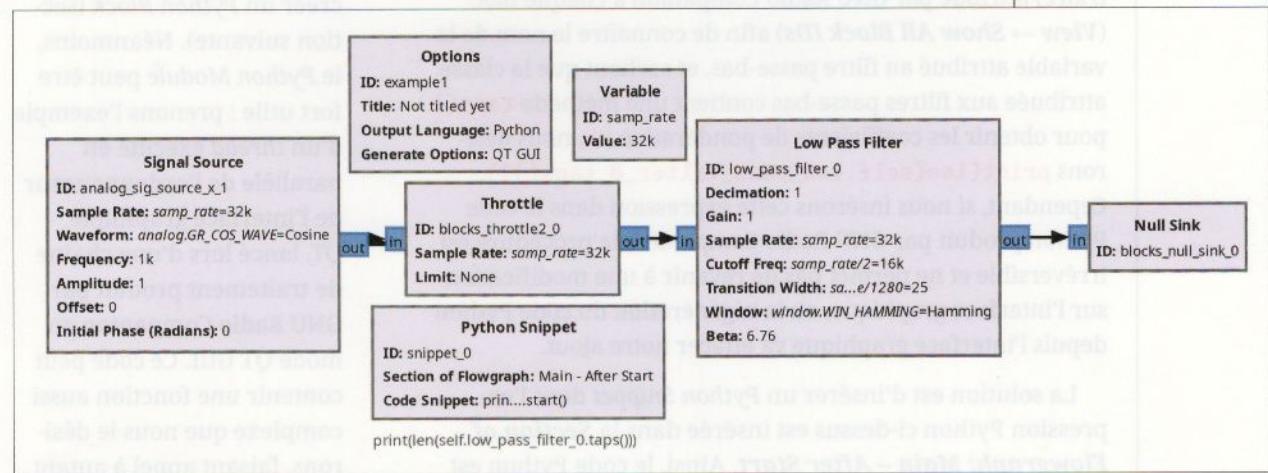

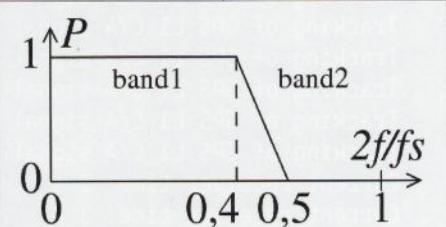

## 2.1 Python Snippet

Le premier cas est le plus simple : nous voulons afficher la longueur d’un vecteur lors de l’exécution d’une chaîne de traitement. Considérons le cas trivial d’un filtre passe-bas (Fig. 5) : ce filtre est caractérisé par une fréquence de coupure et une bande de transition. La fréquence de coupure se comprend bien – la fréquence à laquelle l’amplitude du signal transmis par le filtre commence à décroître – mais qu’est-ce que la bande de transition ? Il s’agit d’un paramètre, que nous noterons  $\delta f$ , qui détermine à quel écart de la fréquence de coupure l’amplitude du signal transmis par le filtre doit avoir baissé. Un utilisateur naïf pourrait se dire que le signal doit passer « instantanément » d’une fonction de transfert passante (amplitude unitaire) à coupante (amplitude nulle). Un tel filtre ne peut exister, ou nécessite un nombre infini de coefficients. De toute façon, GNU Radio Companion nous insulte si nous choisissons une bande de transition nulle en disant **IndexError: firdes check failed: transition\_width > 0**. Comment donc choisir  $\delta f$  ?

L’argumentaire est le suivant : si nous définissons une bande de transition  $\delta f$ , il faut que la transformée de Fourier puisse déterminer

Figure 5 :

Exploitation du

Python Snippet pour

exécuter quelques

lignes de code dans

un emplacement

configurable

du code généré

par GNU Radio

Companion. Ici,

nous avons activé

la visualisation

de l’identifiant de

chaque bloc pour

connaître le nom du

filtre passe-bas et en

afficher le nombre

de coefficients.

l'amplitude à une fréquence  $f$  et une fréquence adjacente  $f + \delta f$ , donc avoir une résolution spectrale d'au moins  $\delta f$ . Une transformée de Fourier d'un signal temporel sur  $N$  points donne un signal dans le domaine spectral sur  $N$  points aussi, dans une gamme de fréquences s'étendant de  $-f_s/2$  à  $+f_s/2 - f_s/N$  avec  $f_s$  la fréquence d'échantillonnage en temps discret du signal. Nous approximerons pour cette discussion la borne supérieure à  $+f_s/2$  en supposant  $N$  grand. Ainsi, la résolution spectrale du spectre est  $f_s/N$ , et cette résolution doit être au moins  $\delta f$ , ou en d'autres termes  $N > f_s/\delta f$ . Nous voyons que si  $f_s$  est petit,  $N$  va devenir démesurément grand. Or, l'expression temporelle d'un filtre, défini par son gabarit dans le domaine spectral, est un filtre à réponse impulsionnelle finie (FIR) reliant sortie  $y$  avec valeurs passées des entrées  $x$  par

$$y_n = \sum_{k=0}^{N-1} b_k \cdot x_{n-k}$$

et il s'agit bien du même  $N$  que précédemment par bijection de la transformée de Fourier. Ainsi donc, lorsque nous exprimons un filtre, chaque échantillon de sortie nécessite  $N$  multiplications, et on voit bien que choisir  $N$  trop grand, ou  $\delta f$  trop petit, va nécessiter trop de ressources de calcul, même sur un processeur moderne.

Ainsi donc, nous affirmons que GNU Radio choisit  $N$  le nombre de coefficients de l'ordre de  $f_s/\delta f$ , et nous voulons le vérifier expérimentalement.

Pour ce faire (Fig. 5), nous affichons l'identifiant (arbitraire) attribué par GNU Radio Companion à chaque bloc (*View → Show All Block IDs*) afin de connaître le nom de la variable attribuée au filtre passe-bas, et sachant que la classe attribuée aux filtres passe-bas contient une méthode `taps()` pour obtenir les coefficients de pondération `bk`, nous désirons `print(len(self.low_pass_filter_0.taps()))`. Cependant, si nous insérons cette expression dans le code Python produit par GNU Radio Companion, la procédure est irréversible et ne permet pas de revenir à une modification sur l'interface graphique, ou la régénération du code Python depuis l'interface graphique va effacer notre ajout.

La solution est d'insérer un *Python Snippet* dont l'expression Python ci-dessus est insérée dans la *Section of Flowgraph: Main - After Start*. Ainsi, le code Python est

appelé après initialisation des variables, et en choisissant une bande de transition égale à `samp_rate/128` dans le filtre passe-bas, nous sommes informés que le nombre de coefficients est 309. Si nous divisons par 10 la bande de transition pour choisir `samp_rate/1280`, nous constatons que le nombre de coefficients croît bien à 3083 donc d'un facteur 10, la théorie est vérifiée.

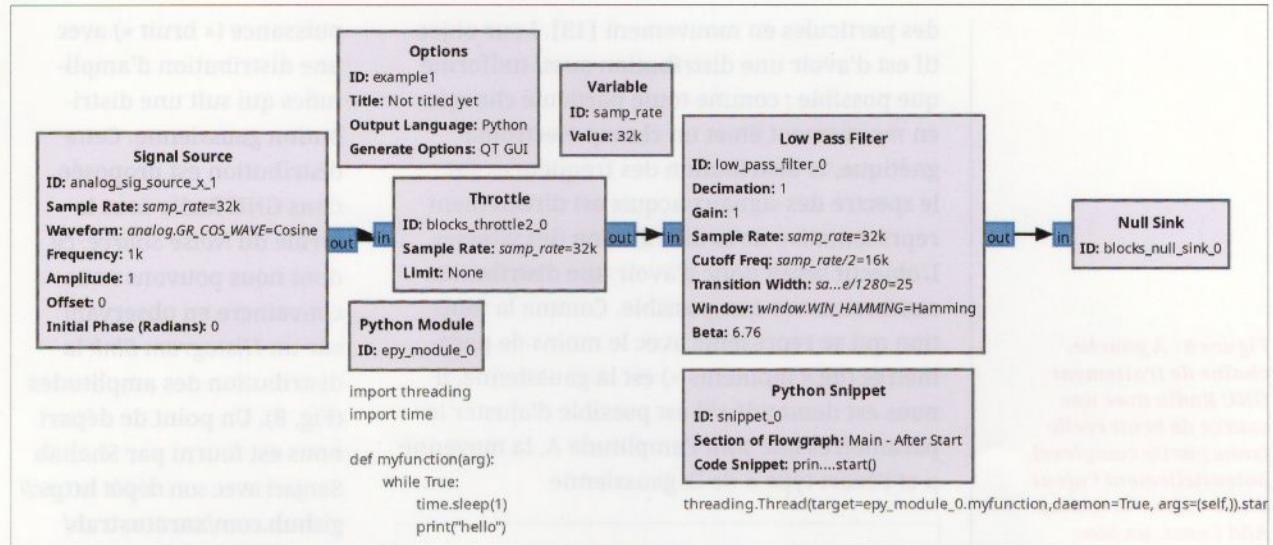

## 2.2 Python Module

Il est fondamental de comprendre que les *Python Snippets* et *Python Modules* ne peuvent pas accéder aux données IQ à traiter, mais ne peuvent qu'agir sur le comportement des blocs de traitement et les variables qui en définissent le comportement. Afin de pouvoir interagir avec les données radiofréquences, il faut créer un *Python Block* (section suivante). Néanmoins, le *Python Module* peut être fort utile : prenons l'exemple d'un *thread* exécuté en parallèle de l'ordonnanceur de l'interface graphique QT, lancé lors d'une chaîne de traitement produit par GNU Radio Companion en mode QT GUI. Ce code peut contenir une fonction aussi complexe que nous le désirons, faisant appel à autant

# GNU Radio 4.0

– Conférence European GNU Radio Days 2024 : annonce de GNU Radio 4.0 et tutoriel... –

de classes que nécessaire, et être lancé depuis le *Python Snippet* que nous venons de voir sous forme de *thread* indépendant de l'exécution du père (Fig. 6).

## 2.3 Python Block

Les utilisateurs au GSI/FAIR (Fig. 7) de GNU Radio analysent la distribution des vitesses des ions dans la boucle de stockage en observant les signaux issus d'antennes placées à proximité

Figure 6 : Un thread séparé de l'ordonnanceur Qt qui se charge de gérer les événements de l'interface graphique, qui se contente ici de simplement afficher un message chaque seconde. Ce thread sera exécuté par un Python Snippet sans lequel le programme contenu dans le Python Module est du code mort. Noter l'option `daemon=True` au lancement qui garantit la mort du fils lorsque le père achève son exécution.

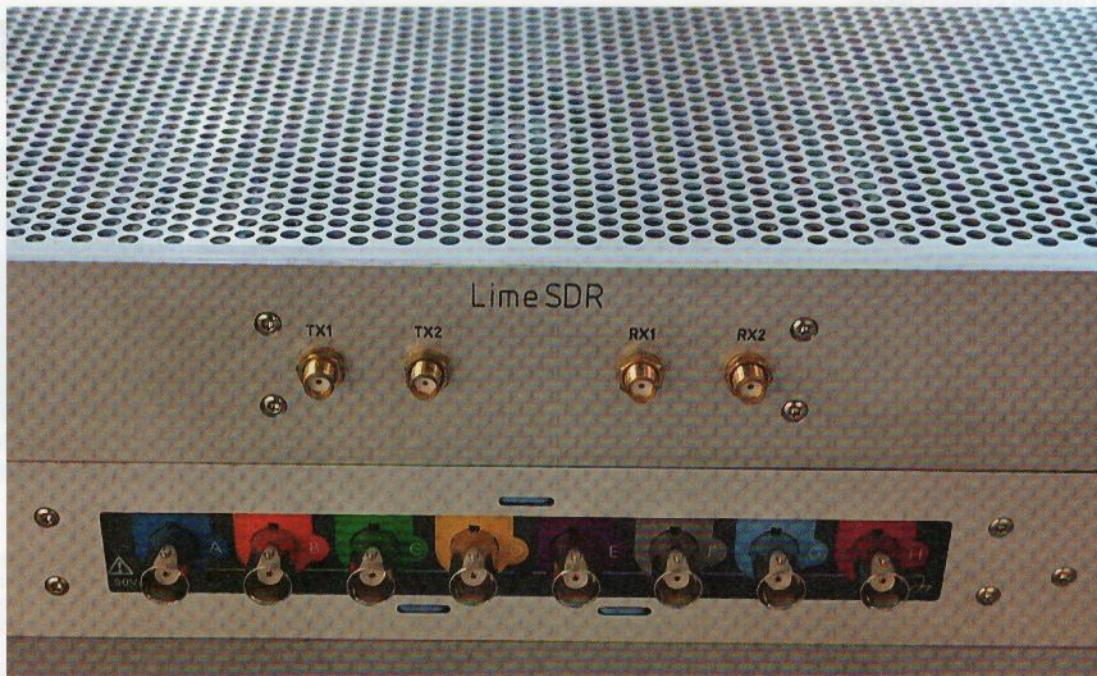

Figure 7 : Shahab Sanjari présente l'anneau de stockage des ions (gauche) dans lequel il observe la durée de vie des divers isotopes et leur fission en divers éléments, et à droite une description du dispositif expérimental dans lequel il exploite GNU Radio pour traiter les signaux acquis par LimeSDR. Notez les fréquences de 60, 245, et 410 MHz [12] parfaitement commensurables avec les plateformes de radio logicielle couramment disponibles. Il est à l'origine de la demande pour un tutoriel sur l'ajustement des paramètres d'une gaussienne sur une courbe expérimentale.

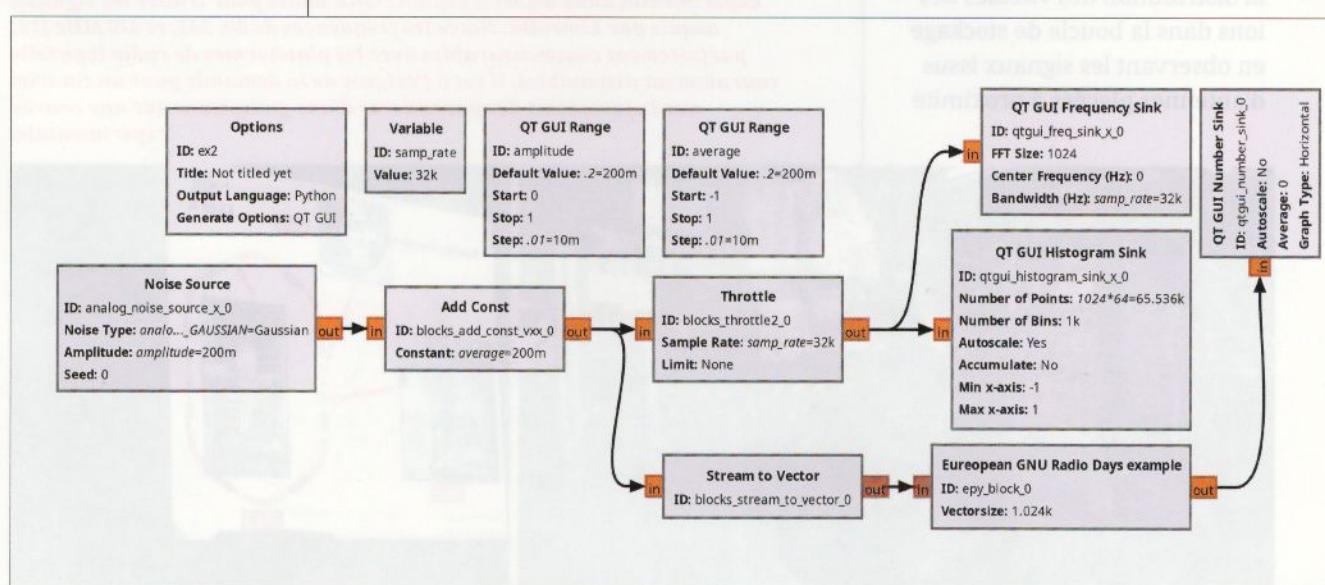

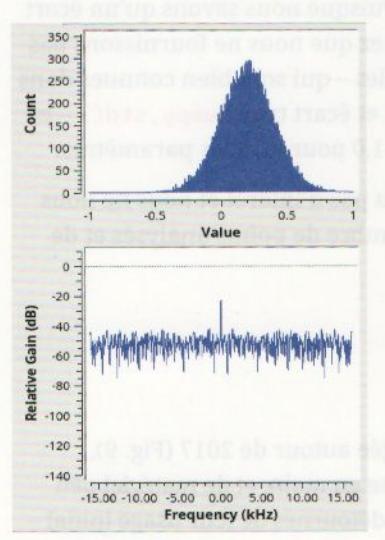

**Figure 8 :** À gauche, chaîne de traitement GNU Radio avec une source de bruit réelle (sans partie complexe), potentiellement l'ajout d'une valeur moyenne Add Const, un bloc de cadencement en l'absence d'horloge physique Throttle, en haut l'affichage du spectre, au milieu l'histogramme des amplitudes, et en bas le bloc de traitement spécifiquement conçu pour extraire les paramètres de la gaussienne. Droite : distribution en amplitude (haut) et spectrale (bas) de la source de bruit.

des particules en mouvement [13]. Leur objectif est d'avoir une distribution aussi uniforme que possible : comme toute particule chargée en mouvement émet un champ électromagnétique, la distribution des fréquences sur le spectre des signaux acquis est directement représentative de la distribution des vitesses. L'objectif serait donc d'avoir une distribution aussi resserrée que possible. Comme la fonction qui se représente avec le moins de paramètres (de « moments ») est la gaussienne, il nous est demandé s'il est possible d'ajuster les paramètres que sont l'amplitude A, la moyenne  $\mu$  et l'écart type  $\sigma$  de la gaussienne

$$y = A \cdot \exp\left(\frac{-(x - \mu)^2}{2\sigma^2}\right)$$

connaissant les observations aux abscisses x. Afin de démontrer ce principe, nous produisons une distribution gaussienne pour effectuer nos développements, non pas sur un spectre en fréquences, mais sur les amplitudes d'un bruit caractérisé par AWGN (*Additive White Gaussian Noise*) dans lequel toutes les fréquences sont représentées avec la même

puissance (« bruit ») avec une distribution d'amplitudes qui suit une distribution gaussienne. Cette distribution est proposée dans GNU Radio sous la forme du *Noise Source*, ce dont nous pouvons nous convaincre en observant sur un *Histogram Sink* la distribution des amplitudes (Fig. 8). Un point de départ nous est fourni par Shahab Sanjari avec son dépôt [https://github.com/xaratusrah/curve-fitting/blob/main/curve\\_fit.py](https://github.com/xaratusrah/curve-fitting/blob/main/curve_fit.py) qu'il utilise actuellement en post-traitement et désire insérer dans la chaîne d'analyse en temps réel GNU Radio.

Le tutoriel [https://wiki.gnuradio.org/index.php?title=Creating\\_Your\\_First\\_Block](https://wiki.gnuradio.org/index.php?title=Creating_Your_First_Block) et le motif (*template*) de bloc

# GNU Radio 4.0

– Conférence European GNU Radio Days 2024 : annonce de GNU Radio 4.0 et tutoriel... –

de traitement sont limpides et permettent de rapidement commencer le développement, si ce n'est que pour pouvoir tracer un histogramme, il faut avoir accumulé un nombre minimum de points avant de pouvoir remplir les cases correspondant aux différentes valeurs possibles d'amplitudes. Afin de garantir un nombre minimum de points, nous convertissons le flux continu de données (*stream*) en un vecteur de longueur correspondant au nombre de points que nous désirons distribuer dans les cases de l'histogramme. Un second tutoriel [https://wiki.gnuradio.org/index.php?title=Python\\_Block\\_with\\_Vectors](https://wiki.gnuradio.org/index.php?title=Python_Block_with_Vectors) indique comment fournir au bloc des entrées qui ne sont pas scalaires, mais des vecteurs sous la forme de `in_sig=[(np.float32, vectorSize)]`. De cette façon, le flux de données acquis par la fonction `work` exécutée en boucle infinie est une structure à trois dimensions telle que le démontre :

```

print(f"{len(input_items[0])} {input_items[0][0].size} {input_items[0].size}")

```

qui indique 8 1024 8192 qui s'interprète comme :

- `input_items[0]`, car nous avons une entrée. Si le bloc avait plusieurs entrées, cet indice indiquerait de quelle entrée il s'agit ;

- `input_items[0][k]` indique le `k`-ième vecteur, puisque l'ordonnateur GNU Radio n'a aucune raison de nous fournir un seul vecteur, mais peut avoir accumulé suffisamment de points en amont pour fournir plusieurs vecteurs ;

- `input_items[0][k][m]` est le `m`-ième point du `k`-ième vecteur. Cependant, chaque vecteur contient bien les 1024 points requis par la conversion de `stream` en `vector` en amont de ce bloc dédié.

Une fois cette structure comprise, la suite est limpide. Nous calculons l'histogramme des points en entrée supposés dans l'intervalle  $[-1, +1]$  au moyen de Numpy par :

```

y,x=np.histogram(input_items[0][k],bins=32,range=(-1,1))

```

puis effectuons l'ajustement gaussien avec la fonction définie dans `fit_function()` des mesures issues de l'histogramme. Seule subtilité, comme les intervalles et les piquets, le vecteur `x` issu de `np.histogram()` contient les extrémités de chaque classe, donc  $n+1$  valeurs s'il y a  $n$  classes. Nous déduisons la valeur moyenne de chaque classe comme `x=0.5*(x[0:-1]+x[1:])` qui a bien  $n$  valeurs comme `y`. Finalement, nous affichons l'amplitude, la valeur moyenne et l'écart type, et renvoyons pour traitement ultérieur ce dernier paramètre qui alimente dans notre chaîne de traitement un QT GUI Number Sink.

```

import numpy as np

from gnuradio import gr

from scipy.optimize import curve_fit

class blk(gr.decim_block):

def __init__(self, vectorSize=1024): # default args

gr.sync_block.__init__(

self,

name='European GNU Radio Days example',

in_sig=[(np.float32, vectorSize)],

out_sig=[np.float32]

)

def fit_function(self, x, A, mu, sigma): # fitting function

return A*np.exp(-(x-mu)**2/(2.*sigma**2))

def work(self, input_items, output_items):

for k in range(0, len(output_items)):

y, x=np.histogram(input_items[0][k], bins=32, range=(-1,1))

x=0.5*(x[0:-1]+x[1:]) # x=middle of each bin

popt, pcov = curve_fit(self.fit_function, x, y)

print(f'{popt[0]:.2f}\t{popt[1]:.2f}\t{np.abs(popt[2]):.3f}')

# sigma ** 2 so either positive or negative solutions are acceptable

output_items[0][k]=np.abs(popt[2])

return len(output_items[0])

```

Le lecteur qui exécute ce code pourra se convaincre que la valeur moyenne introduite par le bloc **Add Const** est bien identifiée dans le second paramètre  $\mu$  de l'ajustement, tandis que l'« amplitude » telle que l'appelle ce paramètre du bloc source de bruit est bien identifiée par l'écart type. Seule petite subtilité : l'écart type  $\sigma$  n'apparaît que par son carré dans l'équation d'ajustement, et les deux solutions de  $\sigma$  positive ou négative sont parfois atteintes selon la nature du bruit et le cheminement de la descente de gradient. Puisque nous savons qu'un écart type est forcément positif, nous affichons la valeur absolue. Notez que nous ne fournissons pas ici le dernier paramètre optionnel que sont les conditions initiales – qui sont bien connues dans le cas d'une gaussienne comme valeur moyenne `numpy.mean()` et écart type `numpy.std()` – et par défaut le point de départ de la recherche de solution prend 1,0 pour tous les paramètres.

Le dernier paramètre qu'est l'amplitude de l'histogramme n'a pas d'intérêt et nous ne nous attarderons pas dessus – il est principalement dépendant du nombre de points analysés et de leur étalement dans les diverses classes de l'histogramme.

## CONCLUSION

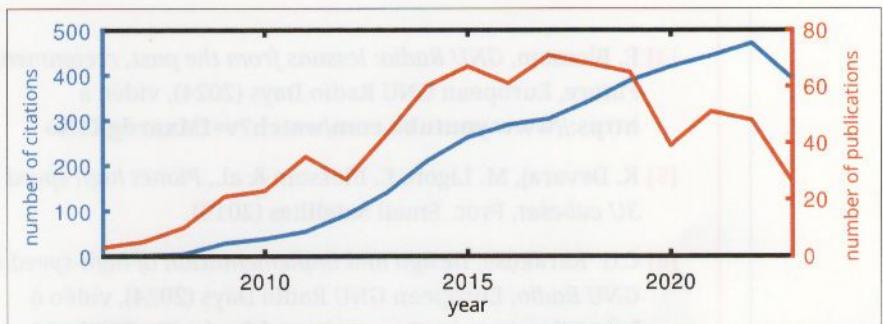

La radio logicielle, et GNU Radio en particulier, a vu son apogée autour de 2017 (Fig. 9), combinaison d'un environnement logiciel stable et simple de prise en main, et de matériel peu coûteux – récepteurs de télévision numérique terrestre RTL-SDR détournés de leur usage initial – permettant d'aborder nombre de protocoles de communication radiofréquences.

# GNU Radio 4.0

– Conférence European GNU Radio Days 2024 : annonce de GNU Radio 4.0 et tutoriel... –

Sept ans plus tard, les contributions scientifiques et techniques s'épuisent, probablement parce que l'outil est devenu tellement courant et adopté qu'il ne mérite plus à être mentionné (qui cite l'utilisation d'un oscilloscope dans une mesure électronique ?).

Pourtant, le développement de GNU Radio se poursuit, notamment pour tirer parti des dernières évolutions des plateformes de calcul hétérogènes, tentant d'aborder de façon transparente CPU généralistes, GPU et FPGA pour distribuer sur les ressources les plus appropriées les diverses étapes d'une chaîne de traitement. La cinquantaine de participants à la conférence a conclu les échanges sur les utilisations innovantes de la radio logicielle, même pour éventuellement détecter en temps réel un ion rare qu'il faut absolument capturer avant qu'il ne disparaisse. Les vidéos des présentations de la conférence sont disponibles sur le canal European GNU Radio Days sur YouTube à <https://youtube.com/@europeangnuradiodays1445> dans la série « European GNU Radio Days 2024 » avec leurs transparents comme liens dans le programme à <https://events.gnuradio.org/event/23/>.

Figure 9 : Nombre de publications (rouge) et de citations (bleu) contenant le terme « GNU Radio » en fonction des années.

Source : Web of Science.

## REMERCIEMENTS

Cyrille Morin a relu les codes Python pour tenter d'en éliminer les plus grossières maladresses, mais toute erreur résiduelle ne peut être imputée qu'à l'auteur de ces lignes. **JMF**

## RÉFÉRENCES

- [1] GNU Radio 4.0 Developer Tutorials à <https://www.youtube.com/playlist?list=PLCfH8xIFcsLlkmVHKLjCr1UaYiMwewiFS>

- [2] J. Messchendorp, *Pushing boundaries: femtoscale research with large-scale tech (in accelerator-driven nuclear physics)*, European GNU Radio Days (2024), vidéo à <https://www.youtube.com/watch?v=66kqn-2W6I8>

- [3] J. Stadlmann, ... and one to accelerate them all, European GNU Radio Days (2024), vidéo à <https://www.youtube.com/watch?v=CiaVABVZ71U>

- [4] E. Blossom, *GNU Radio: lessons from the past, recommendations for taking it to the Future*, European GNU Radio Days (2024), vidéo à <https://www.youtube.com/watch?v=fMxardgX1Ao>

- [5] K. Devaraj, M. Ligon, E. Blossom & al., *Planet high speed radio: Crossing Gbps from a 3U cubesat*, Proc. Small Satellites (2019).

- [6] C.G. Karaköse, *Design and implementation of high-speed data link receiver with GNU Radio*, European GNU Radio Days (2024), vidéo à <https://www.youtube.com/watch?v=jxqQcORWem4>

- [7] G. Ari Özcan, *Design and Implementation of an Adaptive Data Rate LoRa Modem for LEO Satellites Using SD*, European GNU Radio Days (2024), vidéo à <https://www.youtube.com/watch?v=Jc0aT4i2VaM>

- [8] <https://wiki.fsfe.org/Activities/PMPC> et <https://publiccode.eum/>

- [9] J.-M Friedt, *Distributed coherent SDR systems: GNU Radio rides the White Rabbit*, European GNU Radio Days (2024), vidéo à <https://www.youtube.com/watch?v=iyUabco0z4A>

- [10] J. Morman, *GNU Radio Project Overview and Update*, European GNU Radio Days (2024), vidéo à [https://www.youtube.com/watch?v=89l9\\_7PitTE](https://www.youtube.com/watch?v=89l9_7PitTE)

- [11] D. Estévez, *gr4-packet-modem: a QPSK packet modem for GNU Radio 4.0*, European GNU Radio Days (2024), vidéo à <https://www.youtube.com/watch?v=1EPuhalJxCK>

- [12] M.S. Sanjari & al., *A 410 MHz resonant cavity pickup for heavy ion storage rings*, Rev. Sci. Instrum. 91(8) 083303 (2020).

- [13] P. Kienle, F. Bosch, P. Bühler, T. Faestermann, Yu A. Litvinov, N. Winckler, M. S. Sanjari & al., *High-resolution measurement of the time-modulated orbital electron capture and of the  $\beta^-$  decay of hydrogen-like  $^{142}\text{Pm}^{60+}$  ions*, Physics Letters B 726 (4-5) 638–645 (2013).

**ENVIE D'EN SAVOIR PLUS SUR

LE TRAITEMENT DE SIGNAL ?**

Découvrez nos articles sur notre base

documentaire Connect :

CONNECT.ED-DIAMOND.COM

# EFFORT MAXIMUM : OPENBSD SUR UNE CARTE RISC-V 1 GHZ/1 GPIO À 30 €

Denis Bodor

Dans un précédent édito, je râlais (comment ça, « comme toujours » ?) à propos de l'absence de « leader » dans le monde des SBC RISC-V, qui permettrait, à l'instar de Raspberry Pi, d'avoir au moins une plateforme de référence pour l'ensemble des projets open source. Pour asseoir ma plainte et démontrer cette carence, j'ai décidé d'opter pour une petite séance de masochisme en mode « poisson globe roulé sous les aisselles » en me penchant sur le SBC MangoPi MQ-Pro D1 pour y installer un OS qu'on trouve rarement dans l'embarqué...

– Effort maximum : OpenBSD sur une carte RISC-V 1 GHz/1 Gio à 30 € –

Ce qui est condensé ici est le résultat de trois jours d'essais, de fausses joies, de déception et, au final, d'une bonne dose de dopamine. Pourquoi ? Parce que même si l'on trouve facilement cette carte pour environ 30 € sur AliExpress (~27 € avec 512 Mio de RAM et ~32 avec 1024 Mio), elle est déjà plus ou moins obsolète. Pas techniquement et matériellement bien sûr, surtout vu son prix, mais de fait, elle est clairement « abandonnée ». Le SoC qui est à la base de cette carte est un Allwinner D1 à cœur (au singulier) RISC-V XuanTie C906. Ce nom vous rappelle-t-il quelque chose ? C'est normal, nous l'avons évoqué dans un précédent article sur la minuscule Milk-V Duo [1], intégrant un SoC CVITEK CV1800B comprenant deux de ces processeurs... pour 8 €. Ce n'est pas tout. Très classiquement, le BSP du fondeur du SoC, appelé Tina Linux, est disponible via des dépôts GitHub [2], mais ceux-ci sont « archivés » (en lecture seule) depuis janvier 2024. La page officielle de MangoPi, elle, référence une distribution Armbian de 2022, téléchargeable via un cloud chinois, ainsi qu'un dépôt GitHub qui n'a pas bougé depuis des années.

Bref, à ce stade il est clair qu'on est dans le très classique syndrome type *fire'n'forget* : « voici une carte, voilà un système qui fonctionne dessus et nous, on passe à autre chose ».

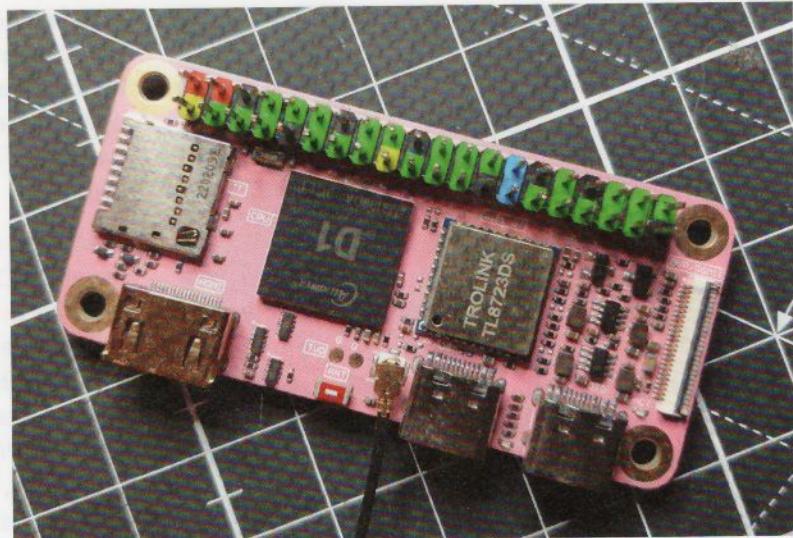

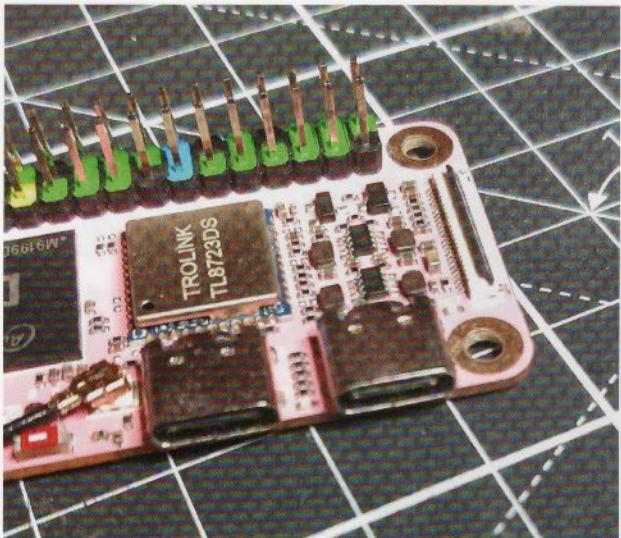

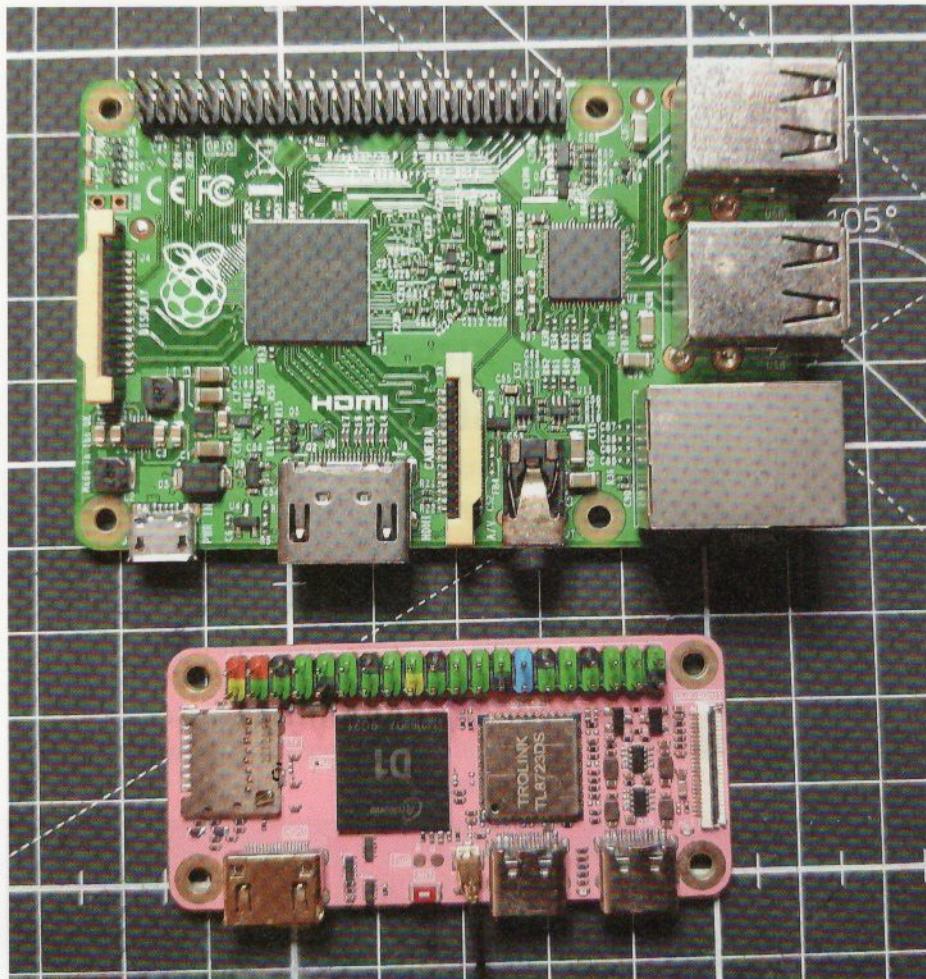

Pour 30 € cependant, nous avons là un objet très intéressant : une carte au format Raspberry Pi Zero, avec un SoC RISC-V à 1,0 GHz, 1 Gio de RAM, une sortie mini HDMI, un chip Wi-Fi/BT (avec antenne), 40 broches avec GPIO, deux ports USB-C (un hôte et un OTG) et l'indispensable emplacement pour microSD. Le rapport ressources/prix est déjà plaisant, mais lorsqu'on ajoute à cela le caractère « exotique » de pouvoir utiliser un « vrai » système (pas un RTOS) sur une architecture RISC-V, c'est difficile de ne pas céder à la tentation. Et, cerise sur le gâteau, cette carte est listée sur la page « riscv64 » du projet OpenBSD [3].

Utiliser une distribution GNU/Linux n'est pas vraiment un challenge ni une démonstration, c'est le système généralement choisi par les constructeurs pour accompagner leurs produits et il n'y a donc pas grand-chose à apprendre au passage, si l'on se contente d'utiliser ce qui existe. Si déjà on sort des sentiers battus en s'éloignant du coutumier ARM, autant se tourner vers un système qui est à la fois sobre, carré et avec une philosophie qui, il n'y a pas si longtemps, était aussi celle strictement appliquée par GNU/Linux (oui, je parle de KISS [4]). Et à ces superlatifs s'ajoute également, dans le cas d'OpenBSD, celui de « spartiate », dans le bon sens du terme (avec les abdos, les barbes et le « réalisme historique » de Zack Snyder (sarcasmes)). Cette carte est l'une des 5 listées sur la page, on peut donc supposer que c'est une plateforme choisie pour être une référence, mais comme nous allons le voir, dans le petit monde RISC-V les choses ne sont pas aussi simples. À noter au passage, FreeBSD propose également un ancien début de support fonctionnel pour le D1, mais là encore, le dépôt [5] est archivé depuis début 2024 et le système ne démarre que sur un RAMdisk, pas avec un *rootfs* sur SD.

## 1. C'EST PARTI !

En jetant un œil aux notes d'installation d'OpenBSD/riscv64 7.5 [6], on se rend rapidement compte que le support est très préliminaire. Plus exactement, l'installation se fait théoriquement en démarrant le système sur une microSD initialisée avec le système du constructeur. L'idée ici est d'utiliser le *bootloader*, ou plus exactement les *bootloaders* déjà présents

pour ensuite démarrer l'installation (chargeur EFI, noyau OpenBSD et installateur) depuis une clé USB et non la microSD, un peu comme démarrer une distribution GNU/Linux *live* depuis GRUB-uEFI sur PC.

Comme avec de nombreuses plateformes embarquées, le démarrage initial est géré par U-Boot, qui fait bien plus que de simplement charger un noyau et lui passer le relais. Dans sa configuration la plus complète, U-Boot sait parfaitement prendre en charge plusieurs types de média ( $\mu$ SM, USB, réseau, etc.) et systèmes de fichiers, tout en permettant l'utilisation de scripts de configuration relativement avancés. Mais sur RISC-V, U-Boot n'arrive que tardivement dans la séquence de *boot* qui prend la forme suivante : *bootcode* en ROM, chargeur (ou SPL), OpenSBI, *bootloader* (U-Boot), noyau OS, etc.

OpenSBI est spécifique aux plateformes RISC-V et est une implémentation de référence *open source* pour la SBI ou *Supervisor Binary Interface* RISC-V. Il s'agit d'une API et d'une couche d'abstraction permettant l'implémentation portable du mode dit « superviseur » (*S-mode*) dans lequel fonctionne le noyau du système d'exploitation ou l'hyperviseur dans un environnement virtualisé (*VS-mode*).

Le mode de plus bas niveau dit « machine » (*M-mode*), autrement dit le mode offrant le maximum de priviléges, est celui dans lequel fonctionne l'implémentation SBI et est désigné par l'acronyme SEE pour *Supervisor Execution Environment*. Cet élément est spécifique à la plateforme, mais offre une interface normalisée pour le système d'exploitation (*S-mode*) qui lui-même contrôle l'exécution des applications en espace utilisateur (*U-mode*). Grossièrement, l'architecture est similaire à la notion de *rings* du monde x86 ou d'*exception levels* (EL3 à EL0) d'ARM. Notez au passage que les EL d'ARM ont un ordre inverse des *rings* x86 avec EL0 pour les applications, EL1 pour le noyau, EL2 pour l'hyperviseur et EL3 pour le mode moniteur (généralement *Trustzone*). RISC-V se débarrasse de cette problématique de classement parfois peu intuitive en utilisant des désignations non numériques.

Le mécanisme d'installation d'OpenBSD part du principe de réutiliser cette chaîne de démarrage jusqu'à U-Boot pour ensuite, via quelques scripts déjà présents dans sa configuration, basculer sur le système d'installation (chargeur EFI + noyau + RAMdisk) mis à disposition via une clé de stockage USB. Sur le papier, c'est très bien, mais on utilise un morceau de système dont nous n'avons pas la maîtrise et, de fait, qui est

susceptible de changer en provoquant des problèmes de compatibilité. Et c'est précisément ce qui arrive, car en tentant l'opération avec l'image Armbian disponible pour la MangoPi MQ-Pro, le processus ne fonctionne pas. Quelque chose est cassé entre ce que faisait la chaîne de *boot* avant, et ce qu'elle fait maintenant. Et dieu sait que j'ai testé bien des combinaisons de binaires et bien des déclinaisons de DTB (*Device Tree Blob*, la structure de données décrivant les périphériques non détectables automatiquement pour une plateforme précise).

Dans cette situation, il ne reste qu'une seule solution : ne pas reposer sur du binaire existant et recomplier les éléments de la chaîne de *boot* à la main, pour créer un contenu minimal pour la carte microSD et pouvoir démarrer le processus d'installation...

## 2. PRÉPARATION DE LA MICROSD

Les spécifications UEFI ou *Unified Extensible Firmware Interface* sont devenues la norme dans le monde x86/amd64/x86\_64 et c'est également de plus en plus le cas dans l'embarqué, avec les SBC ARM en particulier.

– Effort maximum : OpenBSD sur une carte RISC-V 1 GHz/1 Gio à 30 € –

Les plateformes RISC-V n'échappent pas au phénomène, car cette approche permet d'avoir une API stable permettant de développer des chargeurs en minimisant la dépendance au matériel. Le système (le noyau) est donc de moins en moins souvent chargé directement par U-Boot, qui se contente de charger un binaire EFI qui lui s'occupe du reste des opérations, exactement comme c'est le cas sur PC.

Ce binaire ([bootriscv64.efi](#) pour RISC-V, [bootaa64.efi](#) pour AARCH64, [bootx64.efi](#) sur x86\_64, etc.) réside généralement dans une arborescence ([EFI/boot/](#)) dans un système de fichiers FAT16/FAT32 présent dans une partition de type **0B** (Win95 FAT-32) en MBR ou **EE/EF** (EFI GPT / UEFI) en GPT. Ce système de fichiers est présent, quelle que soit l'architecture utilisée, dès lors qu'UEFI est utilisé (y compris sur votre PC). Ceci va beaucoup plus loin que les simples binaires susnommés, avec des choses comme Clover [7] qui me permet de démarrer Devuan GNU/Linux, FreeBSD, NetBSD et OpenBSD en *quadruple boot* sur mon vieux MacBook A1278, ou tout simplement GRUB/EFI, l'implémentation UEFI du célèbre *bootloader*. UEFI permet, techniquement, de développer un OS dont la tâche principale est de *booter* un autre OS.

Pour créer une microSD qui sera, à l'avenir, capable de démarrer automatiquement, nous devons d'ores et déjà préparer ce support en incluant cette partition et ce système de fichiers. Notre microSD jouera deux rôles : permettre le

démarrage du système pour l'installation d'OpenBSD en nous donnant accès à l'interface d'U-Boot, puis une fois le système installé, charger ce système sans intervention de notre part.

Comprenez bien que le partitionnement de la microSD avant d'installer le/les *bootloader*(s) est une manœuvre pour nous faciliter la vie et simplifier le processus d'installation. Cette préparation des partitions de la microSD, ainsi que les compilations qui vont suivre, sont ici décrites pour OpenBSD, mais sont tout à fait applicables avec un autre système d'exploitation, à condition qu'il s'agisse d'un OS digne de ce nom (un Unix libre, donc). Il suffira de désigner les périphériques de stockage avec leurs bons noms et d'utiliser un compilateur croisé adapté au système (testé avec FreeBSD et le préfixe **riscv64-none-elf-** (paquets **riscv64-none-elf-gcc/riscv64-none-elf-binutils**)). La configuration des labels nécessite un système sachant les manipuler, mais ceci peut également être fait durant le processus

**Le SBC MangoPi MQ-Pro D1 se présente sous le même format que le Raspberry Pi Zero, mais se caractérise par deux points notables, le SoC est basé sur un processeur RISC-V et la carte est violemment rose bonbon ! Quel rapport avec une mangue ? Mystère...**

Deux ports USB-C sont accessibles sur la carte. Celui de gauche est USB hôte uniquement, mais celui de droite est OTG. Il peut donc jouer le rôle d'hôte ou de périphérique selon la configuration appliquée, comme votre smartphone.

d'installation qui inclut une étape de partitionnement. Créer au minimum la partition pour UEFI au tout début, comme ici, est toutefois la meilleure approche, et cela peut être fait avec GParted sous Raspberry Pi OS, par exemple, sans le moindre problème.

L'image d'installation, `install75.img` fournie via le CDN OpenBSD [8], qui est un système bootable (`miniroot75.img`) utilisant un RAMdisk en guise de racine accompagné des sets d'installation (également présents dans le même répertoire du site), utilise un partitionnement MBR et non GPT. Pour minimiser le risque d'éventuels problèmes, nous allons utiliser la même chose pour préparer la microSD, glissée dans un lecteur USB connecté à une machine OpenBSD.

Nous commençons par créer une nouvelle table de partition MBR avec :

```

# fdisk -i sd2

Do you wish to write new MBR? [n] y

Writing MBR at offset 0.

```

Nous pouvons ensuite commencer le partitionnement en utilisant le mode interactif de la même commande :

```

# fdisk -e sd2

Enter 'help' for information

```

L'option `-i` nous aura créé automatiquement une partition 3 de type `A6` pour OpenBSD occupant la totalité de l'espace disponible. Ce n'est pas ce que nous voulons, et nous la supprimons avec la commande `e 3`, pour « éditer la partition 3 ». Attribuer un type `00` supprime la partition, et c'est ce que nous faisons.

L'étape suivante consistera à créer la partition destinée à accueillir le système de fichiers FAT pour le binaire EFI. Nous ne pouvons cependant pas créer cette partition n'importe où, car la chaîne de boot (SPL + OpenSBI + U-Boot) doit être placée en début de « disque », juste après la table de partition. Notre partition EFI doit donc démarrer assez loin pour ne pas gêner ces éléments. Nous choisissons donc de placer la première partition à quelque 10 Mio du début du support en éditant 0 avec `e 0` :

```

Partition id ('0' to disable) [01 - FF]: [00] (? for help) 0B

Do you wish to edit in CHS mode? [n]

Partition offset [0 - 7744511]: [0] 20480

Partition size [1 - 7724032]: [1] 102400

```

– Effort maximum : OpenBSD sur une carte RISC-V 1 GHz/1 Gio à 30 € –

Le type à choisir est **0B** (« Win95 FAT-32 ») avec un décalage de 20480 secteurs de 512 octets ( $20480 \times 512 / 1024 = 10$  Mio) et une taille de 50 Mio (102400 secteurs). Puisque nous sommes dans l'édition de partitions, autant immédiatement prévoir celle pour le système. Nous en ajoutons donc une nouvelle, type **A6**, occupant le reste du disque :

```

Partition id ('0' to disable) [01 - FF]: [00] (? for help) A6

Do you wish to edit in CHS mode? [n]

Partition offset [0 - 7744511]: [0] 122880

Partition size [1 - 7621632]: [1] 7621632

```

Voici ce que nous obtenons :

```

sd2*: 1> p

Disk: sd2      geometry: 482/255/63 [7744512 Sectors]

Offset: 0      Signature: 0xAA55

Starting     Ending     LBA Info:

#: id  C   H   S -   C   H   S [ start:    size ]

-----

0: 0B  1 70   6 -   7 165  30 [ 20480: 102400 ] Win95 FAT-32

1: A6  7 165  31 - 482  18  48 [ 122880: 7621632 ] OpenBSD

2: 00  0   0   0 -   0   0   0 [        0:        0 ] Unused

3: 00  0   0   0 -   0   0   0 [        0:        0 ] Unused

```

Et finalement, nous inscrivons tout cela sur le support en quittant avec **q** (ou **w** puis **ex**).

OpenBSD, contrairement à d'autres systèmes de type UNIX (je pense à GNU/Linux), utilise deux notions différentes pour le terme « partition ». Nous avons d'une part ce que nous venons de faire et, de l'autre, les partitions de système de fichiers ou *disklabel partition*, parfois simplement nommée « labels ». Une unique partition MBR (ou GPT) dédiée à OpenBSD peut contenir plusieurs labels permettant d'accueillir les systèmes de fichiers montés par le système. Traditionnellement et par convention, les labels « *a* », « *b* » et « *c* » ont des rôles prédéterminés, respectivement, le *rootfs*, la *swap* et « *c* » désignant le disque dans son ensemble.

Comme pour les partitions MBR (*slices* dans le jargon FreeBSD), les labels ne sont que des noms référençant des zones du support de stockage. Si nous éditons interactivement les labels avec **disklabel -E**, nous voyons immédiatement :

```

# disklabel -E sd2

Label editor (enter '?' for help at any prompt)

sd2> p

OpenBSD area: 122880-7744512; size: 7621632; free: 7621632

#          size      offset  fstype [fsize bsize  cpg]

c: 7744512              0  unused

i: 102400      20480  MSDOS

sd2>

```

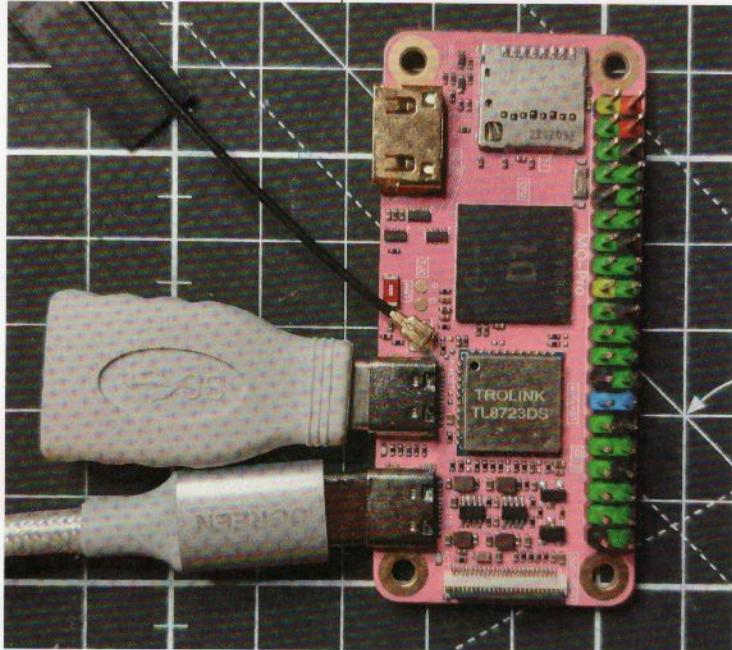

*La proximité des deux connecteurs USB-C peut être un problème avec certains adaptateurs (ou changeur de genre) USB OTG. On voit clairement ici que forcer la connexion appliquerait une force non négligeable susceptible d'endommager la carte. Heureusement, il est parfaitement possible d'alimenter le SBC directement en +5 V via le connecteur 40 broches.*

**c** est la totalité du disque et **i** est notre partition EFI référencée ici sous forme de label. Nous pouvons alors ajouter un label **a** pour notre système de fichiers racine (nous n'avons pas besoin de *swap*) et enregistrons le tout avec :

```

sd2> a a

offset: [122880]

size: [7621632]

FS type: [4.2BSD]

sd2*> p

OpenBSD area: 122880-7744512; size: 7621632; free: 0

#          size   offset  fstype [fsize bsize  cpg]

a:    7621632   122880  4.2BSD   2048 16384     1

c: 7744512          0  unused

i:   102400   20480   MSDOS

sd2*> q

Write new label?: [y]

```

Et tant qu'on y est, on en profite pour créer le système de fichiers FAT qui accueillera le ou les binaire(s) EFI plus tard :

```

$ doas newfs_msdos sd2i

/dev/rsd2i: 102164 sectors in

25541 FAT16 clusters (2048 bytes/cluster)

bps=512 spc=4 res=1 nft=2 rde=512 mid=0xf8

spf=100 spt=63 hds=255 hid=20480 bsec=102400

```

Notez la désignation utilisée, **sd2i** référençant le label « **i** » du disque SCSI (**sd**) numéro **2**.

### 3. CONSTRUCTION DE LA CHAÎNE DE BOOT

Comme dit précédemment, alors que la documentation OpenBSD recommande d'utiliser une microSD inscrite avec l'image fournie par le constructeur (un système GNU/Linux, donc), nous allons tout reconstruire à la main. On peut supposer que, à un moment, l'approche de la documentation a fonctionné, mais les briques évoluant individuellement sans grande cohérence, quelque chose s'est cassé dans les dépendances. Le processus

– Effort maximum : OpenBSD sur une carte RISC-V 1 GHz/1 Gio à 30 € –

de *boot* est bien plus complexe que ce que j'ai décrit en début d'article, avec chaque élément initialisant certaines fonctionnalités et passant des informations à la brique suivante. On retrouve, de-ci de-là, des rapports de *bugs* (ou *issues* sur GitHub) signalant ces incompatibilités et les mêmes symptômes qu'on constate lorsqu'on suit la procédure standard (non-initialisation des périphériques, plantage immédiat du noyau, erreur mémoire, blocage en plein milieu du *boot*, message signalant qu'on n'a pas de RAM (?!), etc.).

Nous compilerons le nécessaire ici exactement comme nous avons partitionné la microSD : sous OpenBSD. Tout ce qu'il nous faut, c'est un compilateur croisé RISC-V et quelques outils habituels (GNU Make, Git, etc.). Ceci s'obtiendra très facilement sous OpenBSD en installant des paquets binaires avec :

```

$ doas pkg_add riscv-elf-binutils riscv-elf-gcc \

riscv-elf-newlib swig gmake git

```

Historiquement, et comme décrit sur le wiki *sunxi* [9], il était nécessaire de construire le SPL (*Secondary Program Loader* exécuté juste après le code en ROM), OpenSBI et U-Boot pour ensuite les combiner et les inscrire directement sur la microSD. Depuis fin 2022 cependant (donc après la diffusion de la distribution du constructeur), tout ceci a évolué et un développeur, Samuel Holland, a *forké* et adapté U-Boot pour ce SoC (entre autres). Le SPL fait maintenant directement partie du mécanisme de construction de son *fork* d'U-Boot qui permet également d'intégrer un binaire OpenSBI pour créer une image unique qu'il suffit de transférer, en une fois, sur le support.

La solution ne sera pas, cependant, de simplement compiler les deux éléments, car dans leur configuration de base, le système ne démarrera pas. Nous commençons donc par récupérer les sources d'OpenSBI depuis le dépôt officiel via Git (branche *master*, commit *bb7267a* du 05/07/2024 ici) :

```

$ mkdir kkpart

$ cd kkpart

$ git clone https://github.com/riscv-software-src/opensbi

```

Les versions récentes d'OpenSBI utilisent une interface de configuration Kconfig (comme Linux, ESP-IDF, U-Boot, etc.) et nous allons ajuster le profil par défaut avec :

```

$ cd opensbi

$ gmake CROSS_COMPILE=riscv64-unknown-elf- \

PLATFORM=generic menuconfig

```

Dans l'interface qui se présente, allez dans *Platform Options* et désactivez le support de tous les SoC, sauf **Allwinner D1 support**. Dans *Serial Device Support*, nous pouvons également désactiver la prise en charge des contrôleurs série inutiles, c'est-à-dire tout sauf **8250 UART FDT driver**. Et enfin, dans *Interrupt Controller Support*, nous faisons de même pour tous les pilotes, sauf **Platform Level Interrupt Controller (PLIC) FDT driver**. Ceci fait, quittez l'interface en enregistrant les changements et lancez la construction :

```

$ gmake -j CROSS_COMPILE=riscv64-unknown-elf- \

PLATFORM=generic FW_PIC=y

```

À l'issue de l'opération, vous trouverez, entre autres, le binaire `fw_dynamic.bin` dans le sous-répertoire `build/platform/generic/firmware/`. C'est la version « dynamique » d'OpenSBI (voir `docs/firmware/*.md`), que nous pourrons utiliser avec U-Boot, que nous construisons ensuite :

```

$ cd ..

$ git clone https://github.com/smaeul/u-boot\

-b d1-wip u-boot_smaeul

$ gmake CROSS_COMPILE=riscv64-unknown-elf- \

mangopi_mq_pro_defconfig

```

Nous utilisons ici la branche *d1-wip* de Samuel et la configuration par défaut (`defconfig`) pour la MangoPi MQ-Pro D1. Cependant, comme j'ai rencontré des problèmes avec le *watchdog* (peut-être lié à la lenteur de la microSD utilisée) chargé de redémarrer le système automatiquement s'il se bloque, nous allons le désactiver. Comme avec OpenSBI, une interface Kconfig rend cela très aisés :

```

$ gmake CROSS_COMPILE=riscv64-unknown-elf- \

menuconfig

```

Rendez-vous dans *Device Drivers* puis *Watchdog Timer Support* et désactivez (décochez) l'option *Automatically start watchdog timer*. Ainsi, le *watchdog* ne sera pas armé directement au démarrage. Quittez en enregistrant les changements et lancez la construction :

```

$ gmake CROSS_COMPILE=riscv64-unknown-elf- \

OPENSBI=../opensbi/build/platform/generic/\

firmware/fw_dynamic.bin

```

Nous référençons ici directement le binaire OpenSBI sur la ligne de commande et notez que nous nous abstenons également d'utiliser l'option `-j` de GNU Make, permettant la compilation parallèle. Pour une raison qui reste mystérieuse, il semblerait que les avertissements soient considérés comme des erreurs en parallélisant, du moins sous OpenBSD (le problème ne se pose pas sous FreeBSD). Quoi qu'il en soit, nous obtenons le binaire `boot-sunxi-with-spl.bin` qui est un regroupement des trois éléments, SPL + OpenSBI + U-Boot, que nous pouvons inscrire immédiatement sur le support de stockage avec :

```

$ doas dd if=u-boot-sunxi-with-spl.bin \

of=/dev/sd2c bs=1024 seek=8

939+1 records in

939+1 records out

962077 bytes transferred in 0.730 secs

(1316892 bytes/sec)

```

- Effort maximum : OpenBSD sur une carte RISC-V 1 GHz/1 Gio à 30 € -

*Parmi les caractéristiques notables du MangoPi MQ-Pro D1, on remarquera un connecteur mini HDMI, un module Wi-Fi/BT RTL8723ds, un connecteur U.FL/UMCC pour une antenne Wi-Fi/BT (livrée avec la carte), un connecteur DVP/RGMII pour l'ajout d'une interface Ethernet et vidéo et, à l'arrière, un connecteur DSI/CTP/LVDS pour une caméra ou un écran. La plupart de ces fonctionnalités ne disposent pas encore d'un support pour OpenBSD.*

Les données sont enregistrées à 8 Kio du début du support (pour ne pas écraser le MBR) et font moins de 1 Mio. Nous avons prévu une « marge » de 10 Mio, la partition EFI n'est donc pas impactée. Nous pouvons passer au démarrage de notre adorable carte toute rose...

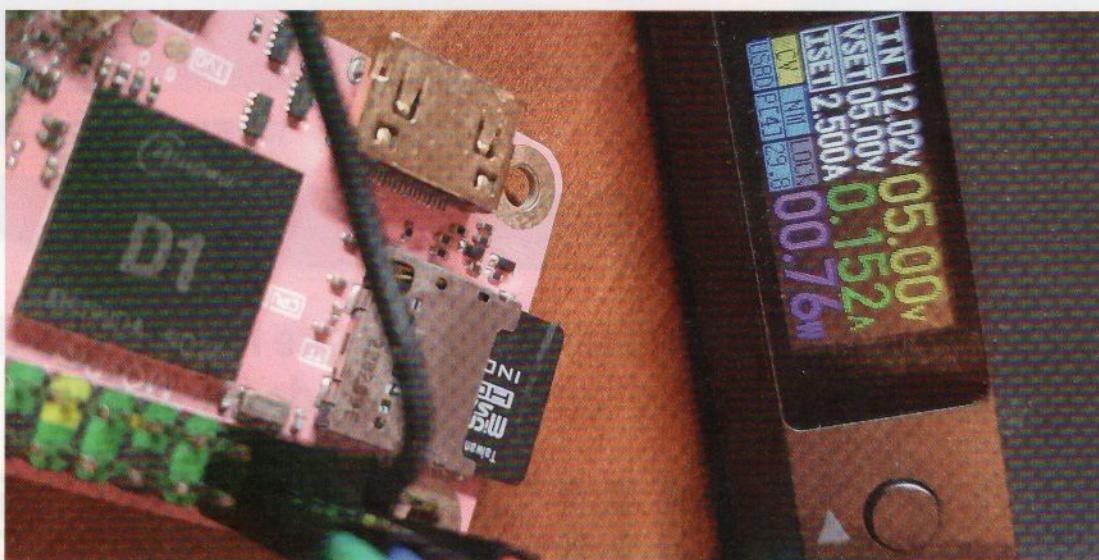

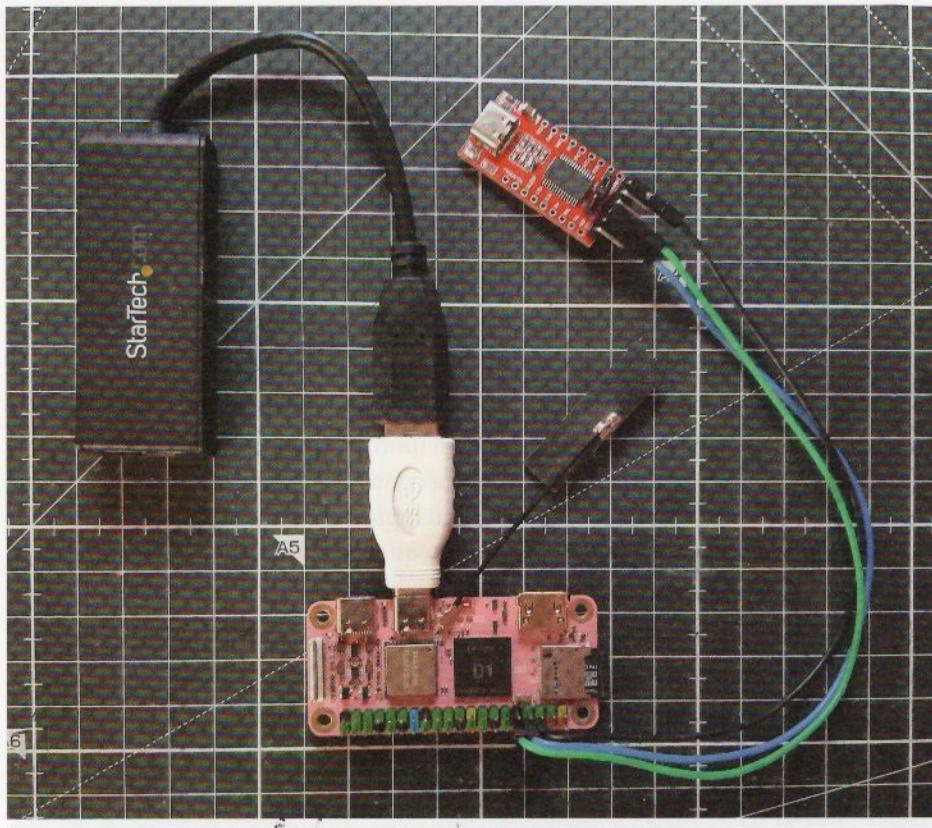

## 4. DÉMARRAGE DE L'INSTALLEUR

Après toutes ces étapes, nous revenons au processus décrit dans la documentation officielle : nous allons utiliser la chaîne de *boot* pour manuellement démarrer un système se trouvant, non pas sur la microSD, mais sur une clé USB. Un adaptateur USB OTG (C vers A femelle) sera nécessaire, ainsi qu'un adaptateur USB/série 3,3 V pour la console (broches 8-TX0 et 10-RX0, plus masse (9)). Étant donnée la proximité des deux connecteurs USB-C, il est parfois difficile de connecter l'alimentation et l'adaptateur OTG sans risquer d'endommager la carte. J'ai donc préféré, finalement, alimenter la Mango en 5 volts via les broches 2 ou 4 (VCCIN) et une masse (6), plutôt que via USB.

La clé USB devra être initialisée avec l'image d'installation **install75.img** et non **miniroot75.img**, car étant donné que nous n'avons pas de réseau dans l'immediat, nous devons disposer des *sets* (composants d'installation) sur un support de stockage. On inscrira l'image avec :

```

$ cd kkpart

$ ftp https://cdn.openbsd.org/pub/OpenBSD/\

7.5/riscv64/install75.img

$ ftp https://cdn.openbsd.org/pub/OpenBSD/\

7.5/riscv64/SHA256.sig

$ signify -C -p /etc/signify/openbsd-75-base.pub

-x SHA256.sig install75.img

Signature Verified

install75.img: OK

$ doas dd if=install75.img of=/dev/rsd2c bs=1m

```

On connectera ensuite la clé via l'adaptateur sur la carte (port USB-C « HOST »), placera la microSD dans le support et connectera l'adaptateur pour la console (115200 8N1) avec Minicom, par exemple. On mettra alors sous tension la carte et verra apparaître les premiers messages de *boot*. Là, vous avez deux secondes pour interrompre la séquence au moment où U-Boot est lancé, en appuyant sur une touche :

```

U-Boot 2024.01-rc1-45338-g2e89b706f5

(Jul 26 2024 - 15:13:00 +0200) Allwinner Technology

DRAM: 1 GiB

Core: 48 devices, 20 uclasses, devicetree: separate

WDT: Not starting watchdog@6011000

MMC: mmc@4020000: 0, mmc@4021000: 1

Loading Environment from FAT...

Unable to read "uboot.env" from mmc0:1...

In:   serial@2500000

Out:  serial@2500000

Err:  serial@2500000

Net:  No ethernet found.

starting USB...

Bus usb@4200000: USB EHCI 1.00

Bus usb@4200400: USB OHCI 1.0

scanning bus usb@4200000 for devices...

2 USB Device(s) found

scanning bus usb@4200400 for devices...

1 USB Device(s) found

scanning usb for storage devices...

1 Storage Device(s) found

Hit any key to stop autoboot: 0

=>

```

Notez que U-Boot détecte bien la présence du stockage USB. À ce stade et parce que nous n'utilisons pas la chaîne de *boot* d'origine, nous pouvons en profiter pour modifier ce délai très court de 2 secondes et enregistrer la modification :

```

=> setenv bootdelay 5

=> saveenv

Saving Environment to FAT... OK

=>

```

- Effort maximum : OpenBSD sur une carte RISC-V 1 GHz/1 Gio à 30 € -

Cette fonctionnalité qui n'est souvent pas présente par défaut nous permet d'enregistrer l'environnement U-Boot dans un fichier `uboot.env` sur la partie FAT de la microSD et ainsi conserver une configuration modifiée d'un démarrage à l'autre. Pour procéder à l'installation, nous n'avons ensuite plus qu'à dire à U-Boot de démarrer sur le support USB. Les scripts intégrés (voir la sortie de la commande `printenv`) se chargent de scanner le périphérique, trouver les éléments nécessaires, charger le binaire EFI et lui passer la main. Tout ceci avec un simple :

```

=> run bootcmd_usb0

[...]

Scanning usb 0:1...

Card did not respond to voltage select! : -110

No EFI system partition

No EFI system partition

Failed to persist EFI variables

BootOrder not defined

EFI boot manager: Cannot load any image

Found EFI removable media binary efi/boot/bootriscv64.efi

148476 bytes read in 13 ms (10.9 MiB/s)

Booting /efi\boot\bootriscv64.efi

disks: sd0* sd1

>> OpenBSD/riscv64 BOOTRISCV64 1.5

boot>

[...]

OpenBSD 7.5 (RAMDISK) #0: Fri Mar 22 19:50:20 MDT 2024

deraadt@riscv64.openbsd.org:

/usr/src/sys/arch/riscv64/compile/RAMDISK

real mem = 1073741824 (1024MB)

avail mem = 1005133824 (958MB)

SBI: OpenSBI v1.5, SBI Specification Version 2.0

[...]

Welcome to the OpenBSD/riscv64 7.5 installation program.

(I)nstall, (U)pgrade, (A)utoinstall or (S)hell?

```

La procédure d'installation est tout à fait standard, tout en considérant que nous n'avons pas de réseau et devons donc préciser où se trouvent les sets. `sd0` désigne la microSD et `sd1` le support USB, et c'est là le seul point où il ne faut pas se mélanger les pinceaux. Concernant le partitionnement, nous n'avons presque rien à faire, si ce n'est, à l'étape de configuration des labels, de spécifier le point de montage avec :

```

sd0> n a

mount point: [none] /

```

Point important, vers la fin de l'installation, OpenBSD va « réorganiser » le noyau pour produire un binaire unique. C'est une fonctionnalité de sécurité appelée KARL et cette génération prend du temps, beaucoup de temps. Ne vous inquiétez donc pas en voyant le message « `Relinking to create unique kernel...` » et rien d'autre pendant un bon bout de temps. C'est normal et ceci débouchera, à un moment, sur :

```

CONGRATULATIONS! Your OpenBSD install has been

successfully completed!

```

```

When you login to your new system the first time,

please read your mail using the 'mail' command.

```

```

Exit to (S)hell, (H)alt or (R)eboot? [reboot]

```

Nous choisissons « h » ici, car le système n'est pas encore (*re)bootable*. Nous avons préparé la microSD avec les *bootloaders* et une zone pour UEFI, mais avons démarré sur USB. Notre microSD ne possède pas le binaire EFI nécessaire. Corrigeons cela avant le premier démarrage.

## 5. INSTALLER LE CHARGEUR EFI ET PREMIER DÉMARRAGE

Placer le chargeur EFI (**bootriscv64.efi**) sur la microSD est un jeu d'enfant puisque nous venons de l'utiliser à l'instant : il suffit de le copier, depuis le système de fichier FAT de la clé USB vers la microSD :

```

# mkdir tmp

# mount /dev/sd2i /mnt

# cp -r /mnt/efi tmp/

# umount /mnt/

```

puis :

```

# mount /dev/sd2i /mnt

# cp -r tmp/efi /mnt/

# umount /mnt/

# rm -rf tmp

```

Comme les scripts U-Boot cherchent automatiquement ce binaire sur les supports scannés et que le premier d'entre eux est la microSD, il nous suffit de remettre la carte dans son emplacement et d'alimenter le tout. Nous verrons alors, comme précédemment, démarrer le système, mais cette fois sur la microSD. Durant le *boot* (et après), vous aurez droit à divers ralentissements :

```

reordering: ld.so  libc libcrypto sshd.

openssl: generating isakmpd RSA keys... done.

openssl: generating iked ECDSA keys... done.

ssh-keygen: generating new host keys: RSA ECDSA ED25519

sshd: (ED25519) SHA256:SeYVtcV1n0KIn7J6zutN736PXzALEJ0+iAy7uVXIM3c

starting early daemons: syslogd pflogd ntpd.

```

## OpenBSD / RISC-V

- Effort maximum : OpenBSD sur une carte RISC-V 1 GHz/1 Gio à 30 € -

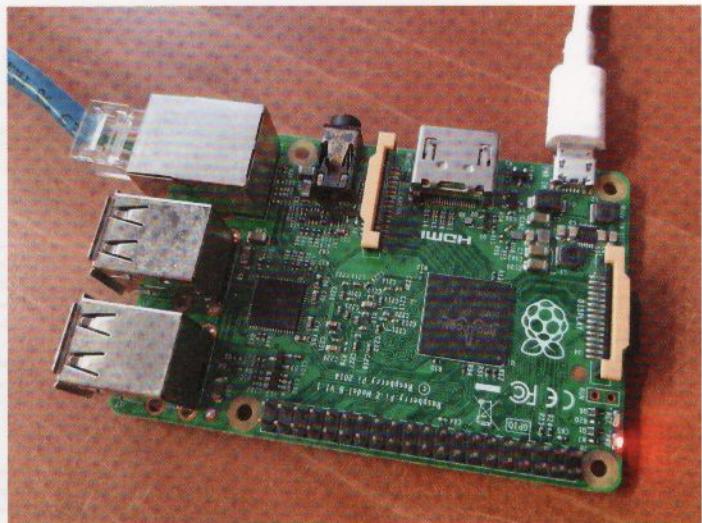

Voici une petite comparaison de taille entre la MangoPi et une très classique Raspberry Pi 2. Au-delà des couleurs et dimensions cependant, rien ne saurait différencier davantage ces deux SBC que l'architecture utilisée : ARM en haut et RISC-V en bas.

Ce **reordering** est un dispositif de sécurité, réorganisant les symboles dans les bibliothèques afin de rendre les attaques plus difficiles. Et ceci sera fait **à chaque démarrage**, ce qui, sur une plateforme embarquée, peut être très pénalisant. Vous pouvez désactiver cela avec :

```

# rcctl disable library_aslr

```

Ce n'est pas tout, le même style de réorganisation est appliqué au noyau (KARL), mais ceci se fait en tâche de fond et augmente la charge système quelques dizaines de secondes après le *boot*. Ceci signifie que le système sera moins réactif dans l'immédiat, ce qui peut également être évité (pour les tests) en utilisant :

```

# sha256 -h /var/db/kernel.SHA256 \

/dev/null

```

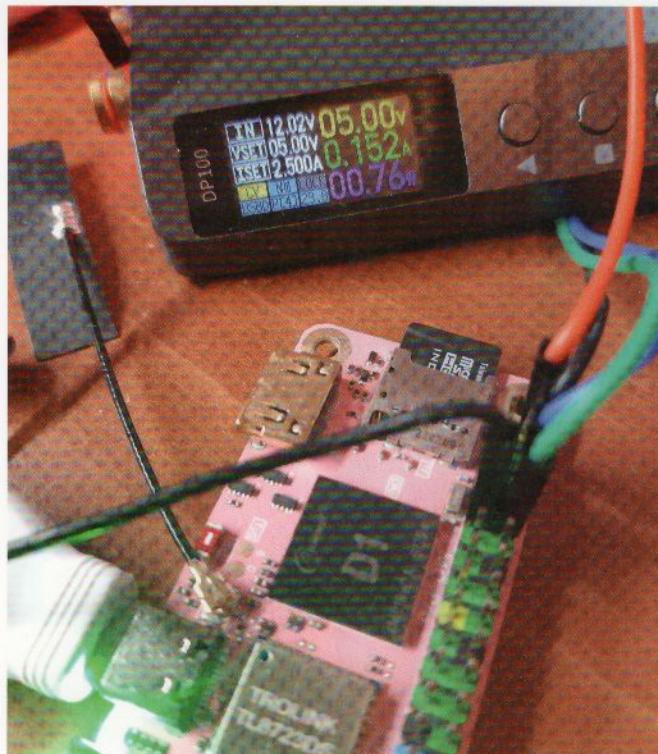

*L'alimentation de la carte via le connecteur 40 broches permet accessoirement d'avoir une idée de sa consommation en temps réel. 150 mA en 5 V pour le système « au repos » est plus que respectable. Chargée, la carte n'a à aucun moment dépassé 2 W lors des tests.*

Notez toutefois que vous aurez droit à un message d'erreur « **reorder\_kernel: failed** » à chaque démarrage. Le fichier de log spécifié dans le message contient la commande permettant de réactiver le mécanisme de sécurité le moment venu.

## 6. AJOUTONS DU RÉSEAU

La MangoPi MQ-Pro D1 ne dispose pas d'interface Ethernet et, pour l'heure, le contrôleur Wi-Fi n'est pas pris en charge. Cependant, rien ne vous empêche de connecter un adaptateur USB/Ethernet puisque le port OTG est disponible. Si le modèle est supporté, vous devrez voir apparaître des messages en conséquence dans la console série :

```

axen0 at uhub0 port 1 configuration 1 interface 0

"ASIX Elec. Corp. AX88179" rev 2.10/1.00 addr 2

axen0: AX88179, address 00:24:9b:77:20:eb

rgephy0 at axen0 phy 3: RTL8169S/8110S/8211 PHY, rev. 5

<code>

```

Et l'interface sera alors également visible avec les outils habituels :

```

<code>

# ifconfig

[...]

axen0: flags=8802<BROADCAST,SIMPLEX,MULTICAST> mtu 1500

lladdr 00:24:9b:77:20:eb

index 4 priority 0 llprio 3

media: Ethernet autoselect (10baseT half-duplex)

status: no carrier

</code>

```

Automatiser la prise en charge est très simple, puisqu'il suffit de créer un fichier **hostname** dans **/etc** avec, comme extension, le nom de l'interface (ici, **axen0**). Pour une configuration automatique via DHCP, le fichier contiendra :

- Effort maximum : OpenBSD sur une carte RISC-V 1 GHz/1 Gio à 30 € -

```

# cat > /etc/hostname.axen0

inet autoconf

^D

```

Et vous pourrez prendre les modifications en compte immédiatement sans avoir à redémarrer avec :

```

# sh /etc/netstart

WARNING: /etc/hostname.axen0

is insecure, fixing permissions.

# ping 8.8.8.8

PING 8.8.8.8 (8.8.8.8): 56 data bytes

64 bytes from 8.8.8.8: icmp_seq=0 ttl=115 time=12.861 ms

64 bytes from 8.8.8.8: icmp_seq=1 ttl=115 time=12.522 ms

64 bytes from 8.8.8.8: icmp_seq=2 ttl=115 time=12.557 ms

^C

```

À présent connecté au réseau, le système est non seulement accessible via SSH, qui est bien plus agréable à utiliser que la console série, mais aussi, et surtout, vous pouvez installer des paquets binaires et commencer à réellement vous amuser :

```

# pkg_add cowsay

quirks-7.14:updatedb-0p0: ok

quirks-7.14 signed on 2024-03-25T22:12:52Z

quirks-7.14: ok

cowsay-0.2.1v0:p5-Text-Template-1.61: ok

cowsay-0.2.1v0: ok

# cowsay "Hackable <3 OpenBSD/RISC-V"

< Hackable <3 OpenBSD/RISC-V >

-----

\  ^__^

(oo)\----_

(__)\       )\/\

||----w |

||     |

```

## CONCLUSION

Maintenir un système pour une carte RISC-V spécifique est presque en tout point similaire à faire de même pour une plateforme de *retrocomputing*. Certes, le matériel est là, accessible à peu de frais (dans certains cas) et un système « officiel » existe, mais celui-ci est d'ores et déjà abandonné (ou le sera dans quelques mois). On se retrouve donc dans une situation où,

le temps que le support soit stabilisé, la carte n'est plus la starlette du moment, remplacée par une autre, plus complète, plus rapide, plus ce que vous voulez. Ceci revient à tenter de faire un magnifique château de sable, juste pour le voir emporté par la marée, à peine prend-il réellement forme. On comprend alors parfaitement pourquoi si peu de systèmes, que ce soit des GNU/Linux *mainstream* ou des alternatives comme [Free | Open | Net]BSD, supportent officiellement et directement certaines cartes et plateformes, préférant souvent se concentrer sur des émulations avec QEMU. De fait, QEMU RISC-V est la plateforme de référence, et même là, comme le précise le site officiel, « *Unfortunately many of the RISC-V boards QEMU supports are currently undocumented* »...

C'est totalement paradoxal, car on ne peut même pas réellement parler de carence en matériel, puisque la gamme de cartes et de SoC est non négligeable. Au contraire, cette impression de « ça part dans tous les sens » fait plus de tort qu'autre chose. Je pense réellement que, tant que cette situation perdurera et qu'aucune plateforme ne se dégagera comme étant la référence, l'architecture RISC-V appliquée aux SBC (ou même aux laptops) n'a que peu de chance de faire de l'ombre à ARM et donc de devenir une alternative réellement viable. Mais j'ai bon espoir, car le phénomène était exactement le même dans l'univers des MCU avant l'arrivée massive des ESP32-C\*... ■ DB

## RÉFÉRENCES

- [1] <https://connect.ed-diamond.com/hackable/hk-054/milk-v-duo-unminuscule-sbc-risc-v-a-8-eu>

- [2] <https://github.com/Tina-Linux>

- [3] <https://www.openbsd.org/riscv64.html>

- [4] [https://fr.wikipedia.org/wiki/Principe\\_KISS](https://fr.wikipedia.org/wiki/Principe_KISS)

- [5] <https://github.com/freebsd-d1/freebsd-d1>

- [6] <https://cdn.openbsd.org/pub/OpenBSD/7.5/riscv64/INSTALL.riscv64>

- [7] <https://sourceforge.net/projects/cloverefiboot/>

- [8] <https://cdn.openbsd.org/pub/OpenBSD/7.5/riscv64/>

- [9] [https://linux-sunxi.org/Allwinner\\_Nezha](https://linux-sunxi.org/Allwinner_Nezha)

## ENVIE D'EN SAVOIR PLUS SUR LE DÉVELOPPEMENT KERNEL OPENBSD ?

Découvrez notre article sur la base documentaire Connect :

CONNECT.ED-DIAMOND.COM

GLMF 269

Écrire son premier pilote pour OpenBSD

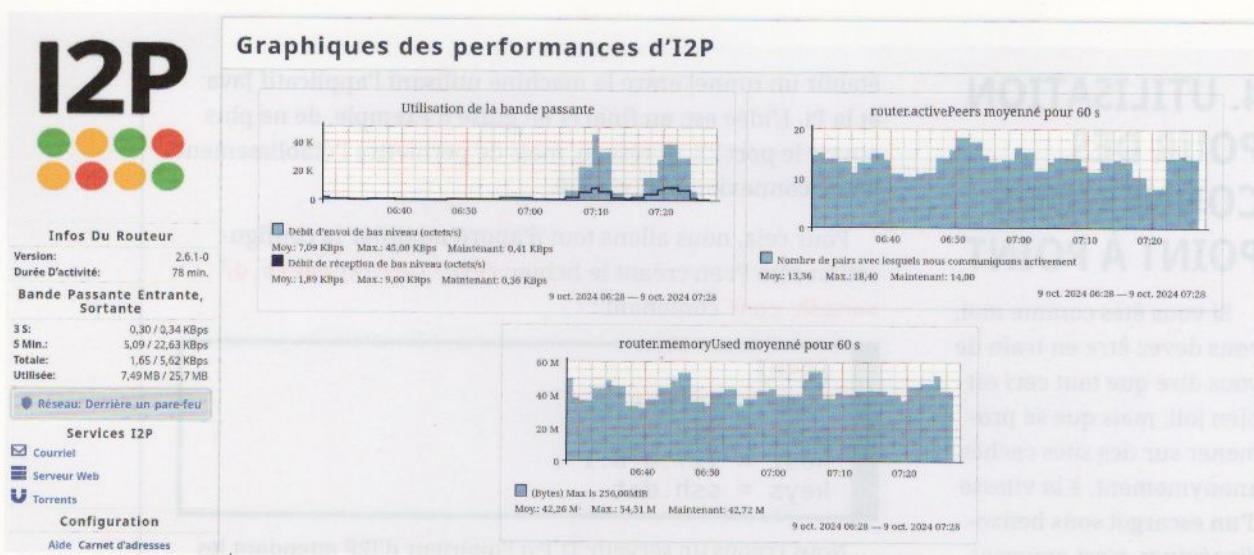

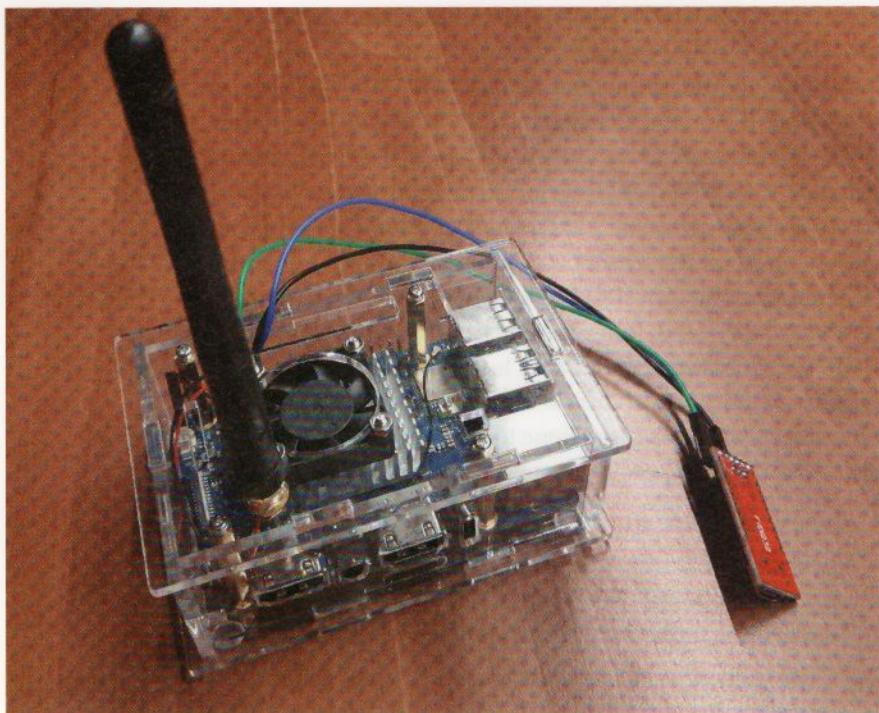

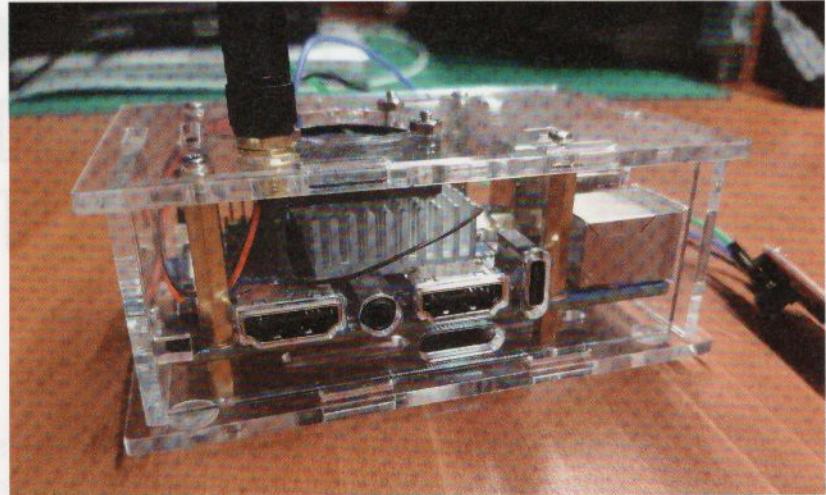

# RPI & I2P : ANONYMISER SON TRAFIC AVEC L'INTERNET INVISIBLE

Denis Bodor

**La surveillance de masse, la censure et les nombreuses restrictions qui pèsent sur Internet, et les communications en général, représentent un énorme problème pour la vie privée et la liberté d'expression.** Bien entendu, en Europe, nous ne sommes certainement pas les moins bien lotis, en particulier en comparaison avec des pays aux régimes totalitaires. Mais le fait de dissimuler ses communications et ses échanges de données n'est pas l'apanage des journalistes, des lanceurs d'alerte, des freedom fighters ou même, à l'autre extrême, des groupes mafieux ou terroristes et des réseaux pédophiles. L'anonymisation, le chiffrement et la dissimulation sont devenus l'affaire de tout un chacun désormais.

– RPi & I2P : anonymiser son trafic avec l'Internet invisible –