ÉLECTRONIQUE | EMBARQUÉ | RADIO | IOT

# HACKABLE

L'EMBARQUÉ À SA SOURCE

N° 58

JANVIER / FÉVRIER 2025

FRANCE MÉTRO.: 14,90 €

BELUX: 15,90 € - CH: 23,90 CHF ESP/IT/PORT-CONT: 14,90 €

DOM/S: 14,90 € - TUN: 35,60 TND - MAR: 165 MAD - CAN: 24,99 \$CAD

L 19338 - 58 - F: 14,90 € - RD

CPPAP : k92470

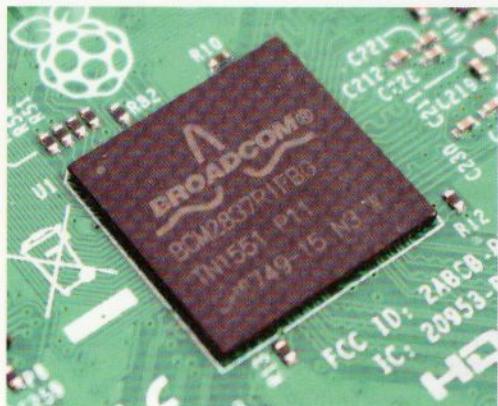

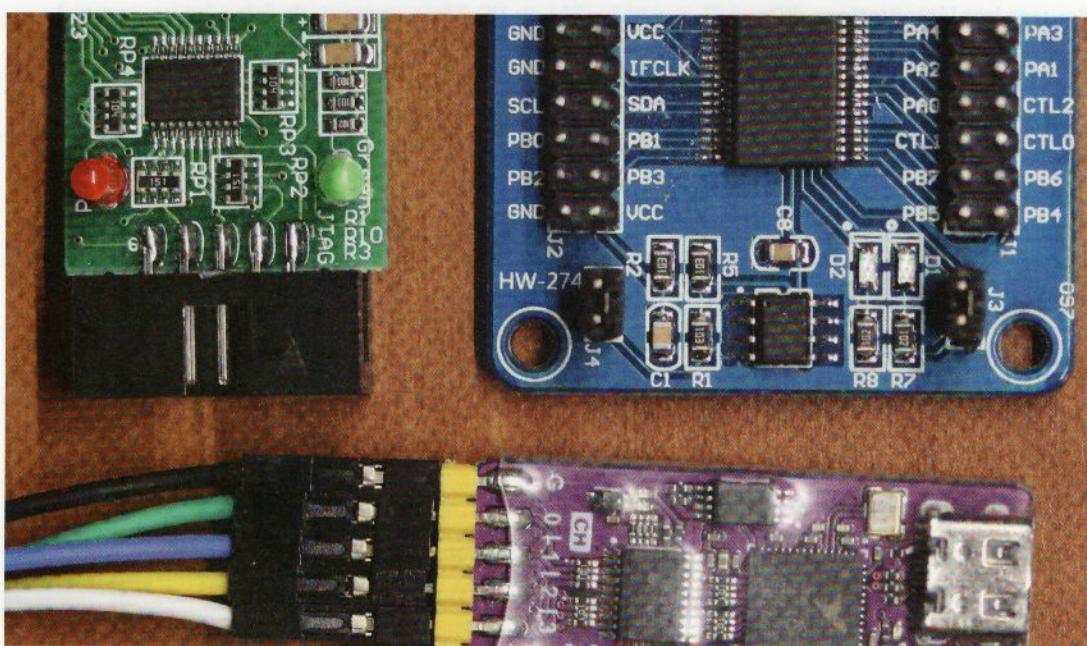

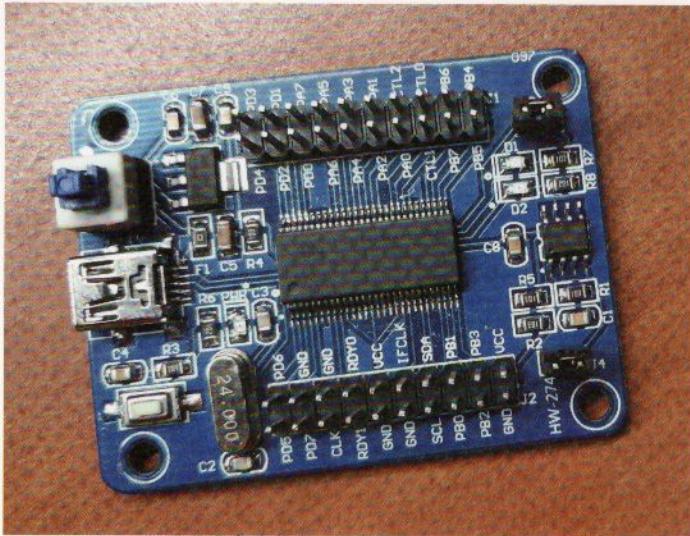

USB / CY7C68013A / C

Créez vos périphériques USB basés sur le **microcontrôleur EZ-USB FX2LP** avec SDCC et LibUSB p.62

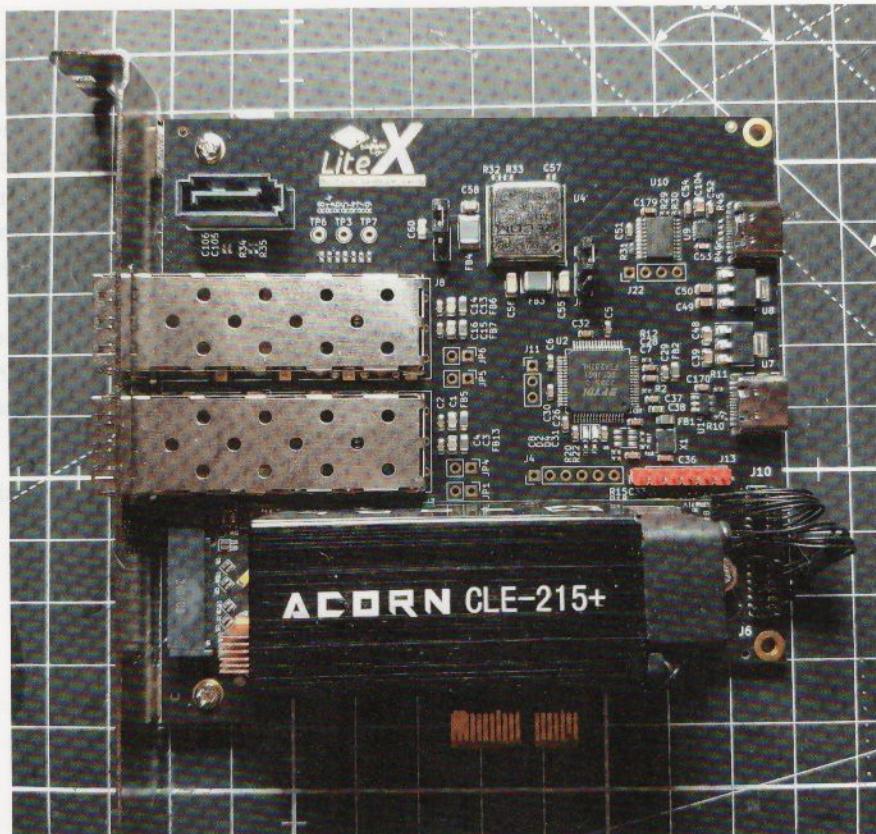

FPGA / FRAMEWORK

Plongeons au cœur de **LiteX** et créons deux **systèmes RISC-V** complets fonctionnant sous Linux p.100

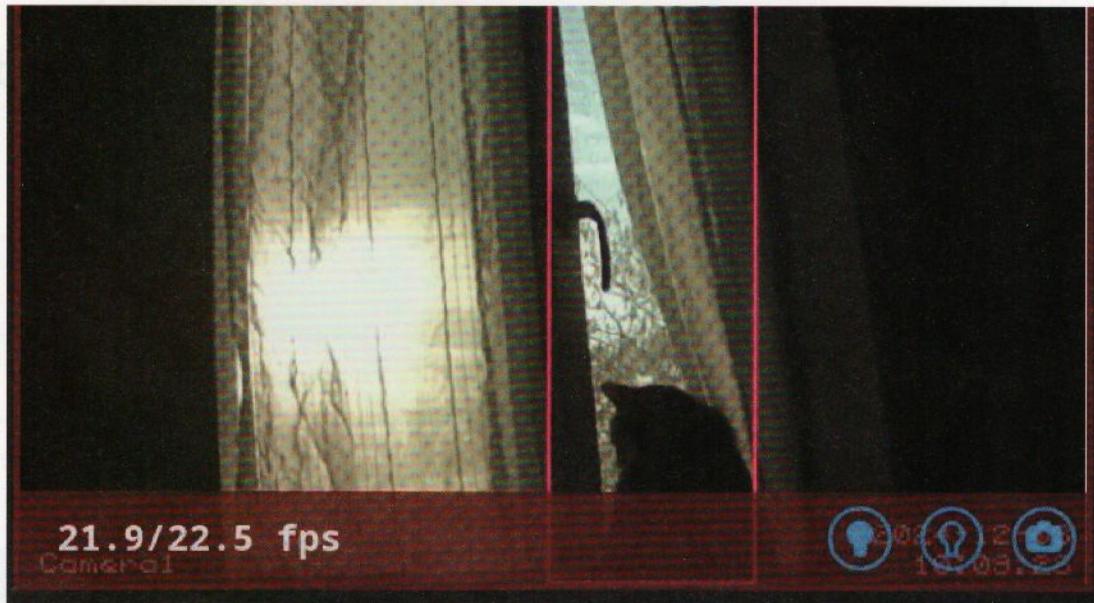

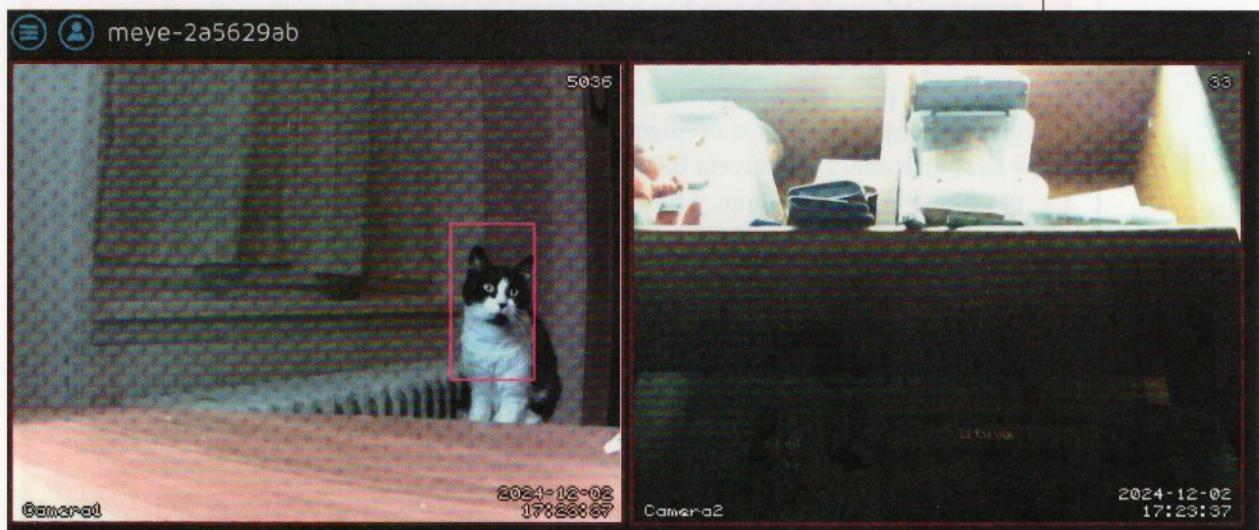

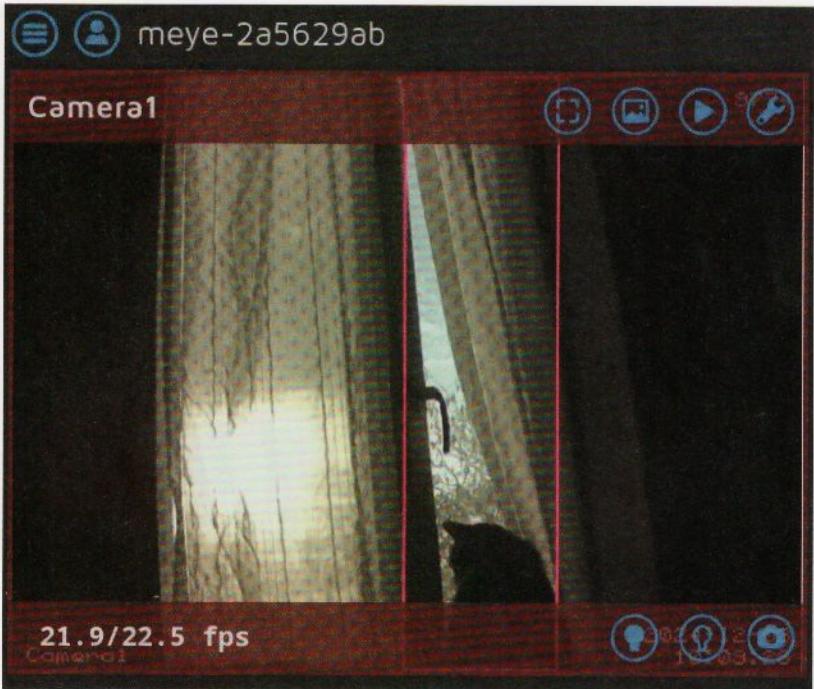

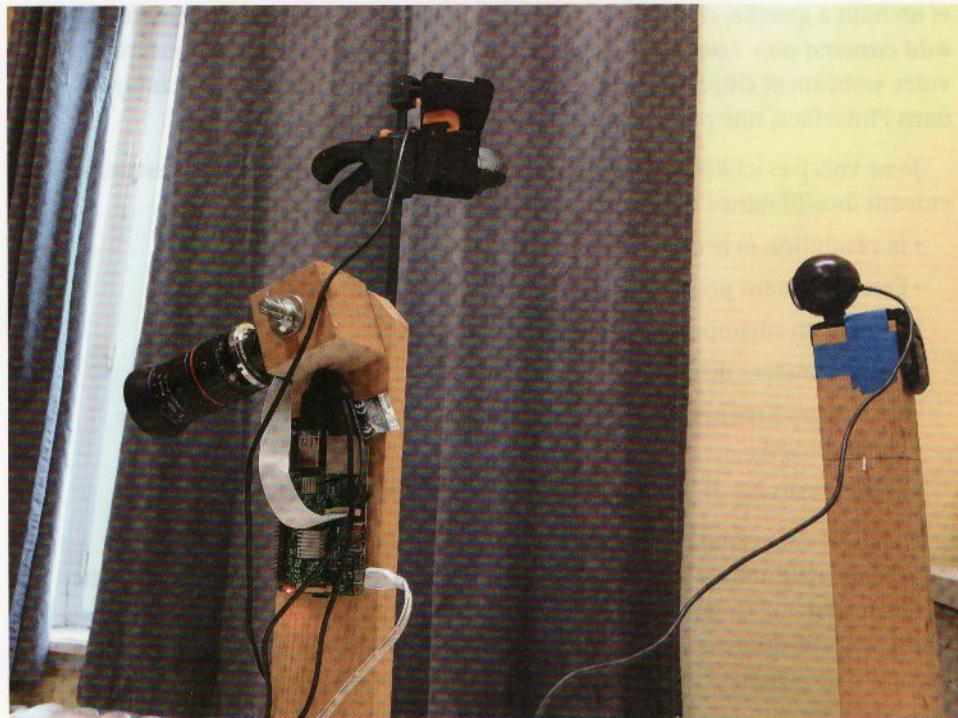

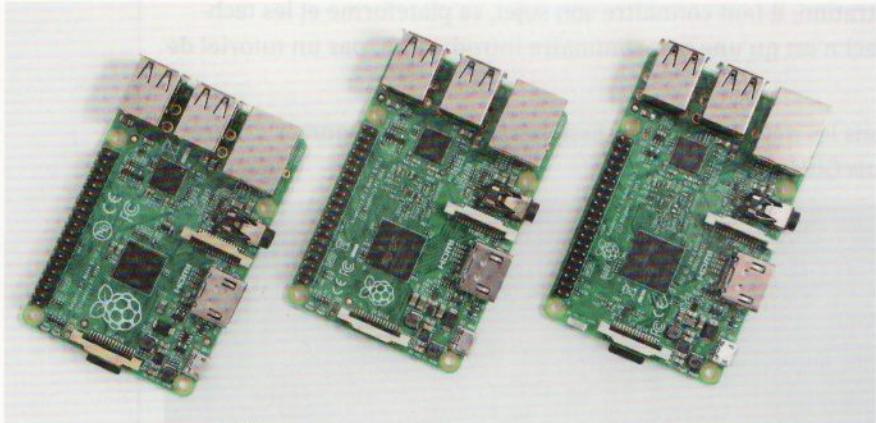

## RASPBERRY PI / CAMERA / MOTIONEYE

Comment garder un œil sur votre habitat **ET** votre vie privée ?

## DOMOTIQUE & VIDÉOSURVEILLANCE

p.38

- Transformez vos Pi en IPcam

- Déetectez les mouvements

- Déclenchez des actions

- Intégrez le tout à Home Assistant

SECURITÉ / CRYPTO

Ajoutez des signatures cryptographiques **ECDSA miniatures** à n'importe quels textes et QRcodes p.80

RPI / GPU / CALCUL

Initiez-vous facilement à la programmation parallèle sur **GPU avec OpenCL** et Raspberry Pi p.50

ACTU / CPU / ASIC

**FSiC 2024** : État de l'art, rétrospective et futurs défis du silicium libre et de la production de circuits intégrés open hardware p.04

**1-2 AVRIL 2025**

**LILLE GRAND PALAIS

FRANCE**

# **LA PREMIÈRE COMPÉTITION EUROPÉENNE DE CYBERSÉCURITÉ !**

L'EC2 est le rendez vous à ne pas manquer, permettant de mêler team building de vos équipes sécurité, marque employeur et communication auprès de l'écosystème cybersécurité français et européen !

Vous serez nombreux mais à la fin il n'en restera qu'un !

L'équipe vainqueur recevra un chèque d'un montant de 5 000 €.

## **ÉPREUVES 2025**

**.01/ CTF**

**.02/ OSINT**

**.03/ FORENSIC**

**.04/ OT**

**.05/ RÉCUPÉRATION DE DONNÉES**

**.06/ BATTLE ROYALE**

**.07/ AD/WINDOWS**

↗ [european-cybercup.com](http://european-cybercup.com)

# JJ ÉDITO

Une vidéo récente sur la chaîne secondaire de Matthias Wandel [1] m'a récemment fait vérifier presque l'ensemble des câbles que j'utilise pour mes montages et autres expériences. En effet, Matthias, qui généralement diffuse du contenu autour du travail du bois, a constaté que ses câbles munis de pinces, achetés très récemment, présentaient une résistance relativement surprenante, quelque 300 mΩ pour 15 cm, ce qui n'est peut-être pas un problème pour des signaux (selon la fréquence), mais en est clairement un pour une alimentation.

Habituellement, il s'agit généralement d'un problème de fabrication au niveau des connexions (en particulier pour les pinces) et ajouter un point de soudure règle le problème. Mais ici, le souci était différent : il s'est finalement avéré que non seulement le nombre de brins était très faible, mais qu'en plus, il ne s'agissait pas du tout de cuivre ou d'aluminium, seulement de fer plaqué cuivre, expliquant totalement les surprenantes mesures. Depuis peu donc, les câbles et clips « chinois », tels qu'on en trouve un peu partout pour peu cher (typiquement AliExpress et consorts), viennent tout juste de drastiquement chuter en qualité...

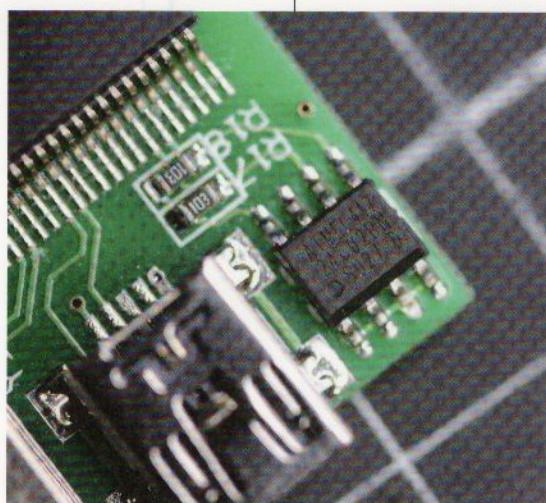

L'astuce accompagnant la vidéo consiste à tout simplement utiliser un aimant néodyme et voir si effectivement nous avons affaire à un alliage ferromagnétique ou non. Et effectivement, j'en avais quelques-uns dans ma collection (dont un clip de test SIOC-8 !). Notez au passage que la vidéo teste ainsi également un câble de souris, mais là, en vérité, ceci est parfaitement normal, c'est le blindage tressé protégeant le câble, pas de quoi s'inquiéter.

Ce qui inquiétant, en revanche, et bien plus que la méfiance d'usage dont il faut toujours faire preuve en achetant à certains endroits du Net, est le fait que ce type de production n'est absolument pas réservé au marché « extérieur ». Les câbles, composants et matériaux bas de gamme, copiés, plagiés à bas coût... infestent également le marché chinois lui-même, se retrouvent « sourcés » pour des produits plus légitimes et impactent également les progrès techniques de ce pays, qui prend déjà ses aises côté sécurité sur d'autres plans (comme les *boosters* de fusées qui retombent de-ci de-là).

C'est une contamination à la source de la chaîne de production, tel qu'on le voit déjà pour les circuits intégrés contrefaits. Tout ceci va, à un moment, tourner très mal...

Denis Bodor

[1] <https://www.youtube.com/watch?v=15sMogK3vTI>

## Hackable Magazine

est édité par Les Éditions Diamond

BP 20142 - 67602 SELESTAT CEDEX - France

E-mail : [lecteurs@hackable.fr](mailto:lecteurs@hackable.fr) -

Service commercial : [cial@ed-diamond.com](mailto:cial@ed-diamond.com)

Sites : [hackable.fr](http://hackable.fr) - [ed-diamond.com](http://ed-diamond.com)

Directeur de publication : Arnaud Metzler

Rédacteur en chef : Denis Bodor

Réalisation graphique : Kathrin Scali

Régie publicitaire :

Valérie Fréchard - Tél. : 03 67 10 00 27

Service abonnement : Les Éditions Diamond

BP 20142 - 67602 SELESTAT CEDEX, France,

Tél. : 03 67 10 00 20

Impression : Westermann Druck | PVA,

Braunschweig, Allemagne

Distribution France :

(uniquement pour les dépositaires de presse)

MLP Réassort : Plate-forme de Saint-Barthélemy-d'Anjou. Tél. : 02 41 27 53 12

Plate-forme de Saint-Quentin-Fallavier.

Tél. : 04 74 82 63 04

Service des ventes :

Abomarque - Tél. : 06 15 46 15 88

IMPRIMÉ en Allemagne - PRINTED in Germany

Dépôt légal : À parution

N° ISSN : 2427-4631

CPPAP : K92470

Périodicité : bimestriel - Prix de vente : 14,90 €

La rédaction n'est pas responsable des textes, illustrations et photos qui lui sont communiqués par leurs auteurs. La reproduction totale ou partielle des articles publiés dans Hackable Magazine est interdite sans accord écrit de la société Les Éditions Diamond. Sauf accord particulier, les manuscrits, photos et dessins adressés à Hackable Magazine, publiés ou non, ne sont ni rendus ni renvoyés. Les indications de prix et d'adresses figurant dans les pages rédactionnelles sont données à titre d'information, sans aucun but publicitaire. Toutes les marques citées dans ce numéro sont déposées par leur propriétaire respectif. Tous les logos représentés dans le magazine sont la propriété de leur ayant droit respectif.

Suivez-nous sur Twitter

@hackablemag

### POUR DEVENIR AUTEUR

Contactez : [contrib@hackable.fr](mailto:contrib@hackable.fr)

Consultez :

## SOMMAIRE

### ACTUALITÉ

04 FSIC2024 : L'Open Silicium décolle à Paris !

### DOMOTIQUE & CAPTEURS

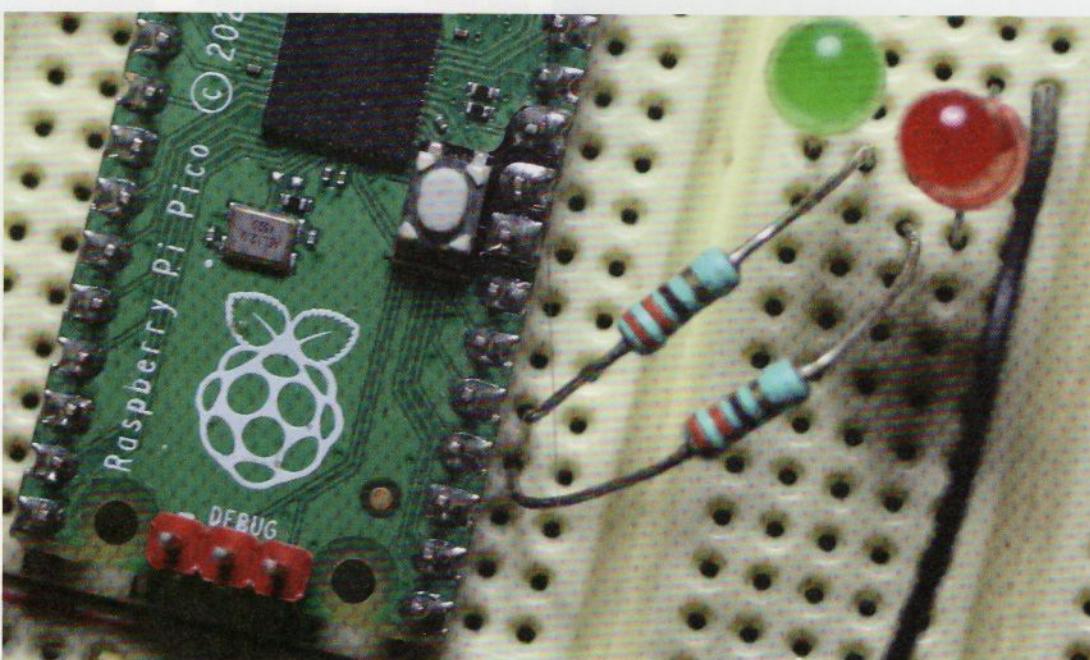

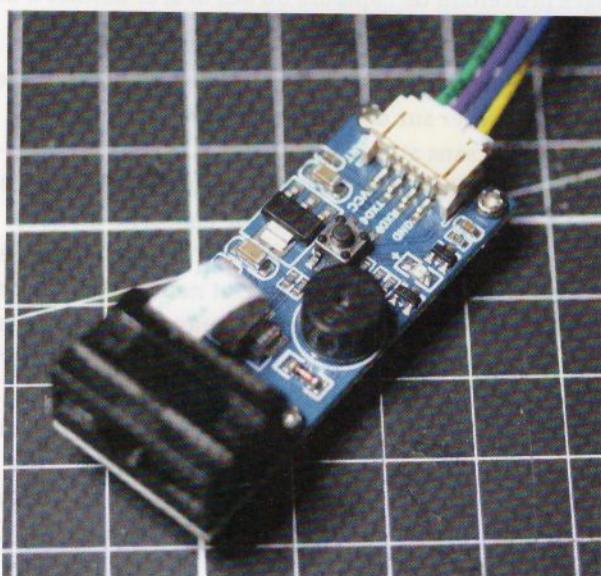

38 Mettre en place une surveillance domotique avec Raspberry Pi

### SBC & RASPBERRY PI

50 S'initier à OpenCL sur Raspberry Pi 3

### MICROCONTROLEURS & ARDUINO

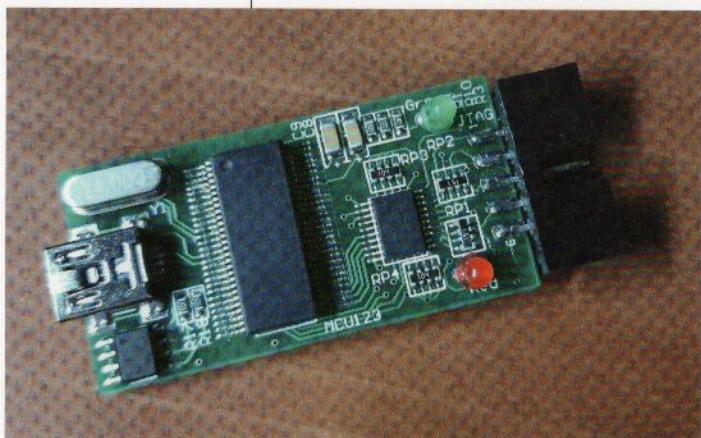

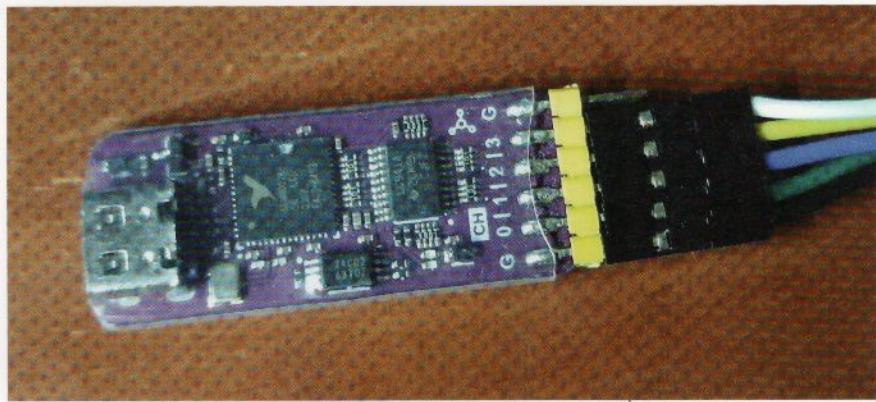

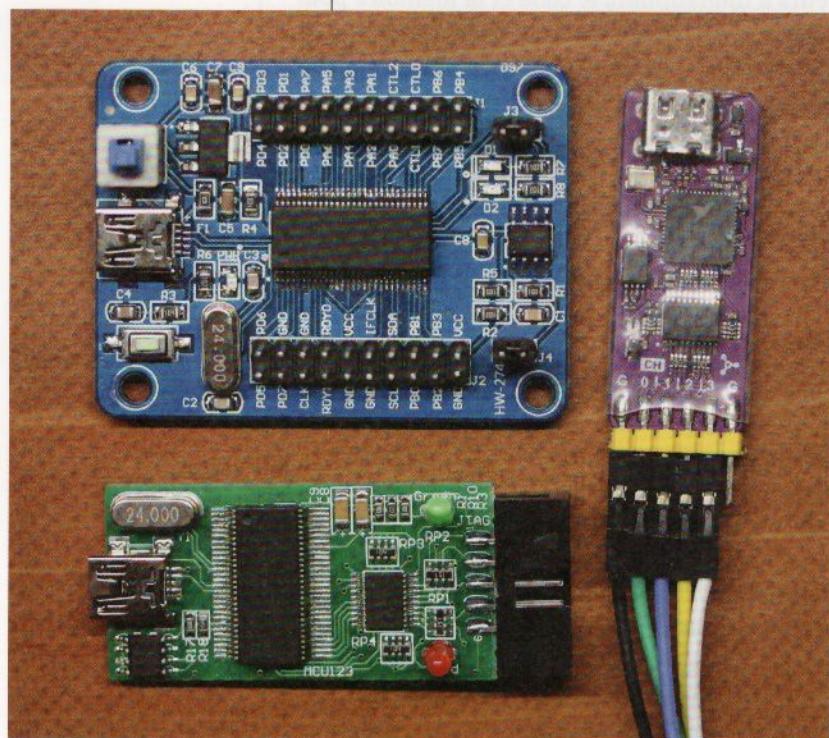

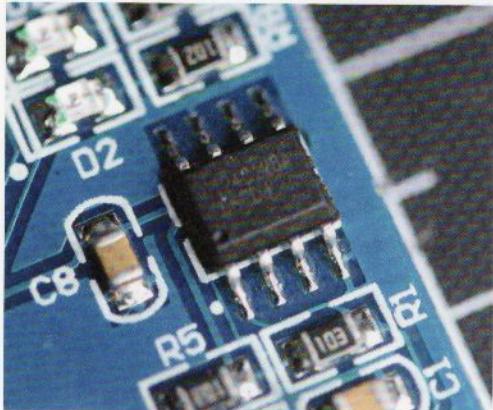

62 FX2LP : une autre solution pour créer des périphériques USB

### SÉCURITÉ

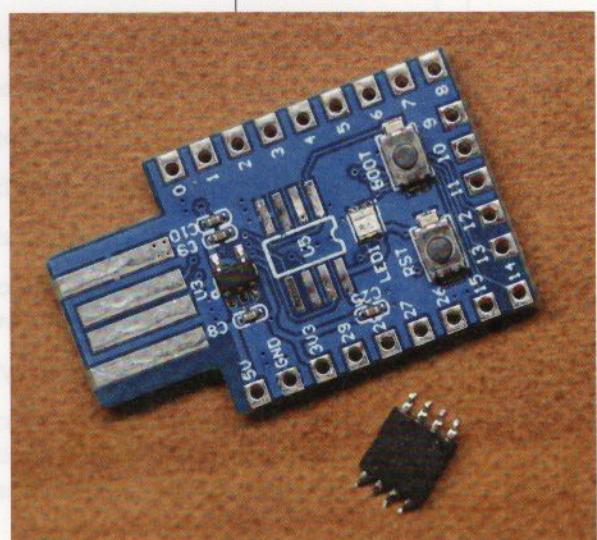

80 Sécuriser tout et n'importe quoi avec des mini-signatures

### FPGA & GATEWARE

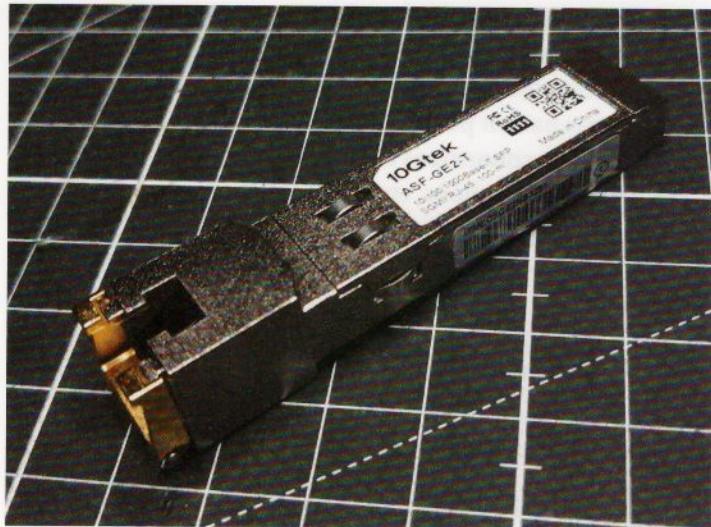

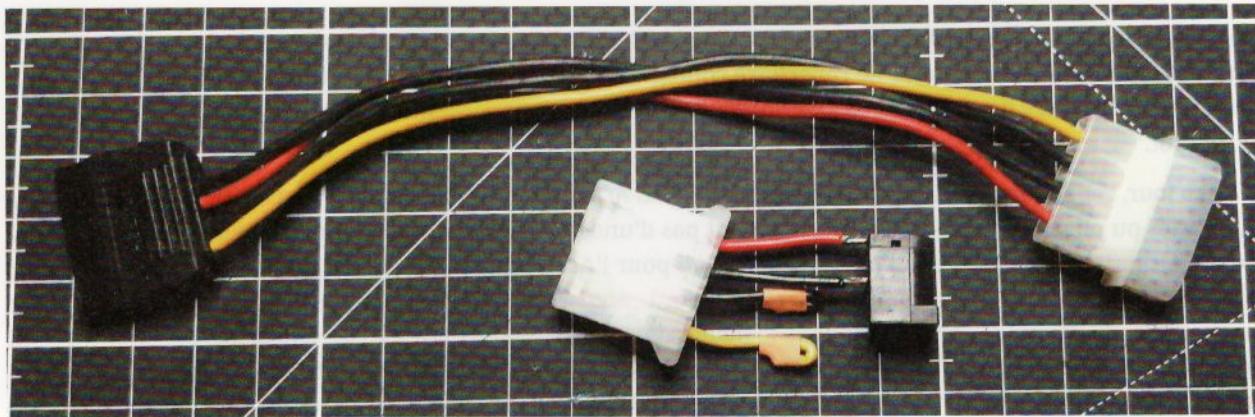

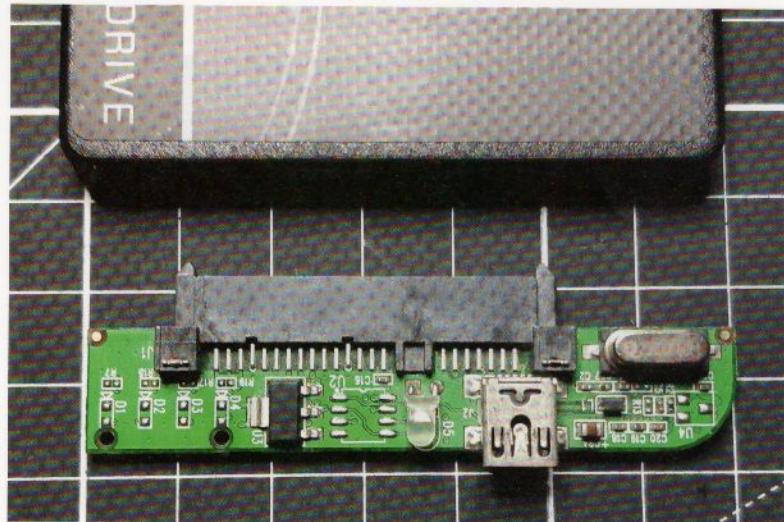

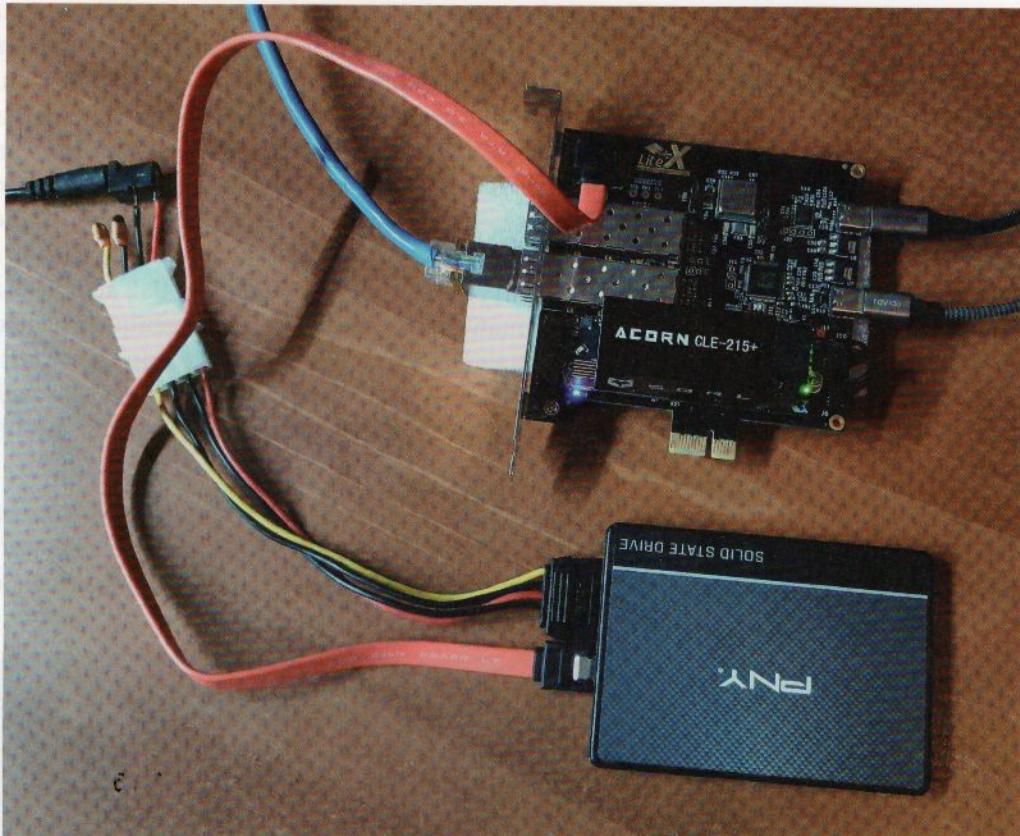

100 LiteX : Linux sur un SoC RISC-V en FPGA

### ABONNEMENT

89 Abonnement

RETROUVEZ CE NUMÉRO ET BIEN PLUS ENCORE SUR CONNECT

- » articles gratuits

- » contenu premium

- » listes de lecture...

CONNECT.ED-DIAMOND.COM

### À PROPOS DE HACKABLE...

#### HACKS, HACKERS & HACKABLE

Ce magazine ne traite pas de piratage. Un **hack** est une solution rapide et bricolée pour régler un problème, tantôt élégante, tantôt brouillonne, mais systématiquement créative. Les personnes utilisant ce type de techniques sont appelées **hackers**, quel que soit le domaine technologique. C'est un abus de langage médiatisé que de confondre « pirate informatique » et « hacker ». Le nom de ce magazine a été choisi pour refléter cette notion de **bidouillage créatif** sur la base d'un terme utilisé dans sa définition légitime, véritable et historique.

# FSIC2024 : L'OPEN SILICON DÉCOLLE À PARIS !

**Yann Guidon**

[whygee@f-cpu.org]

Du 19 au 21 juin a eu lieu la FSiC2024 [1], ou « Free Silicon Conference » sur le campus de Jussieu à Paris : trois intenses journées organisées par le projet « Go IT ! » (financé par l'Union européenne [2]) et hébergées par le département LIP6 de la Sorbonne/Paris 6. On y a croisé des académiques, bien sûr, mais aussi des bricoleurs de différents niveaux et d'horizons variés, des industriels et même des institutionnels ! Voici un petit résumé de ce que vous avez manqué et pourquoi vous auriez dû venir.

**Q**uelle époque incroyable nous vivons ! Il y a quatre ans, je vous expliquais [3] l'importance de l'accord historique entre Google, eFabless et Skywater. Le (pro)moteur principal de cette initiative, Tim « mithro » Ansell, n'est plus aussi impliqué, mais la masse critique a été indéniablement atteinte : le premier PDK (*Process Design Kit* [4]) a été libéré et le flambeau a été repris par les autres acteurs. Résultat : aujourd'hui, nous assistons à une multiplication des utilisateurs et deux autres PDK [5] sont maintenant librement disponibles à tous !

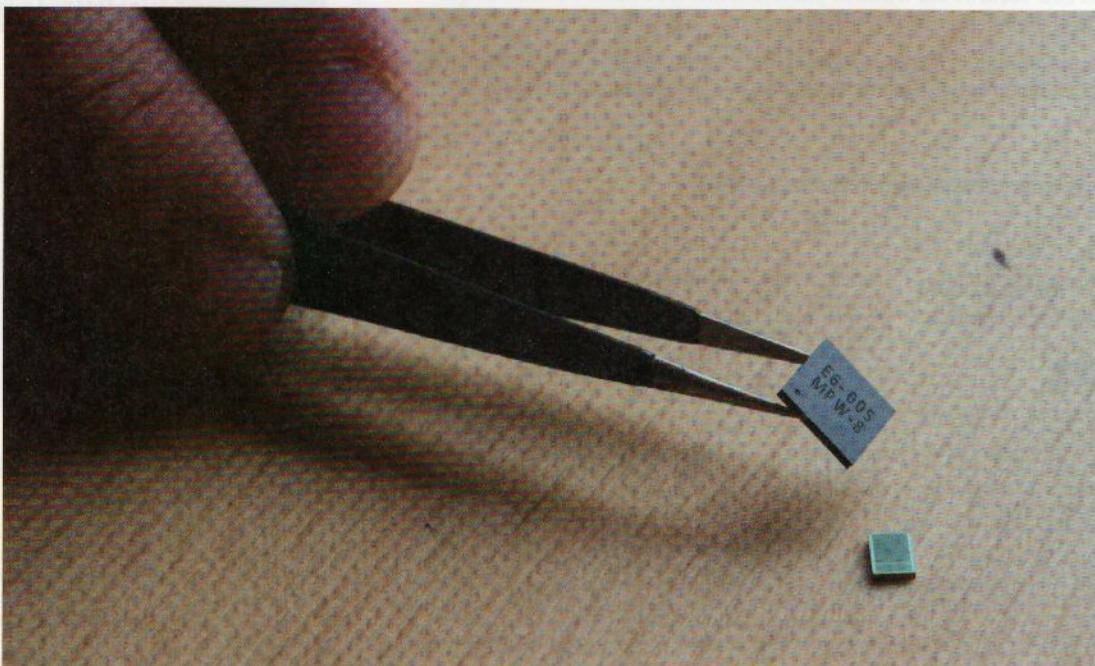

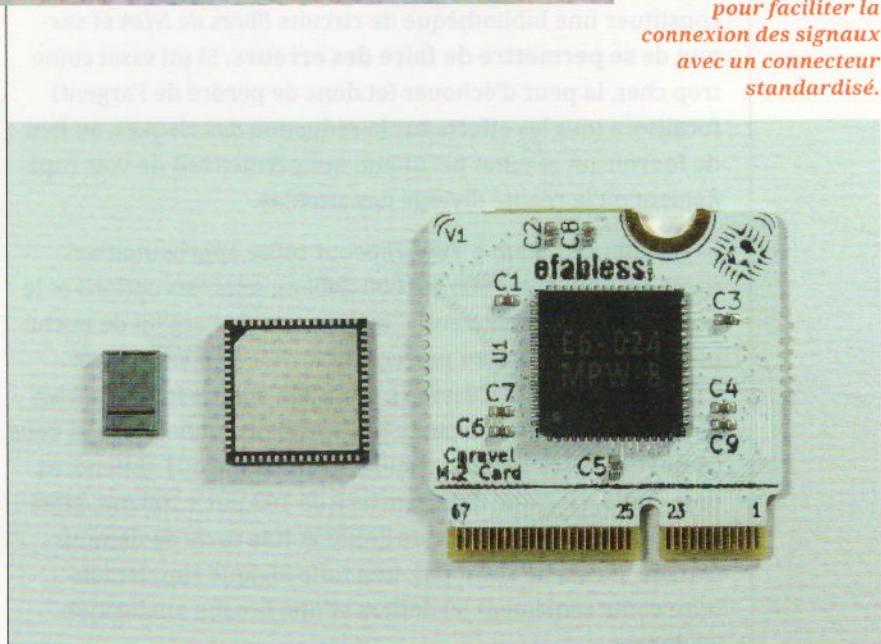

Les débutants peuvent aujourd'hui facilement créer un tout petit circuit, comme celui de la figure 1, intégré par le projet Tiny Tapeout [6]. Ce galop d'essai à quelques centaines de dollars se transforme parfois en une aventure à dix mille dollars pour occuper toute la surface de la puce, en utilisant librement les dix millimètres carrés (en passant directement par eFabless [7]). Mille dollars par millimètre carré peut sembler délirant (comparé au marché immobilier), mais ce forfait comprend typiquement une centaine d'exemplaires. Et c'est un bond considérable, d'autant plus que tout le *workflow* est intégré dans un serveur **git** public. Dire qu'en 2001, je me plaignais qu'il n'était pas possible de concevoir un circuit intégré avec des outils libres [8] alors qu'aujourd'hui, ils sont plébiscités par les gouvernements !

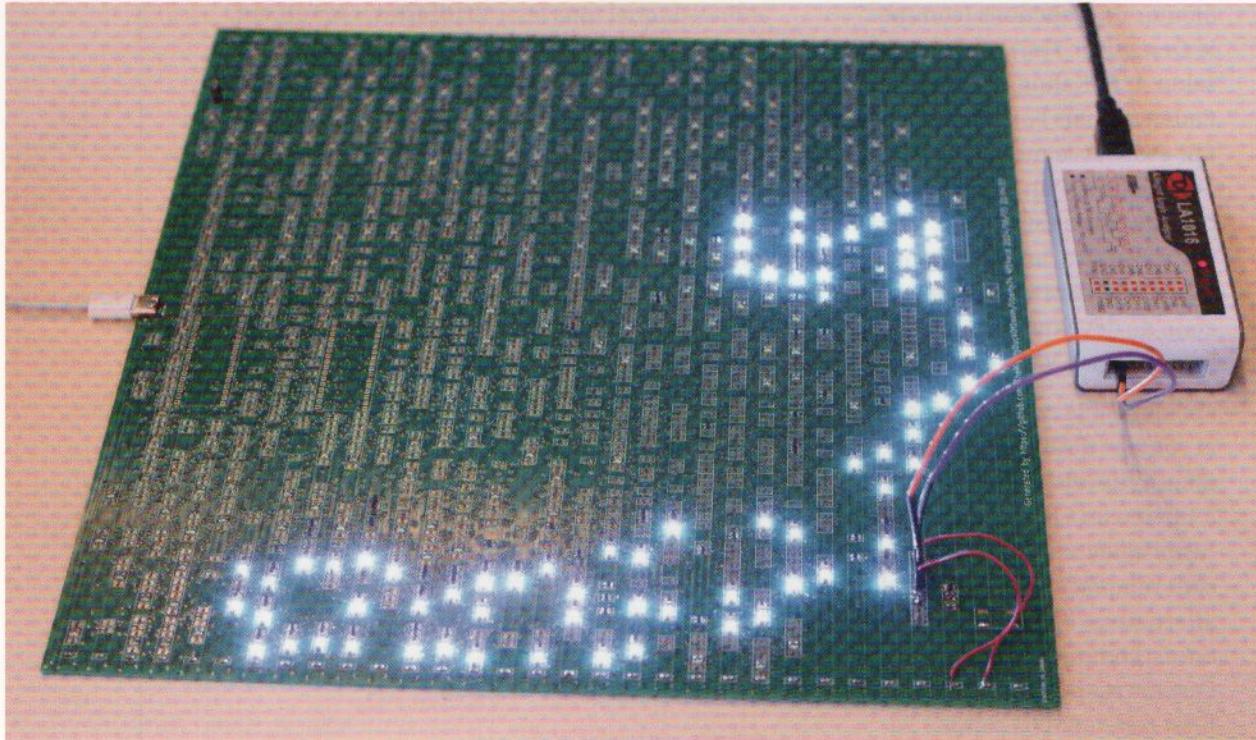

**Figure 1 : Vous aussi, vous pouvez faire votre propre puce ! Le projet Tiny Tapeout permet de concevoir des circuits électroniques de quelques centaines ou milliers de portes, puis de les faire réaliser sur un circuit intégré partagé avec une centaine d'autres projets (pour quelques centaines d'euros). Ici, l'un de ces projets est un « Simon » doté de sa carte d'extension spéciale (pour les LED, les boutons et le buzzer), présenté sur le livret qui détaille les dizaines de projets hébergés par la puce en question.**

### 1. LA NOUVELLE RÈGLE DU JEU

La pandémie et les guerres économiques ont électrisé tous les États du globe durant ces dernières années ; chaque pays y va de son programme de promotion des circuits intégrés locaux, de la conception à la fabrication, dans une optique de « souveraineté » puisqu'ils ont été reconnus comme essentiels à notre société moderne :

- La Chine (lire : le Parti communiste chinois) avait déjà plus ou moins son « plan » pour rattraper son retard sur les toutes dernières technologies, subventionnant les usines à tour de bras. Les lois étaient déjà conçues pour s'approprier les technologies étrangères en obligeant des « transferts de compétences » pour toute entreprise non chinoise désirant s'établir sur le territoire. Cela existait déjà au Japon, mais demandez à ARM comment ils se sont fait voler leurs brevets [9]. Cependant, l'injection de budgets faramineux (financés à l'échelle nationale et régionale) n'a pas eu tous les effets escomptés, car cela a surtout attiré les monteurs de projets financiers (aux motivations et méthodes douteuses, en pleine bulle spéculative), au lieu d'industriels compétents. Les pressions politiques et la corruption poussent de nombreuses usines à la faillite alors qu'elles sortent à peine de terre [10].

### « LE JUSTE PRIX »

Combien coûte une puce ? Une production en très grand volume a un coût, donc logiquement un prix, *relativement raisonnable* et dégressif. Ce qui a changé depuis l'an 2000, c'est l'investissement exponentiel pour son développement, atteignant des sommes délirantes, ce qui a plusieurs conséquences :

- de moins en moins de sociétés ont le budget requis pour développer une puce de toute dernière génération ;

- le prix de ces puces explose et oblige à en produire considérablement plus pour compenser cette augmentation, ce qui les limite à des produits de très grande consommation ;

- les lignes de fabrication coûtent des dizaines de milliards de dollars et ont une capacité limitée, conduisant à une sorte d'enchère secrète pour réserver la capacité de production pour un client, parfois même pour bloquer un concurrent ;

- il en résulte un appauvrissement de la diversité de l'offre et une réduction du nombre des plateformes majeures ;

- et une stagnation sur les technologies « déjà suffisantes » pour les applications peu sensibles ou matures.

Mais de combien parle-t-on ? Les coûts sont difficiles à chiffrer, car cela dépend de la complexité donc du temps de développement, du nombre d'ingénieurs assignés au projet, du support informatique (acheter et maintenir les serveurs surpuissants et leurs logiciels tout aussi chers) et bien sûr, du nombre d'erreurs donc du nombre de masques à refaire, qui coûtent chacun une fortune, selon la finesse de gravure.

Puisqu'il n'y a pas d'absolu, parlons en termes relatifs. Une estimation récente a été partagée par Sandra Rivera, la responsable FPGA chez Intel (suite au rachat d'Altera pour 16,7 milliards de dollars en 2015). Selon elle, les FPGA ont un bel avenir, car les fonderies comme TSMC deviennent inabordables.

## conférence/ EDA

- FSIC2024 : L'Open Silicium décolle à Paris ! -

L'explosion de la bulle immobilière (avec la chute d'Evergrande) et les réactions à la pandémie ont semé le doute dans l'industrie. En plus, les USA ont été échaudés par l'espionnage industriel éhonté et ont décidé d'un embargo sur toutes les technologies de pointe. ASML, NVIDIA et TSMC sont parmi les plus touchés par l'interdiction de vendre leurs joyaux. La guerre était déclarée et l'orgueil chinois piqué au vif : ils veulent « leurs puces » !

- Le gouvernement américain prend conscience de sa fragilité, suite à la crise industrielle provoquée par la COVID, les retards causés par l'administration Trump, et surtout les tensions politiques en mer de Chine qui font craindre de ne plus disposer des précieuses puces dernier cri fabriquées en majorité par TSMC à Taïwan (sans oublier le Japon et la Corée du Sud juste à côté). Le « *CHIPS and Science Act* » est voté en 2022 [11] et alloue 39 milliards de dollars pour inciter les industriels à installer des usines de dernière génération sur le territoire des USA. Des subventions énormes sont accordées entre autres à Intel (qui se met à ouvrir ses usines à des « partenaires » pour concurrencer TSMC, comme Samsung l'avait fait plus tôt, dans l'espoir de mieux rentabiliser ses usines) et TSMC (menacé par lesdites prétentions territoriales chinoises).

Les clients FPGA d'Intel partagent leurs difficultés, et Intel est déjà au courant des tarifs (qui sont jalousement gardés par des NDA), puisqu'il est lui aussi client. Une fourchette de budget a fini par percer dans un article de Timothy Prickett Morgan :

The thing that is in the favor of FPGAs and the[sic] mitigates against the massive migration to ASICs is the increasing cost of developing for each process node, and she rattled them off using Taiwan Semiconductor Manufacturing Co as the example, which was fun:

- \$40 million for a 28 nanometer device,

- \$100 million for a 14 nanometer device,

- \$300 million to \$400 million for an N7 device,

- \$600 million for an N3 device, and

- \$800 million for an N2 device.

Évidemment, ces nombres sont à considérer avec prudence, car Intel veut concurrencer TSMC en se séparant de ses propres fonderies.

On peut quand même estimer que pour le prix d'une puce de toute dernière génération, on peut s'en acheter deux en technologie plus ancienne, ou même s'offrir une usine âgée de trente ans. Et il s'agit du développement uniquement, car chaque puce produite ajoute ses propres coûts unitaires, pour le silicium, la gravure, l'encapsulation et tous les tests ! C'est donc logique que TinyTapeout et d'autres restent sur des technologies anciennes, bien plus économiques et « suffisamment bonnes ». Il y a déjà tellement à faire à 130 nanomètres !

Source : Timothy Prickett Morgan, « *Altera Is Being Realistic About FPGA Compute In The Datacenter* » <https://www.nextplatform.com/2024/09/26/altera-is-being-realistic-about-fpga-compute-in-the-datacenter/> 26 septembre 2024.

- L'Union européenne emboîte le pas et crée son propre programme similaire : l'*« European Chips Act »* adopté en 2023 [12]. Les programmes existants passent à la vitesse supérieure et Intel est courtisé pour installer une de ses dernières usines sur notre continent. C'est Magdebourg qui est choisi, entre autres grâce à dix milliards d'euros d'aide du gouvernement allemand. Intel prévoit aussi de s'étendre en Pologne et en Irlande, mais ses finances ne suivent pas et TSMC est sur ses talons : ESMC s'installe à Dresde [13] grâce à un partenariat avec Bosch, Infineon et NXP (qui financent à hauteur de 10 % chacun). Pour aider à former des concepteurs microélectroniques européens, l'Union européenne a aussi lancé *Edu4chip* [14] : c'est un programme qui associe des instituts et des sociétés de France (Mines-Telecom Saint-Étienne en fait partie), Allemagne, Danemark, Suède, Finlande, Bulgarie (et j'ai entendu Roumanie et Norvège, sans trouver de confirmation).

- Au Japon se crée l'*« Open Source Utilized Silicon Initiatives »* (Open-SUSI) [15].

- La Suisse aussi se réveille et lance son « *SwissChips* » en février 2024 [16].

- Le Royaume-Uni tente de se réorganiser après le Brexit, cherchant à reconstituer un rôle de prestige, mais n'en a pas les moyens. De plus, le Brexit a coupé l'île de précieux liens avec l'Europe, l'allié étasunien pose un risque de souveraineté (suite à l'embargo imposé à ASML en Chine) et les Chinois investissent massivement dans l'ombre [17]. Heureusement qu'il leur reste ARM, aujourd'hui coté en bourse.

- Les pays du Golfe veulent être de la partie pour diversifier leurs investissements de pétrodollars : l'Arabie Saoudite lance son « *National Semiconductor Hub* » [18] dans l'espoir d'attirer une cinquantaine de sociétés de conception, ainsi que des « talents », en mettant sur la table un quart de milliard de dollars de fonds d'investissement. Ce sujet fait aussi l'objet d'un récapitulatif par Asianometry [19].

- La Russie continue de prétendre qu'*elle aussi y arrivera bientôt, promis*. D'ici 2030, la « Mère Patrie » pourra graver toute seule comme une grande en 28 nm [20], puisque TSMC applique les sanctions internationales. Pour l'instant, ce sont les gentils voisins chinois qui assurent l'intérim, mais la gravure n'est rien sans une technologie d'encapsulation appropriée [21]. Pendant ce temps, le marché noir reprend « comme au bon vieux temps » et il se dit que des composants de chars sont obtenus en désossant des équipements électroménagers.

- Neuf pays d'Amérique du Sud resserrent leurs liens au sein de « *Latin Practice* » [22].

- Sans oublier la *Chip Alliance* gérée depuis 2019 par la Linux Foundation [23].

- Ce sont les initiatives les plus médiatisées, mais comme Andrew Kahng le remarque dans sa présentation [24], « *il n'y a pas d'open source chinois/américain/européen* ». Par contre, il y a des différences de soutien selon les régions. Et on peut presque parler d'une nouvelle révolution industrielle, car les règles ont changé brusquement, toutes les cartes ont été redistribuées, l'intégration verticale comme la consolidation industrielle et financière sont contournées (pour l'instant) grâce à l'*open source*. Tout le monde est sur le pont, car chacun a de nouveau sa chance et veut sa part, comme dans un nouveau Far West.

- Simultanément, depuis la révolution ChatGPT, tous les investissements ont basculé de la crypto/*blockchain* à l'*« intelligence artificielle »* (quoi que

cela signifie) qui a l'heureuse propriété de recycler beaucoup de technologies et d'infrastructures mises en place par les cryptomineurs. Les actions NVIDIA se sont encore plus envolées (atteignant une capitalisation comparable à Apple) grâce à des prévisions radieuses sur l'explosion de la puissance de calcul nécessaire pour « soutenir l'IA » : McKinsey prévoit au moins une multiplication par 100 d'ici cinq ans. Avec de telles perspectives, l'Union européenne songe à détourner son financement des projets *open source* [25].

Toutes les megaconstructions mentionnées plus haut font courir le risque d'une nouvelle crise de surproduction d'ici quelques années, que ni Apple ni Nvidia ne pourront probablement absorber. L'espoir est que le marché devienne plus compétitif, mais toutes les entreprises seront-elles rentables ? Le prochain cycle industriel pourrait se terminer bientôt, puisque les voix s'élèvent depuis juillet 2024 pour prévenir les investisseurs sur l'exagération des promesses de l'IA : quand la bulle éclatera-t-elle ?

À l'heure où j'écris ces lignes, Intel vient justement d'annoncer une « mesure de réduction des coûts » qui licenciera un employé sur

sept d'ici novembre [26]. Mécaniquement, son action a baissé d'un tiers en quelques heures, retournant à sa valeur de 2013. La direction est en crise<sup>\*0</sup>. Même si la cause officielle est d'avoir « raté le coche de l'IA », d'autres événements simultanés (comme Apple trahi par B-H, Google coupable de monopole ou les soucis au Japon) ont poussé les places boursières de trois continents à chuter significativement, comme en écho à 2001. Pas de krach boursier pour l'instant, Intel n'a pas coulé, mais cela compromet ses plans d'expansion et sa capacité à recevoir des subventions. Parallèlement, on s'inquiète sur la surévaluation de NVIDIA, société *fabless* donc qui n'a même pas ses propres usines, contrairement à Intel.

Toujours du côté de la rentabilité, les usines établies proposent plus longtemps des technologies « mûres », moins performantes mais beaucoup moins chères, à plus de clients grâce à la libération de leur PDK : c'est le pari de GlobalFoundries, qui a suivi l'exemple de SkyWater.

- En regardant plus attentivement, même si TSMC est actuellement à la pointe sur les toutes dernières technologies de gravure (au point de laisser Intel dans son sillage), une partie significative de son chiffre d'affaires est toujours réalisée avec des géométries plus anciennes comme 45 nm ou 28 nm, déjà rentabilisées et encore appropriées pour beaucoup d'applications modernes. Cela permet de financer ses indispensables recherches (un budget de 5,5 milliards de dollars en 2023), mais même TSMC ne peut pas se permettre de construire de nouveaux bâtiments pour chaque nouvelle génération : ses clients sont poussés à migrer vers des technologies plus récentes en prévision de l'arrêt des plus vieilles lignes de fabrication (moins rentables à cause de la concurrence plus forte). Grâce à sa domination, TSMC n'a aucun intérêt direct à jouer le jeu de l'*open source*.

- Par contre, de nombreux fondeurs plus modestes ne peuvent plus suivre le rythme ahurissant des investissements : ils font donc durer leurs équipements existants au maximum. L'ouverture de leur PDK devient nécessaire pour se démarquer et attirer de nouveaux clients, surtout si les autres fondeurs font de même. C'est pour cela que l'audace de SkyWater a été déterminante : le premier à libérer son PDK a une avance commerciale de quelques années sur les autres, et redore son blason. Ce fut flagrant durant la conférence !

\*0 Juste avant d'imprimer ce magazine, le président d'Intel Pat Gelsinger vient d'annoncer son « départ à la retraite » alors qu'une partie des subventions allouées à Intel par le CHIPS Act est remise en cause parce que les projets de nouvelles usines sont repoussés.

Sachant qu'une nouvelle usine de pointe coûte aujourd'hui environ *vingt milliards de dollars* avant même de livrer ses premières gaufres, il faut beaucoup de clients pour garder les lignes complètement occupées. De plus, les généreuses subventions des États hébergeurs doivent s'accompagner d'économies pour eux, en particulier sur les licences des logiciels. Heureusement que les universités et les amateurs en développaient depuis des décennies, sans le coût prohibitif des systèmes propriétaires : Cadence et Synopsys facturent très cher, en plus des budgets pour les formations et surtout les plateformes logicielles et matérielles. Bien que leurs résultats soient (pour l'instant) moins optimisés, les logiciels *open source* sont bien plus faciles à bricoler, l'industrie pense souvent « on verra plus tard pour contribuer des améliorations en retour ».

De plus, une expansion industrielle si brusque crée des tensions sur le marché du travail : les entreprises peinent à recruter<sup>\*1</sup> ! C'est particulièrement problématique dans un monde tellement sous l'emprise du secret industriel (les *Non-Disclosure Agreements* sont la règle) qu'un employé ne peut pas vraiment parler de son travail sur son CV, par exemple. Les ouïfils à la mode peuvent changer d'un coup et il faut alors former des dizaines de milliers de nouveaux techniciens, sur des technologies qui changent tous les cinq ans environ. Les programmes comme Edu4chip ne suffiront pas. La continuité inhérente des projets *open source* réduit la dépréciation des compétences et permet d'envisager des projets à plus long terme, sans crainte que les outils nous trahissent ou nous prennent en otage.

Mais les logiciels d'EDA ne sont rien sans les PDK. L'industrie microélectronique est tellement prisonnière des NDA qu'il est aujourd'hui impossible de comparer quoi que ce soit, ou de reproduire des résultats, publiés tronqués dans les journaux académiques. Comme dans plusieurs domaines scientifiques, on craint une « crise de reproductibilité » qui rendrait toute recherche caduque ou vaine. Un exemple typique nous en a été offert par l'ETH de Zurich lors de la période de questions-réponses, après avoir présenté un de leurs super-projets :

*Public : Quel outil commercial utilisez-vous ?

ETH : je ne crois pas que je peux le dire.*

Les projets libres n'ont pas tous ces inconvénients et ont même d'autres avantages, ce qui les rend enfin légitimes auprès des « décideurs ». Il n'est plus mal vu d'être un hacker !

## 2. PETITE CONFÉRENCE, GRANDS ENJEUX

C'est dans cette conjoncture que s'ouvre FSiC 2024, le 19 juin 2024. Le calendrier de bouclage de Diamond n'a pas permis de publier cet article plus tôt, mais le délai a permis de prendre un peu de recul et de relativiser l'optimisme.

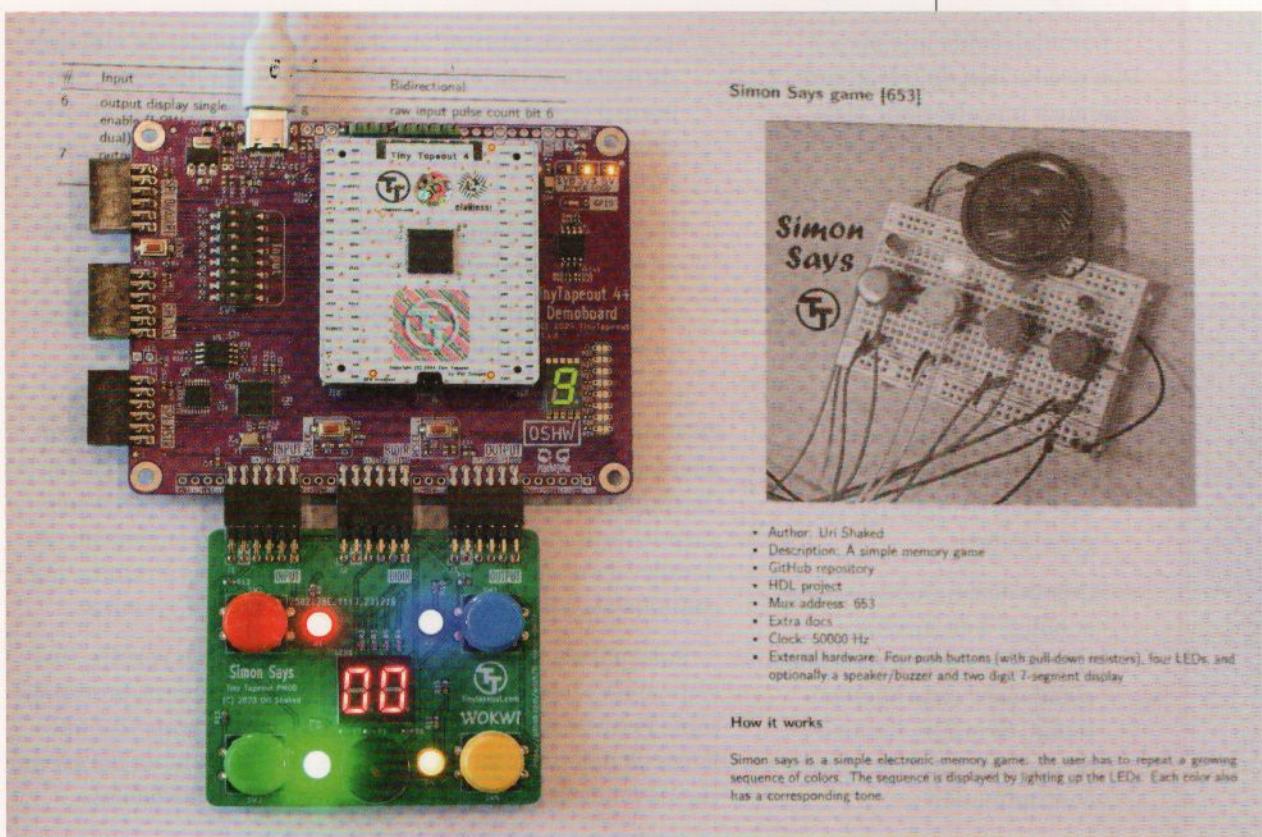

L'amphithéâtre 43 a accueilli environ 120 personnes (dont la photo de groupe est sur la figure 2), françaises bien sûr, mais aussi venues des USA, Inde, Allemagne, Pays-Bas, Grèce, Égypte, Finlande, Belgique, Chili, et probablement d'autres. Étrangement, le Royaume-Uni ne semble pas représenté, probablement à cause des conséquences du Brexit.

L'inscription est gratuite par e-mail, sans autre formalité : c'est une rencontre très pointue, mais sans barrière d'accès. Les débutants

\*1 Alors même qu'Intel et d'autres « dégraissent ».

## conférence/ EDA

- FSiC2024 : L'Open Silicium décolle à Paris ! -

Figure 2 : La plupart des 120 participants à la conférence ont posé pour une photo de groupe, lors de la pause méridienne du premier jour. Merci à eux et à tous les autres !

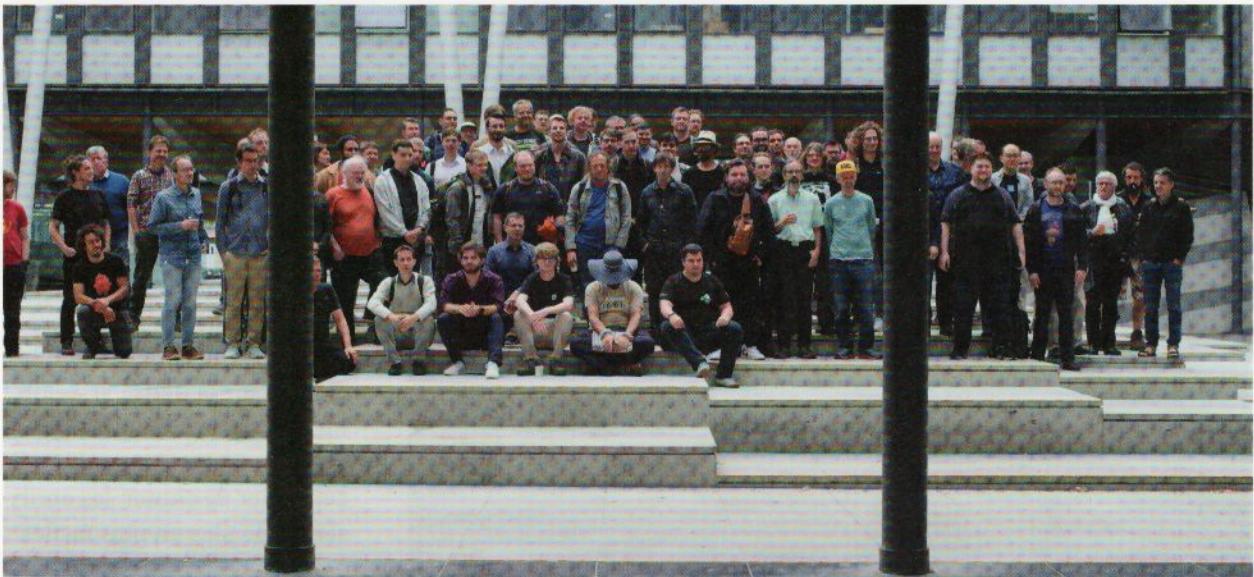

et les vétérans échangent librement, comme le montre la figure 3. Il manque seulement Tim Ansell pour que la galerie soit complète.

On note aussi qu'aucun « acteur majeur » de l'industrie n'est présent, donc pas d'Intel, d'AMD, de TSMC ou de Samsung, mais Skywater et Global Foundries sont souvent mentionnés puisque eFabless (présent) peut dorénavant les utiliser. Les nombreuses présentations s'enchaînent avec un rythme assez soutenu, une toutes les 20 à 30 minutes environ (au début). Forcément, des vignettes autocollantes circulent, dont certaines sont présentées sur la figure 4, page suivante.

On y parle beaucoup d'EDA, sigle de « *Electronic Design Automation* » qui signifie plus ou moins « automatisation de la conception électronique » et désigne le monde des outils de

Figure 3 : À gauche, Jérémy Alcim est un jeune ingénieur de talent, adepte de parallélisme, d'IA, de HDL et de C++, qui explore l'EDA Libre depuis un certain article dans Hackable [3]. Il rencontre le vétéran Tim Edwards (à droite) : il est (entre autres) le mainteneur actuel de l'outil historique MAGIC (<http://opencircuitdesign.com/>) ainsi que « Senior Vice President of Analog and Design » chez eFabless, où il a contribué à l'ouverture du PDK SkyWater et travaille sur le Caravel Panamax (voir la figure 12).

*Figure 4 : Pas de conférence sans autocollants ! C'est toujours mieux d'en avoir un peu d'avance, pour échanger plus tard.*

conception des circuits microélectroniques. Si l'EDA *open source* hérite directement de la philosophie du monde des logiciels libres, nous avons déjà dit que l'EDA commerciale interdit le partage des fichiers (scripts, paramètres, sources ou objets) et même le *benchmarking* ! Et jusqu'à très récemment, tous les PDK étaient strictement secrets, ce qui empêchait de reproduire ou de comparer des résultats publiés dans les journaux académiques. L'ouverture du PDK SkyWater a donc eu un impact profond sur l'industrie et certaines présentations nous en montrent les effets tangibles.

Pour comprendre l'intérêt de cette rencontre internationale, rien ne vaut la toute première présentation [27] : Matt Venn y résume l'état général des développements ouverts/libres et leurs enjeux. Je ne vais pas trop la paraphraser puisque la conférence a été filmée, n'hésitez pas à aller examiner sa présentation en ligne !

Matt a une perspective très optimiste de l'évolution récente et des perspectives pour « nous les bricoleurs », grâce à sa position stratégique puisqu'il organise le projet Tiny Tapeout (qu'il nous présente fièrement dans l'amphithéâtre sur la figure 5). Selon lui, les coûts de conception des circuits intégrés vont continuer de chuter, les outils seront de plus en plus faciles à obtenir et à installer, et les ateliers d'initiation se multiplieront : plus de 280 kits Tiny Tapeout ont déjà été livrés !

Je retiens en particulier qu'à la vingtième page de sa présentation, Matt évoque la « métrique **PPA** » qui est typiquement utilisée dans l'industrie pour caractériser et comparer des technologies, selon leur **Puissance**, leur **Performance** et l'**Aire** requises pour réaliser un circuit donné. À sa place, il propose une autre métrique qu'il appelle **RED** : **R**eproductibilité, **E**fficacité (du développement : installation aisée des outils et partage du code source) et **D**ocumentation (et en plus, cela peut devenir un acronyme, et non plus un sigle). Sous cet angle, les outils *open source* et la communauté sont loin devant l'industrie, puisque cette dernière s'est enfermée dans la culture du NDA. Tout change selon la perspective !

- FSIC2024 : L'Open Silicium décolle à Paris ! -

- Compte tenu du choix considérable offert par les fonderies aujourd'hui, allant du micromètre au nanomètre, la performance absolue d'un circuit ne compte plus autant qu'avant, car ce n'est alors qu'une question de budget. Mais sans reproductibilité, il est impossible d'itérer le développement d'un circuit pour l'améliorer.

- La gestion fluide des logiciels, non contraints par des serveurs de licences ou d'autres obligations contractuelles contre-productives, libère les développeurs qui peuvent se concentrer sur leur travail et moins lutter contre leurs propres outils (ou du moins, avoir plus de chances de gagner).

- Quant à la documentation, même si c'est souvent une considération « après coup » pour la plupart des développeurs, sa disponibilité pour tous sur Internet favorise encore plus la dissémination, la familiarité et l'évolution, alors qu'un produit propriétaire sous NDA est figé dans le temps.

### 3. RÉINVENTONS LA ROUE !

C'est un air connu pour les lecteurs assidus, mais le refrain a encore été chanté dans cette conférence.

Comme lors de toute « explosion cambrienne », l'augmentation de la variété des espèces (ou des projets) entraîne aussi de la redondance. C'est inhérent à l'*open source* et à la liberté de développer, car chacun peut fixer ou choisir ses propres besoins, au lieu de se plier à un outil qui impose son univers avec ses idiosyncrasies. Forcément, lorsque des équipes séparées ont besoin de la même

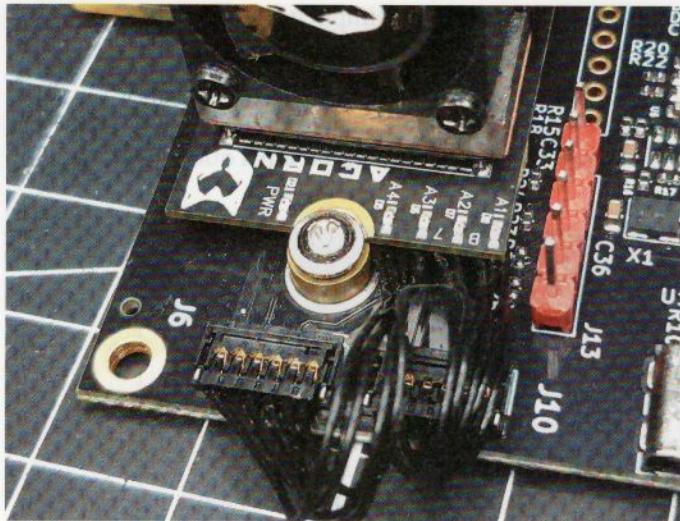

Figure 5 : Matt Venn est toujours prêt à faire une démonstration de la dernière fournée de TinyTapeout, avec son ordinateur, son analyseur logique, et les cartes d'adaptation, dont une dotée d'un support ZIF pour tester les puces sans les souder.

chose, elles développent des solutions similaires : c'est la *convergence*. Le travail est dupliqué, mais les différences peuvent grandir au point que les résultats deviennent incompatibles ou incomparables (comme Gnome ou KDE). À ce sujet, Andrew B. Kahng nous rappelle à la fin de sa présentation que ce phénomène n'est pas nouveau [24] :

*« The first SHARE Design Automation Workshop was held in 1964 (SHARE = Society to Help Avoid Redundant Effort). »*

Une bonne partie des duplications est due à l'ignorance : si l'on ignore que la roue existe, on finit par la réinventer. D'où l'importance de cette conférence : ignoriez-vous qu'elle avait eu lieu ? Pour vous rattraper, allez explorer le site web qui héberge toutes les présentations [1], vous pourriez y découvrir des outils que vous auriez été tenté de développer vous-même.

Une autre raison de dupliquer un outil est le « syndrome NIH » (*Not Invented Here*) : soit un utilisateur n'aime pas, soit il ne le comprend pas ou bien il n'accepte pas les choix d'un développeur. Dans la plus pure tradition des *hackers*, le code source est *forké* et modifié, ou même repris depuis zéro, souvent en utilisant le nouveau langage à la mode, saupoudré de concepts équivalents ou de néologismes. C'est ce qui s'est produit avec Migen et nMigen écrits en Python, mentionnés il y a quatre ans [3], sans parler d'Amaranth, magma, myhdl ou pymtl. Quant à Chisel et SpinalHDL, ils sont basés sur Scala. Cette année, la conférence a présenté Clash [28] qui compile et synthétise des portes logiques à partir de Haskell cette fois, et exporte en Verilog ou VHDL. Au rythme actuel, nous risquons de voir apparaître un HDL en Rust dans peu de temps, mais cela montre juste que la puissance de VHDL est ignorée ou incomprise.

Nous y voyons aussi d'autres influences du monde des logiciels libres : la tendance à abstraire et ajouter des complications « pour simplifier », alors que l'EDA traite des systèmes très tangibles qu'il faut pouvoir contrôler de A à Z, à tous les niveaux de description. Trop d'abstractions tuent l'abstraction, trop

de langages tuent les langages : j'ai déjà expliqué cela dans le chapitre 6 d'un article précédent [29].

Sinon, comme dans le cas du noyau Linux, un outil dupliqué a pu commencer comme un bricolage sur le coin d'une table « juste pour voir » puis a attiré des contributeurs et utilisateurs inattendus. Ce sont typiquement les projets les plus simples qui ont le plus de succès et de croissance... C'est moins probable dans le microcosme de l'EDA, mais nous voyons déjà des « masses critiques » se constituer.

Par exemple, alors que dans le monde des logiciels libres, nous avons vu les débats « Vim contre Emacs » ou « LLVM contre GCC », l'EDA libre balance entre OpenROAD et Coriolis.

- OpenROAD signifie « *Foundations and Realization of Open, Accessible Design* ». C'est la solution la plus adoptée et développée actuellement ; son historique est expliqué par son responsable dans une présentation passionnante [24]. Pour résumer, c'est issu d'un appel à projets DARPA en 2018 et après 17 millions de dollars de subventions, la fondation est créée depuis 2023. Le support commercial est fourni par <https://precisioninno.com> en partenariat avec Intel, Global Foundries, TSMC, SkyWater et Google. Côté logiciel, c'est une sorte de *patchwork* très flexible formé de nombreux outils existants (dont Yosys) ou expérimentaux ; d'ailleurs, certaines présentations décrivaient des modules supplémentaires pour

ajouter des fonctions (comme le *Design For Test*). Grâce à cela, selon A. B. Kahng, ce n'est plus Cadence, mais l'*open source* qui fait avancer le monde de l'EDA. Cela augure d'un « *brain drain* » comme cela s'est produit au début du millénaire, lorsque Linux a attiré progressivement beaucoup de développeurs contraints jusque-là par Windows.

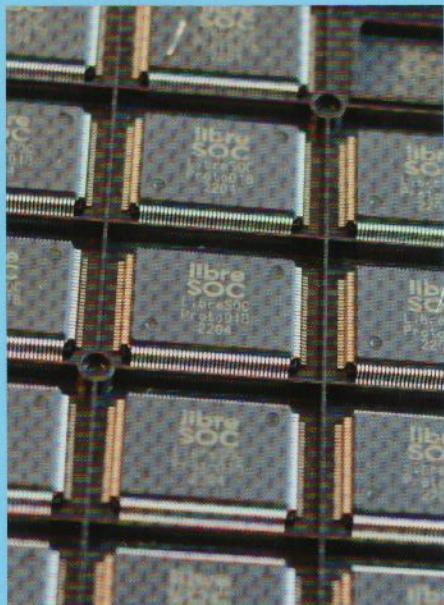

- Coriolis est le nouveau placeur et routeur d'Alliance, la suite d'outils développés depuis 1990 à Jussieu au LIP6. Certains outils historiques et idiosyncratiques sont remplacés par de nouvelles alternatives *conformes aux standards*, comme GHDL et Yosys. Coriolis est peu représenté, mais il est très capable, comme l'a montré la fabrication du prototype de Libre-SOC (voir à la partie 7) rendue possible grâce au soutien de NLnet entre 2019 et 2022 [30]. Coriolis n'est pas encore validé pour des géométries inférieures à 130 nm. Et comme l'équipe de développement et de maintenance est minimale, Coriolis ne peut pas supporter toutes les distributions GNU/Linux (un grief qui a fait l'objet d'une des présentations [55]).

Du côté des langages HDL (« de description de matériel »), c'est toujours Verilog qui est utilisé en général (« parce que c'est plus simple » et comme langage intermédiaire avant synthèse) mais VHDL résiste, en particulier grâce à GHDL

autour duquel tous les « VHDListes » se rallient, à la manière du ralliement autour de GCC il y a trente ans, délaissant les solutions commerciales plus rigides. GNU/Linux Magazine a publié un entretien avec son auteur, Tristan Gingold [31] il y a déjà 14 ans. Après une belle carrière chez AdaCore, il travaille depuis 2017 pour le CERN. Il nous a présenté [32] l'utilisation de GHDL dans un projet du CERN à base de Xilinx UltraScale. Le mélange de code *open source* avec des outils propriétaires cause encore et toujours des problèmes ubuesques. C'est là que les nombreuses qualités de GHDL brillent : la facilité d'intégration dans un *workflow*, la co-simulation, l'adhérence stricte aux standards, l'absence de toute limite arbitraire (comme le nombre d'instances exécutées simultanément) et VHDL est un « vrai langage »...

## 4. TRY, FAIL, ITERATE, AND BLINK !

La différence entre amateurs et professionnels est de plus en plus difficile à cerner, comme vous aurez pu le remarquer ces dernières années en lecteur assidu. Le critère essentiel est l'ampleur des moyens financiers disponibles, alors que les technologies sont plus abordables et accessibles, et les entreprises utilisent plus d'« outils amateurs ». Vous avez certainement remarqué la facilité déconcertante à réaliser des prototypes ou des petites séries de circuits imprimés, impensable il y a vingt ans. Non seulement les logiciels se sont démocratisés (entre autres grâce aux logiciels libres et aux versions gratuites de certains logiciels métiers), mais les industriels (surtout chinois) ont réduit encore plus la barrière d'entrée et les prix (vive le *dumping*) pour réaliser nos propres projets. Les PCB sont devenus une « commodité » et les composants basiques ont presque autant de valeur que des grains de sable !<sup>2</sup>

<sup>2</sup> Et même moins, puisque le temps de se baisser pour chercher une résistance au format 01005 (soit 0,4 mm×0,2 mm) tombée par terre coûte plus cher à l'employeur que le composant lui-même, ce qui lui vaut d'être qualifié de « poussière » dans le métier.

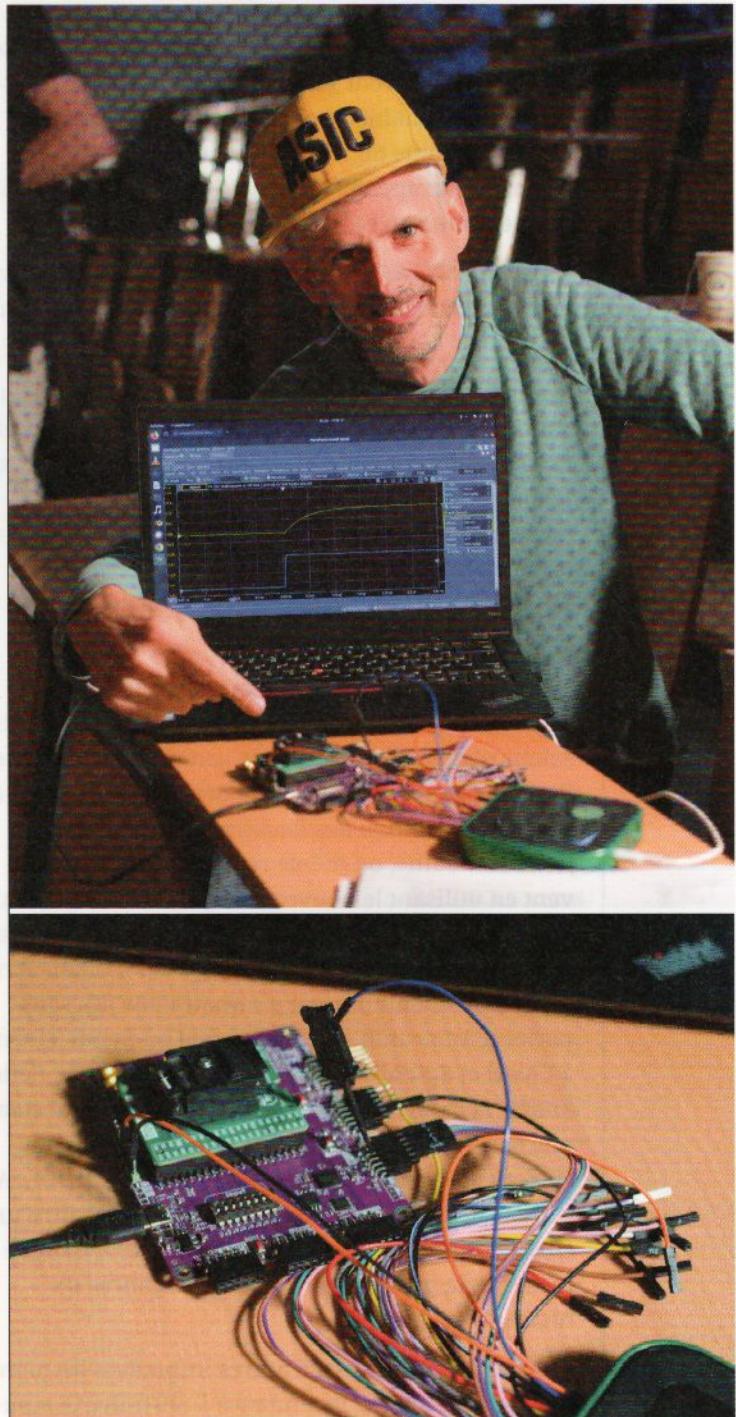

**Figure 6 : Le processeur de Tobias n'est pas intégré, mais à base de portes « discrètes », en boîtier en montage en surface. Le circuit imprimé est très large et pour économiser du budget, les portes sont soudées à la main, une à une, et chaque sortie est reliée à une LED pour vérifier son fonctionnement. Un analyseur logique injecte des données dans la chaîne de test pour automatiser la détection des fautes, c'est ce que nous voyons allumé sur cette image. D'autres diront que c'est une installation d'art abstrait, ne les écoutez pas.**

Cela a inspiré certains, dont Tim Böscke<sup>\*3</sup> en 2022, à détourner OpenROAD pour réaliser des circuits imprimés presque automatiquement à partir d'une description HDL [33]. Lorsque l'on peut générer son propre fichier Liberty (qui décrit les portes logiques proposées par une technologie particulière), rien n'oblige à ce que les portes soient destinées à un circuit intégré (qu'il soit bipolaire, CMOS, ECL ou autre). On a donc vu apparaître des prototypes de processeurs minimalistes « discrets », façon MOnSter6502 [34] mais générés automatiquement, comme des ASIC ! Ils sont réalisés à base de transistors (MOSFET ou bipolaires), de résistances, de diodes, de LED (*LED-Transistor-Logic*, LTL [35]) et en poussant encore un peu, on peut même utiliser le NE555 comme porte logique [36] !

Pour couronner le tout, les fabricants de PCB (qui s'amalgament naturellement avec les distributeurs de composants) sont heureux de placer et souder à la machine des centaines ou milliers de composants CMS à votre place, pour un surcoût *presque marginal* ! C'est un terrain de jeux fabuleux, presque moins cher et tellement plus impressionnant que Tiny Tapeout. Le résultat, bien que peu performant, est palpable, facile à déverminer ou réparer, et décoratif : il ne demande qu'à être encadré et accroché à un mur.

\*3 Encore un autre Tim, mais celui-ci est connu sous le pseudonyme CPLDCPU.

## conférence/ EDA

- FSiC2024 : L'Open Silicium décolle à Paris ! -

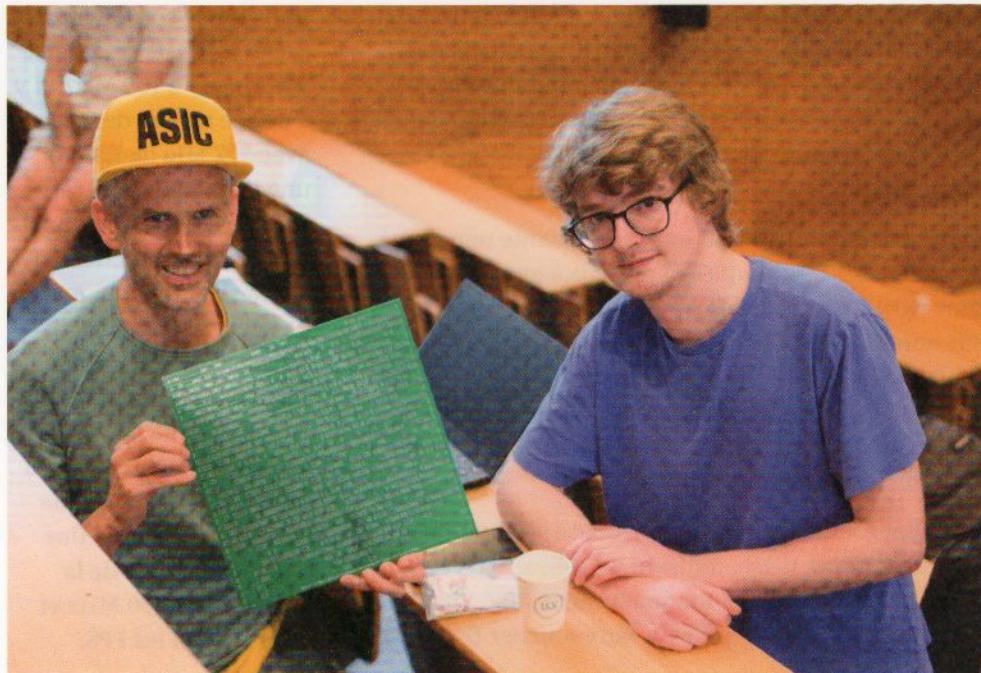

Figure 7 : Tobias Senti discute avec Matt Venn, à qui il offre un exemplaire du circuit imprimé de son « processeur désintégré ». Ensuite, à Matt de souder les milliers de composants, s'il veut que ça fonctionne !

Figure 8 : Thorsten Knoll crée des instruments de musique électronique. La filière d'EDA open source lui permet d'intégrer ses circuits dans des puces au lieu de rester tributaire des fabricants de FPGA. Ces derniers ne servent plus qu'au prototypage.

C'est ce que Tobias Senti, étudiant à l'ETH de Zurich, a voulu essayer par lui-même [37]. Il a compilé un microprocesseur en bricolant Yosys, Verilator, OpenROAD et KiCad. Au lieu d'utiliser des transistors, il a créé une bibliothèque de portes logiques (edit fichier Liberty) calquant cette fois-ci les fonctions des membres de la famille 74LVC1Gxx, qui sont des circuits intégrés en boîtier SOT23 ou SC70 contenant une seule porte logique. Le résultat est impressionnant (figures 6 et 7), même si le montage manuel n'était pas terminé. Tobias a aussi eu la bonne idée d'insérer une *scanchain* pour tester les circuits au fur et à mesure de l'assemblage.

Un autre bricoleur invétéré est venu d'Allemagne, bien qu'il n'ait pas fait de présentation. Parmi ses nombreux projets, Thorsten Knoll a développé un circuit de génération de musique dans un FPGA (figure 8, page précédente), qu'il va bientôt immortaliser dans un circuit intégré grâce aux nouvelles méthodes.

Encore une démonstration impressionnante nous a été offerte par Charles Papon [38]. Il a remis à jour le *softcore* VexRiscv (NDLR : voir article sur Linux et LiteX dans le présent numéro) en utilisant SpinalHDL : ce dernier est un *fork* (spirituel) de Chisel depuis fin 2014. Il est écrit en Scala, qui est un langage statiquement typé reposant sur la *Java Virtual Machine*, et génère du VHDL ou du Verilog (c'est ce dernier que Charles utilise).

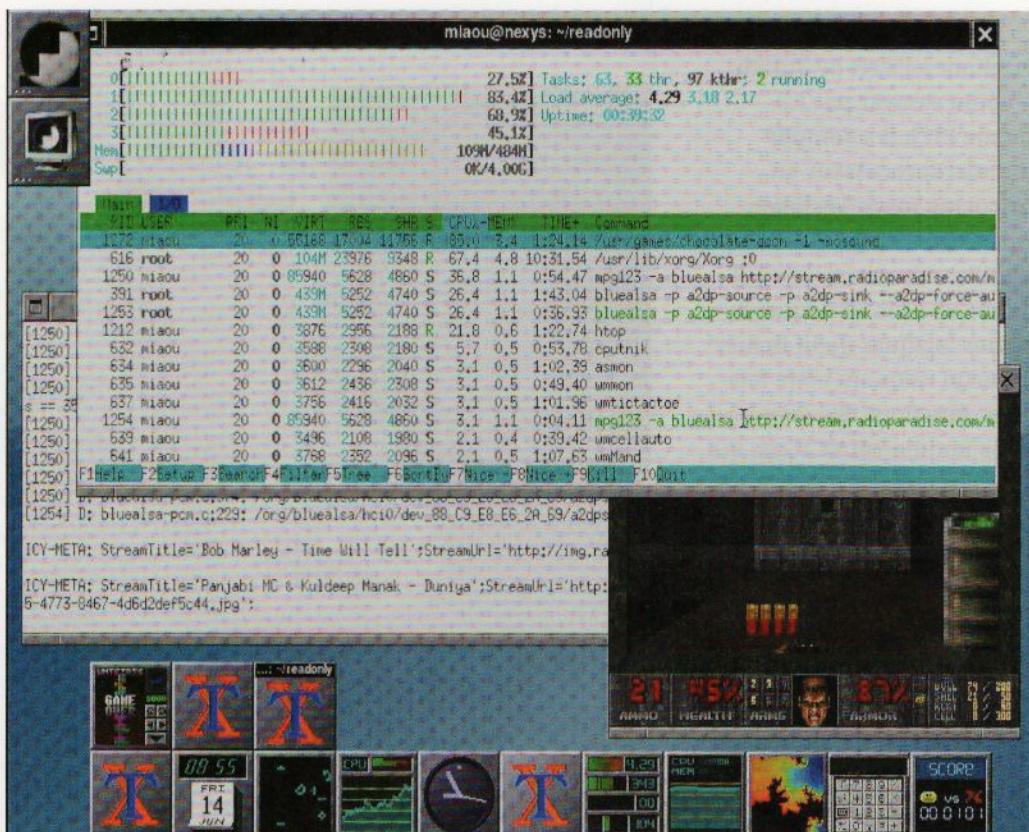

Le résultat est un système complet basé sur une carte FPGA *Diligent Nexys Video*, utilisant un Xilinx Artix7 (figure 9). Le processeur est un quadricœur RISC-V (configurable en superscalaire) qui peut faire tourner Debian à

une vitesse correcte malgré la modeste fréquence d'horloge de 100 MHz. Il y a peu de risques de *swapper* avec 512 Mio de RAM et une installation dégraissée. Le vidéoprojecteur est connecté (indirectement) sur la sortie graphique de la carte, démontrant qu'elle était totalement fonctionnelle en affichant les *slides* de la présentation. Nous avons aussi eu droit à une petite partie de DOOM à 25 fps ! Une version suivante de la carte atteint 200 MHz et double ainsi les FPS.

**Figure 9 : Capture d'écran (au travers d'un dongle HDMI-USB) du système Debian tournant sur un processeur quadricœur RISC-V 100 MHz implémenté dans un FPGA Artix7. Il est largement assez puissant pour afficher la présentation avec xpdf, ou jouer à DOOM sans latence. Presque tout est libre, on n'attend plus que le FPGA ! Source : Charles Papon, domaine public.**

– FSiC2024 : L'Open Silicium décolle à Paris ! –

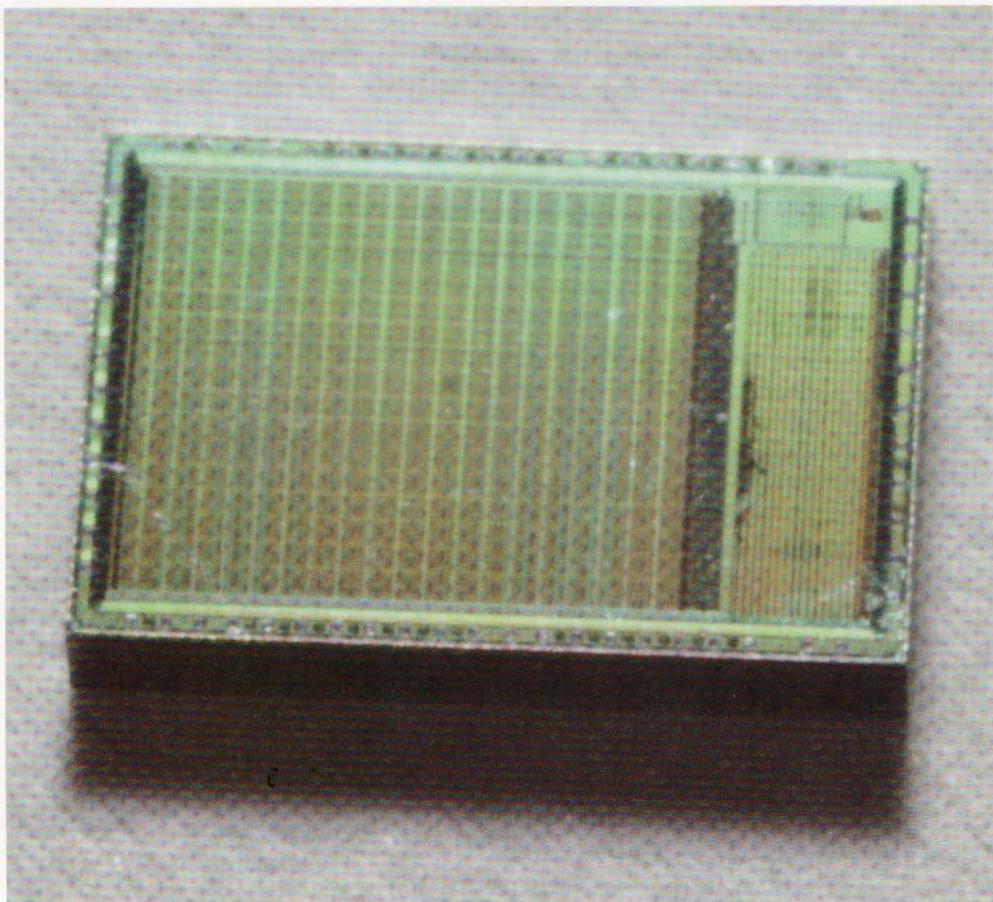

Figure 10 :

Macrophotographie

d'une puce

TinyTapeout nue,

où l'on devine le fin

maillage sous lequel

plus d'une centaine

de projets occupent

chacun quelques

milliers de portes

logiques.

Figure 11 : Après

fabrication, la puce

TinyTapeout (à

gauche) est encapsulée

dans un boîtier

plastique QFN (au

milieu) à peine plus

gros que la puce elle-

même ! Ce boîtier est

ensuite soudé (à l'air

chaud) sur un petit

circuit imprimé (au

format M2, à droite)

pour faciliter la

connexion des signaux

avec un connecteur

standardisé.

## 5. TINY TAPEOUT DEVIENDRA GRAND

Vous avez compris qu'il y avait du Tiny Tapeout partout. Merci encore à Thorsten de m'avoir fourni un échantillon d'une puce nue (figure 10) et une version encapsulée (figure 11), afin que je puisse les photographier correctement à la maison !

Lors de la conférence, la quatrième fournée venait d'être livrée et la huitième

bouclera (*tape out* en anglais : « envoi des bandes magnétiques à l'usine ») le 6 septembre. Il faut environ six mois entre la clôture d'un *circuit multiprojets* et sa livraison, selon le calendrier à <https://tinytapeout.com/runs>.

Le cafouillage de la première édition est largement loin derrière : les logiciels ont été reconfigurés correctement pour fournir des puces qui fonctionnent, cette fois. Mais ce faux départ n'était pas un désastre, car même si la puce arrivait seulement à faire clignoter une LED, la fierté de posséder un circuit intégré qu'on a conçu soi-même compensait largement ! Cela augure de porte-clés en série limitée, et les éditions suivantes ont livré les circuits promis au départ.

Aujourd'hui, la machine est rodée, la file d'attente des projets est bien remplie et les utilisateurs expérimentent tous azimuts, encouragés par les limites techniques qui sont progressivement repoussées par les organisateurs. Par exemple, aujourd'hui, un utilisateur peut réclamer plusieurs blocs consécutifs au lieu d'un, en payant un surcoût proportionnel. Ils disposent ainsi de plus de place pour réaliser des fonctions plus complexes comme un microprocesseur, un accélérateur de Mandelbrot ou un bloc cryptologique.

Les technologies utilisées par Tiny Tapeout et eFabless ne sont pas les plus à la pointe, mais elles sont rendues très abordables, puisque l'objectif est de pouvoir expérimenter, de constituer une bibliothèque de circuits *libres de NDA* et surtout de **se permettre de faire des erreurs**. Si un essai coûte trop cher, la peur d'échouer (et donc de perdre de l'argent) focalisera tous les efforts sur la réduction des risques, au lieu de fournir un résultat pertinent, qui permettrait de voir rapidement où la réalité diverge des attentes.

Une participation à Tiny Tapeout coûte approximativement, en tout, entre 500 et 1000 dollars, selon les options et le nombre de puces désirées. C'est presque de l'argent de poche pour certains, grâce au partage du forfait à 10000 dollars « ChipIgnite » de eFabless [7]. Pour 300 dollars (plus les frais de port, mais avec une petite réduction promotionnelle si vous soumettez votre projet parmi les premiers), vous obtiendrez une « tuile » logique d'une surface de 160 µm × 100 µm, ainsi qu'un unique exemplaire de l'ASIC et une carte de démonstration. Si cela ne suffit pas, une tuile logique supplémentaire coûte seulement 50 dollars et une broche analogique 40 dollars.

Oui, car il est maintenant possible de concevoir et réaliser des circuits analogiques, ce qui ouvre de nouvelles perspectives ! Le concours Chipalooza 2024 [39] a permis de *crowdsourcer* une bibliothèque de modules analogiques indispensables même pour les circuits numériques, comme des oscillateurs, des PLL, des convertisseurs A/N et N/A, ou des détecteurs de perte d'alimentation. D'autres fonctions sont clonées ou explorées, comme le fameux timer 555, des amplificateurs opérationnels, des pédales de distorsion... Aussi bien Tiny Tapeout que eFabless bénéficient de ces développements, qui doivent être soumis sur un **git** public en licence libre.

Bientôt, grâce à cette réutilisation et à la modularité, des circuits analogiques et mixtes plus avancés seront aussi faciles à réaliser qu'avec des portes logiques booléennes. La septième fournée (TT07 pour les intimes) contient déjà, parmi une centaine d'autres projets, un RISC-V32I, un amplificateur pour sonde d'électrocardiographie et même des émulateurs de générateurs de sons analogiques vintage d'ordinateurs 8 bits (style AY-3-8913 des CPC, MSX, Atmos, Vectrex...). Les amoureux de *chiptunes*

## conférence/ EDA

- FSiC2024 : L'Open Silicium décolle à Paris ! -

**Efabless Caravel Panamax**

**ML-SoC pinout**

**OVT pads**

**User project area**

**Legend:**

- red: user/mgmt GPIO

- green: 2 SIO pads

- blue: 2 analog pads

- yellow: 8 1.8V supply pins

- orange: 9 3.3V supply pins

- grey: 8 mgmt GPIO

- grey: 16 GPIO are OVT

- grey: 4 XO pads

- grey: 6 analog 3.3V pins

- grey: 6 analog ground pins

- grey: 2 1.8V ground pins

- grey: 9 3.3V ground pins

FSiC 2024

June 19, 2024

et de *sasfepus* réfléchissent déjà à comment remplacer leurs puces d'origine qui vieillissent mal.

N'oublions pas la gestion de la puissance. Une équipe chilienne a montré l'utilisation du PDK SkyWater130 et de Caravel pour réaliser des régulateurs de tension DC/DC totalement intégrés sur une puce. Sur un exemple, la moitié de la surface (environ 5 mm<sup>2</sup>) est couverte par les condensateurs flottants d'une pompe de charges [40] : c'est la preuve du potentiel et de la flexibilité de la technologie de SkyWater. Le but est de fournir des blocs

configurables de gestion d'alimentation (PMIC) intégrables dans des puces plus grosses, pour faciliter la vie des concepteurs amateurs. Les circuits intégrés « ouverts » pourront donc optimiser leur performance et leur consommation.

Un autre domaine analogique est l'électronique radiofréquence, en particulier pour les communications (radio ou filaire), mais la bande passante des interfaces disponibles sur la puce actuelle ne le permet pas encore. La fournée TT07 (qui sera livrée début 2025) et les suivantes permettront probablement de repousser cette limite.

Après l'électronique de puissance et radiofréquence, il ne restera plus que les MEMS, mais il n'en a pas été question. Je crois que ce sera pour beaucoup plus tard, avec une autre fonderie !

**64 user/mgmt GPIO**

**8 mgmt GPIO**

**2 SIO pads**

**2 analog pads**

**16 GPIO are OVT**

**4 XO pads**

**8 1.8V supply pins**

**8 1.8V ground pins**

**9 3.3V supply pins**

**9 3.3V ground pins**

**6 analog 3.3V pins**

**6 analog ground pins**

**Figure 12 : La configuration « Caravel Panamax » de Efabless permettra d'utiliser au mieux la surface et les broches permises par la puce en technologie 130 nm de SkyWater. Par rapport aux 34 broches de la configuration actuelle, c'est un bond important pour le prototypage de circuits plus complexes et nécessitant beaucoup de bande passante ! D'autant plus que le boîtier TQFP128, bien que plus cher, est plus facile à souder à la main. Source : [41].**

En attendant, les limites actuelles créent un embouteillage sur la puce : TT03 contenait 249 projets différents (dont un seul actif à la fois), chacun disposant d'un port de 24 bits (8 entrées, 8 sorties et 8 bits bidirectionnels). Pour multiplexer autant de broches, un gigantesque registre à décalage a été mis au point, ce qui limite la bande passante numérique. La fréquence interne de 50 MHz est divisée par autant de projets, soit environ 500 kilohertz, donc contraignant les projets à des « bacs à sable » à basse fréquence comme le Simon de la figure 1 ou des décodeurs 7 segments. Le multiplexage numérique est en cours d'amélioration, car il étouffe littéralement les projets, et les 34 broches ne suffisent pas, ce qui conduit à une sous-utilisation de la surface disponible.

Heureusement, Tim Edwards de eFabless a annoncé avoir discuté avec SkyWater pour créer une nouvelle configuration surnommée « Caravel Panamax » [41]. Grâce à elle, un projet pourrait utiliser un bus numérique parallèle de 64 bits grâce à un boîtier TQFP 128 broches (figure 12), et les 10 mm<sup>2</sup> de la puce sont libérés au maximum (en plaçant certaines fonctions essentielles dans l'anneau des connexions externes). Cela permet d'envisager la conception de processeurs plus performants ou d'allouer plus de broches pour des projets Tiny Tapeout. Le prix hors Tiny Tapeout (si vous voulez disposer de tout pour vous tout seul) n'est pas encore annoncé, mais probablement supérieur aux 10000 dollars habituels, en raison du boîtier plus grand. Mais cela vaut la peine pour les projets qui ont besoin de beaucoup de bande passante, ou si vous préférez souder à la main !

## 6. L'AMBITION ALLEMANDE

Une autre présentation fascinante nous a été offerte par Staf Verhaegen [42]. Après des années à travailler pour IMEC (l'institut interuniversitaire de recherche microélectronique à Louvain en Belgique), il a fondé <https://chipflow.io>, qui est similaire à eFabless, mais s'occupe aussi de la sous-traitance de la conception des circuits. Pour cela, il a développé ses propres outils en licence libre en Python à partir d'Amaranth (basé sur nMigen, suite à des controverses de droit des marques [43]).

Les autres projets de Staf (dont <https://chips4makers.io/>) l'ont amené à collaborer avec les suspects habituels comme Matt Venn ([44] pour son cours « Zero to ASIC ») ou LIP6 (pour

le prototype de Libre-SOC avec Coriolis). Dans ce dernier cas, Staf s'est chargé de la gestion du PDK puisque ce dernier était sous NDA strict de TSMC : Coriolis peut travailler avec des « cellules symboliques » qui seront remplacées plus tard avec des cellules réelles par une personne habilitée sous NDA (Staf, en l'occurrence).

Pour gérer toutes ces cellules et bibliothèques, libres comme propriétaires, Staf a mis au point *PDK Master* [45] permettant d'harmoniser les différents PDK que les fonderies fournissent (ou que des universités développent, comme FreePDK), souvent en formats incompatibles entre eux. Il s'est logiquement retrouvé impliqué dans la « libération » de l'OpenPDK de l'iHP [46], fourni cette fois par le « *Leibniz Institute for High Performance Microelectronics* » près de Francfort (voir <https://www.ihp-microelectronics.com/>).

Ce troisième PDK libre permet dorénavant d'accéder à la technologie BiCMOS 130 nm (appelée **SG13G2**) développée à l'institut, pour les recherches (académiques ou non) et les prototypes. Sur la base d'une technologie CMOS 130 nm, des transistors HBT (*High Performance Heterojunction Bipolar*

- FSIC2024 : L'Open Silicium décolle à Paris ! -

Transistors ultrarapide à base de silicium-germanium) sont ajoutés, rendant possibles des circuits intégrés « mixtes » qui combinent de la logique booléenne dense et des traitements des signaux radiofréquences à plusieurs dizaines de gigahertz. Pour résumer, c'est ce qu'on trouve de mieux avant de faire appel à l'arsénure de gallium (AsGa) ou au phosphure d'indium (InP) qui ne sont toujours pas disponibles en fabrication de masse, en particulier parce que les circuits bipolaires ne peuvent pas rétrécir autant que les circuits MOS.

Cette technologie mixte pourrait accélérer certains traitements logiques avec les HBT, gourmands en énergie, et garder les portes CMOS pour les fonctions lentes ou basses consommations (comme les mémoires). Cela permet d'envisager des microprocesseurs plus rapides (Intel avait fait appel au BiCMOS pour le premier Pentium) ou des modems 5G/Wi-Fi/Bluetooth par exemple. On atteint un niveau de sophistication bien supérieur à celui de Tiny Tapeout !

Et puisque nous vivons à l'aube de l'ère de l'« IA », ou du moins des LLM, l'iHP a introduit un *chatbot* (basé

sur ChatGPT) dans son PDK pour faciliter la recherche dans la documentation. Ce type d'innovation (ou de bricolage) est un autre avantage de l'ouverture !

Bien que l'OpenPDK de l'iHP ne soit pas le plus complet ou avancé, il rend accessible une technologie de pointe, ce qui devrait bénéficier à tout le monde, et surtout inciter d'autres fonderies commerciales à libérer leurs propres PDK. Mais ce n'est pas le plus surprenant : en collaboration avec Europractice, les universités peuvent utiliser le process de l'iHP gratuitement, à condition de rendre leurs fichiers publics sous licence libre. La soumission des projets se fait déjà avec un [git](#) public, comme Tiny Tapeout/eFabless. L'*originalité* ici est que la « propriété intellectuelle » (IP) est reversée à l'iHP, qui **reste aussi propriétaire des puces** (puisque il les subventionne). Un système appelé « *OpenSamples StoreHouse* » a aussi mis en place, pour « prêter » les « échantillons gratuits » des puces fondues, puisqu'il faut bien vérifier qu'elles fonctionnent. C'est une nouvelle organisation étrange, concoctée par les institutionnels pour remplir un objectif évident de formation et de *crowdsourcing*, tout comme le Chipalooza d'eFabless ou même l'initiative originale de Google. Nous verrons dans les années à venir comment cela évolue et si elle fait des émules.

Dans le cas de l'iHP, les projets commerciaux sont majorés pour sponsoriser les développements libres. Donc plus l'iHP a de clients, moins chers seront les projets, mais pour qu'il y ait plus de clients, il leur faut plus de ressources gratuites pour concevoir leurs circuits. C'est une problématique courante d'*amorçage*. Déjà, il se dit que eFabless commence à collaborer avec l'iHP, laissant présager son implantation en Europe, ainsi que des projets « signaux mixtes » encore plus perfectionnés et utiles, peut-être au travers de Tiny Tapeout (donc sans passer par *OpenSamples*).

Il a été peu question des licences *open source* pour le code source du matériel, la licence CERN a été évoquée, mais ce n'est apparemment plus un débat comme il y a vingt ans, grâce à l'expérience acquise. On a surtout discuté de facilité d'utilisation, de coût, d'exploration, de NIH, de diversité... Et tout se fait par des logiciels (donc avec des licences existantes), ce qui court-circuite la question du « copyright » sur les fichiers générés ou sur la puce elle-même. Aucun brevet n'a été aperçu.

J'ai remarqué que les Allemands étaient venus déterminés, avec plusieurs présentations ainsi que des institutionnels dans le public, prenant des notes méticuleuses ; c'était probablement des membres du ministère de la Recherche allemand qui subventionne l'iHP, ce dernier distribuant des dépliants sur une table. Entre TSMC et Intel qui vont chacun ouvrir une mégusine sur leur sol, grâce à des subventions inégalées en Europe, j'imagine qu'ils veulent être sûrs d'avoir les moyens de leurs ambitions. Cela préfigure aussi l'événement évoqué en conclusion.

En parallèle du pragmatisme allemand, l'europeanisation des projets se poursuit, mais la préférence nationale persiste : par exemple, l'argent allemand finance uniquement les entités allemandes. Si on vit en dehors de l'Allemagne, il faut demander de l'aide à son pays de résidence ou à l'Union européenne. Ce qui pose l'autre question du financement des individus : « il est plus facile d'établir des contrats avec des sociétés », dit-on. Comment soutenir les communautés, alors ? Comment définir, officialiser et légitimer les communautés et leurs projets, sans les entraver par des obligations et de la paperasse ?

Puisqu'ils sont des auteurs importants des outils libres et *open source*, les développeurs indépendants, qui ne sont pas dans l'industrie ou le circuit académique, doivent aussi être soutenus. Ce qui est un problème majeur, pas seulement dans le cadre spécifique de la microélectronique : on entend ici et là les plaintes que les FOSS sont « libres à télécharger et utiliser, mais pas à développer » ! Et l'Union européenne est connue pour focaliser des millions d'euros d'aide sur des sociétés déjà implantées.

C'est là qu'intervient la Fondation NLnet qui « finance les 500 millions d'Européens » en redistribuant des fonds venus de différents programmes comme *Next Generation Internet* (<https://ngi.eu>). NLnet lance des appels à projets tous les deux mois et la présentation de Michiel Leenaars [47] est simple, claire et devrait vous donner toutes les informations pour soumettre votre projet. Mais faites vite, car l'Europe semble reconstruire ses priorités [25] en cédant aux sirènes de l'IA.

## 7. ADIEU, LIBRE-SOC

Pour terminer en beauté ces trois jours, j'ai profité des circonstances favorables pour rendre visite à ce qu'aujourd'hui je qualifierais d'« artefacts historiques ». Cette conférence étant hébergée à Jussieu, où le LIP6 a ses bureaux et salles de cours, l'occasion était trop belle.

Comme mentionné précédemment, le LIP6 développe la suite Alliance/Coriolis et a participé (entre autres) à la fabrication du prototype de Libre-SOC, annoncé il y a quatre ans [3]. En suivant les conversations sur la liste de diffusion [48] je savais que des puces avaient été fondues en CMOS 180 nm par TSMC en passant par l'IMEC [49] puis livrées au LIP6, mais leur fonctionnalité n'avait pas encore été testée au-delà de la chaîne JTAG et de la PLL.

Au moins, *les puces étaient là* et vingt-cinq ans après le début du projet F-CPU, il était important d'aller immortaliser ce qui était (d'une certaine façon) son aboutissement : le premier prototype d'un microprocesseur réellement innovant, conçu avec des logiciels libres et (presque) totalement exempt de NDA. J'ai pu approcher un responsable du département qui m'a gracieusement ouvert le local des archives, où s'est déroulée une petite séance photo improvisée (figures 13 et 14).

Il faut rappeler que le *tapeout* est arrivé à un moment, on va dire, peu propice, en pleine crise mondiale de production assortie d'une petite

## conférence/ EDA

– FSIC2024 : L'Open Silicium décole à Paris ! –

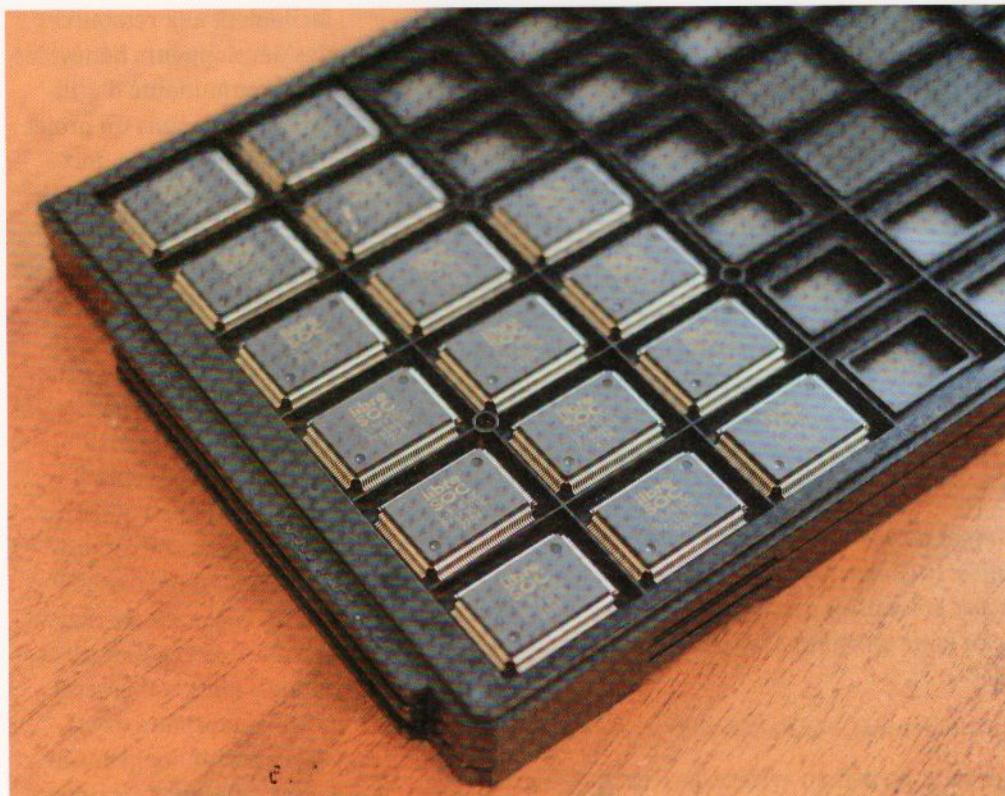

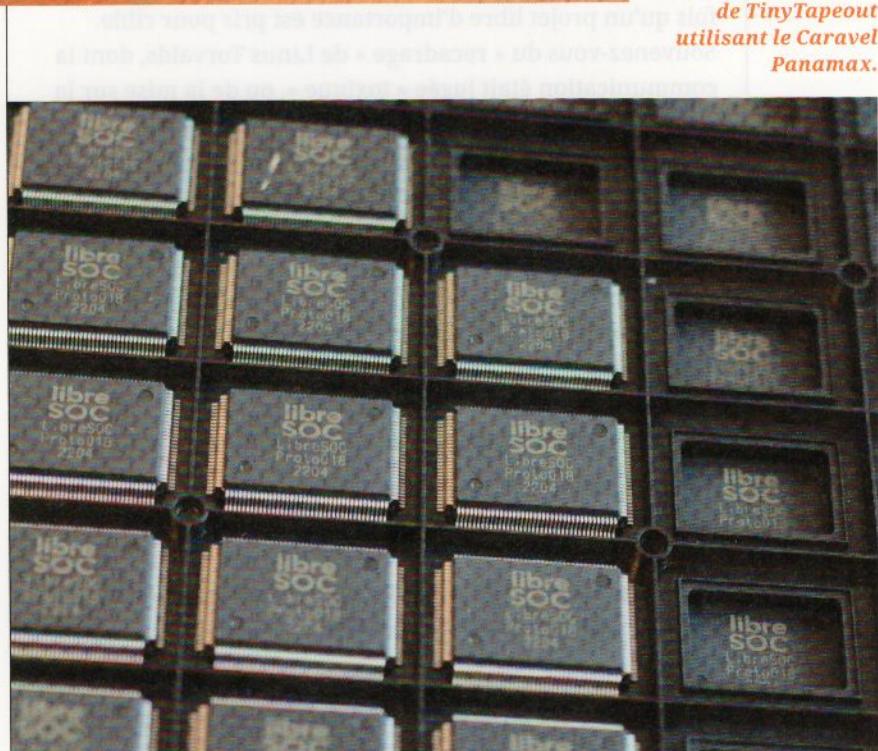

Figure 13 :

La centaine de prototypes du Libre-SOC est stockée sur trois niveaux de plateaux. Certains ont été partiellement testés, mais leur destin s'arrête là.

Figure 14 :

Le prototype du Libre-SOC contient un cœur POWER simplifié, encapsulé dans un boîtier TQFP128 tel que pourraient l'être de futures versions de TinyTapeout utilisant le Caravel Panamax.

pandémie. Depuis, la situation a encore empiré. Selon Luke Leighton (*lkcl*), le principal développeur :

« Libre-SOC est un projet incroyablement complexe avec deux cents pages de spécifications, développées durant six ans. L'objectif a toujours été de créer un processeur central, que l'on pourra intégrer dans des produits informatiques comme des smartphones, des ordinateurs portables et d'autres appareils grand public, procurant un grand rapport efficacité/consommation sans compromettre la performance ni la confiance des utilisateurs.

*Cela implique d'abord un énorme engagement dans la conception d'un jeu d'instructions (ISA), puis des spécifications, un simulateur, une réalisation matérielle et finalement une commercialisation, s'appuyant sur le droit des marques pour assurer l'interopérabilité. Cette commercialisation nécessite un budget à sept chiffres, ce qui est considérablement au-delà d'un projet de logiciel libre usuel.*

*Malheureusement, deux partenariats pour la commercialisation se sont soldés par des tentatives de prise de contrôle des recherches. La dernière a eu des effets dévastateurs sur le projet : intimidation de contributeurs, tentatives de récupération de l'infrastructure et des serveurs, et bien plus, ce qui a choqué toutes les personnes suivant le projet et indirectement mis en jeu la vie du développeur principal.*

*Avec autant de menaces pesant sur un projet libre, totalement public (y compris de la surveillance de l'activité sur le bugtracker et les listes publiques), il devient impossible de travailler en toute quiétude, sans peur d'intimidations ou de représailles. »*

Et là, normalement, vous allez vous exclamer « **Quoi ?** »

En regardant un peu en arrière, ce n'est pas la première fois qu'un projet libre d'importance est pris pour cible. Souvenez-vous du « recadrage » de Linus Torvalds, dont la communication était jugée « toxique », ou de la mise sur la touche de Richard Stallman, suite à des allégations calomnieuses. Brendan Eich (le papa de JavaScript) a été éclaboussé et évincé de Mozilla pour des histoires d'opinions politiques (comme s'il n'avait pas le droit à la vie privée hors du travail), et récemment Tim Peters (un pilier de Python) s'est fait suspendre par le comité de direction pour de prétendues violations du code de conduite [50]. Il y a encore d'autres exemples, que je vous épargne, mais cela se résume souvent à « il n'est pas assez ceci » ou « il est trop cela », en dehors de toute considération technique.

Dans tous ces cas, ces personnes gèrent des projets qui sont des briques essentielles, indispensables au paysage technologique d'aujourd'hui. Les prises de position par les acteurs industriels (IBM/Red Hat ou Microsoft) suffisent pour comprendre à qui profite le jeu des chaises musicales.

Le mode opératoire est souvent basé sur une prise de pouvoir progressive en exploitant les structures politiques en place, afin d'affaiblir les protections et accéder un jour plus

facilement aux ressources (les développeurs bénévoles et la communauté d'utilisateurs). Prenons un projet libre au hasard qui, fort de son succès, doit devenir « sérieux » donc créer une fondation par exemple, pour pérenniser les travaux et structurer le processus de développement. Alors que le projet était jusque-là relativement horizontal, le « dictateur bienveillant à vie » (BDFL) ou autre figure fondatrice est progressivement mis de côté par un ensemble de règles, de codes, de règlements et comités qui s'établissent grâce à des sponsors et autres personnes bienveillantes qui, sans contribuer une seule ligne de code, expliquent « comment on fait ». Une fois la machine mise en place, il ne reste plus qu'à tourner la manivelle et lâcher les chiens dans les forums de discussion.

Pour Libre-SOC, c'est un peu différent puisqu'il s'agit au final de concevoir du matériel. *Du peu que j'ai compris*, le fondateur avait cocréé une société privée (RED Semiconductor Ltd [51]) destinée à la commercialisation du projet, séparée soigneusement du développement public, qui reste libre et subventionné

par NLnet. Cette dernière est une fondation charitable, pas une entreprise, et ne fonctionne pas sur la base de contrats, mais de *mémorandums d'en-tente* (MoU), une forme de convention sans force exécutoire. C'est donc très flexible, mais au bon vouloir de chacun, donc sans aucune garantie. *Normalement, tout va très bien.*

Luke Leighton s'est retrouvé chassé de sa propre entreprise, privé ainsi de son investissement personnel, puis la société a tenté de recruter les développeurs de Libre-SOC, d'interférer avec une conférence tout en essayant de bénéficier des subventions. Le chaos n'était pas immédiatement palpable, mais les accusations qui ont fusé de part et d'autre n'ont pas plu à la fondation néerlandaise chargée de gérer et distribuer les aides. Acculé par les pressions, Luke a vu sa santé chuter catastrophiquement, ce qui l'a encore plus isolé. Je me demande par quel miracle il est encore en vie après les nombreux passages aux urgences médicales, conduisant à des maltraînances supplémentaires.

Au moment de boucler cet article, la situation du projet Libre-SOC est encore trop confuse pour déduire ou conclure à quoi que ce soit. On sait juste que NLnet a définitivement suspendu toute collaboration (après avoir payé le mauvais contributeur) et Luke est totalement démunie et en état de choc permanent. Le projet est mort.

En six ans, Libre-SOC a reçu 800000 euros [52] de financement, ce qui met des institutionnels très mal à l'aise puisqu'il n'a pas abouti. À cause des interférences et ententes privées, de la fuite des contributeurs, des réactions épidermiques et d'une obscure zizanie, tout le projet était en phase terminale depuis de nombreux mois. J'espère que certaines parties, comme les unités de calcul en virgule flottante de Jacob, seront réutilisées par d'autres projets. Mais il y a très peu de chances qu'une des puces des figures 13 et 14 soient un jour remises sous tension, même si leur documentation est en ligne. Qu'en ferait-on et où irait le projet sans son créateur ?

Nous pouvons en tirer (ou confirmer) certaines leçons :

- Passé un certain degré de popularité, il est quasiment impossible d'empêcher un projet technique de devenir politique. Aujourd'hui, *tout est politique* et les techniciens, surtout ceux qui excellent dans la conception, sont rarement dotés de sens social et de psychologie. D'ailleurs, Luke Leighton comme Richard Stallman sont notoirement autistes, donc des cibles privilégiées pour les attaques personnelles, car il est facile de les faire passer pour abuseurs.

- Tout projet prenant de l'ampleur financière attire les profiteurs. Le pouvoir attire le pouvoir. Il suffit de voir ce qu'est devenue la Linux Foundation [53] : on dirait un cartel de l'*openwashing* qui en plus sponsorise le développement du *kernel*\*.

- Les codes de conduite ne protégeront personne puisqu'ils sont conçus pour être interprétés à loisir dans le sens qui convient à qui les utilise. Les bonnes intentions et les documents savamment rédigés seront toujours faciles à détourner, les situations retournées. Luke pensait s'en prémunir en créant une charte [54], un code d'honneur très simple auquel chaque participant doit se conformer, qui se résume par :

\*<sup>4</sup> Tout comme un smartphone est un terminal intelligent qui est en mesure de passer des appels téléphoniques.

*« Always do good

Never do harm

The Code applies 100% of the time

Everyone knows the Code »*

NLnet a contré en sortant de sa manche un code de conduite de l'IEEE et les querelles restent cachées « pour protéger les personnes concernées ». Contrairement à du code informatique, la communication entre humains est naturellement ambiguë et les humains ont fait de la distorsion sémantique un sport depuis l'Antiquité : le sophisme.

Comment empêcher la mauvaise foi ? Faut-il éviter les projets qui ont un « code de conduite » ? Faut-il fuir les projets nécessitant des financements ? Comment empêcher un projet de devenir aussi toxique que les réseaux sociaux ?

Je n'en sais rien, mais Libre-SOC a essayé sans réussir, et j'ai ressenti une gêne et une tristesse voilées durant la conférence. Souhaitons à Luke de se rétablir.

## CONCLUSION

Je ne peux malheureusement pas parler des années précédentes (pour cela, voir les pages correspondantes sur leur wiki [1]), mais j'ai pu enfin assister à l'édition 2024 : c'était résolument un grand cru ! Il y avait tellement d'autres choses à mentionner et expliquer ici, mais je n'ai ni le temps ni la place, malgré les aléas du calendrier de publication.

Durant ces trois jours, j'ai fait de nombreuses rencontres et même des retrouvailles très surprenantes. Et j'ai constaté avec joie que le monde des circuits intégrés a commencé sa période de *tsunami*, un peu comme en l'an 2000 où Linux commençait à être pris au sérieux par l'industrie. Tout le travail de fond avait déjà été réalisé par le projet GNU depuis sa fondation et il aura fallu une décennie avant que le projet « amateur » d'un jeune Finlandais devienne la clé de voûte de sociétés milliardaires.

Comparé à l'industrie des logiciels, le monde des circuits intégrés est d'une nature très différente, mais les parallèles sont toujours là, avec un décalage d'un quart de siècle.

C'est émouvant de se dire que dès 1999, des groupes de geeks (F-CPU, OpenRISC et d'autres) ont osé y croire. Ils ont partagé une vision commune (ou du moins, semblable) et ont œuvré sans relâche à construire toutes les briques qui manquaient. On peut mentionner beaucoup de jalons (OR1K, LEON, GHDL, RISC-V, OpenROAD, Tiny Tapeout et j'en passe), mais aujourd'hui, nous pouvons contempler tout le travail accompli, célébrer les résultats tangibles et nous réjouir du changement d'attitude des industriels et des politiques.

Nous avons pu discuter des défis qui pointent à l'horizon, ainsi que des orientations futures : par exemple, la coopération entre le monde propriétaire et l'*open source* va encore s'accélérer. Comme le disait si bien Andrew Kahng, « *open source is not a goal but a way* ». Le fait que GNU/Linux ait pu « trouver sa place » sans tout remettre en question rassure aujourd'hui de nombreuses entreprises et leur donne un mode opératoire pour profiter sans risque de la nouvelle vague. Le *FUD* ne disparaît pas, mais il aura moins d'emprise.

Il a été aussi mentionné plusieurs fois que les outils freinent l'adoption par

les débutants. Les logiciels EDA classiques sont lourds, complexes, abscons, souvent incompatibles, ce qui rappelle à beaucoup ce qu'il s'est passé avec les logiciels pour programmer les microcontrôleurs (avant la vague Arduino), dessiner les circuits imprimés (avant KiCAD) ou configurer les FPGA (*soupir*). Aujourd'hui, <https://wokwi.com> reprend ces nouveaux *workflows* libres pour faciliter l'accès du silicium aux néophytes, en réutilisant des outils et concepts familiers, mais la multiplicité des distributions GNU/Linux freine clairement beaucoup d'initiatives. On a évidemment parlé du cauchemar des dépendances entre paquets [55], de l'enfer des versions d'OS, de scripts spécifiques aux distributions... Et installer les outils n'est pas tout : il faut les prendre en main et savoir s'en servir de bout en bout !

Ces difficultés ne sont pas encore bloquantes. La démocratisation de la conception de circuits intégrés avance plus vite, plus fort, et l'argent commence à couler : les vannes des

financements sont ouvertes ! Cela attire forcément les nouveaux acteurs, les *startups* commencent à pointer leur nez, ou à « pivoter » vers celle-ci (la vague de l'IA finira par retomber, mais il faut toujours des puces pour la faire tourner).

Même si le marché est relativement réduit (et il a surtout été question d'eFabless), il s'agrandit : grâce à la réduction des coûts de fabrication, de plus en plus de personnes et hobbyistes vont sauter du FPGA à l'ASIC

## RÉFÉRENCES

- [1] FSiC 2024 : <https://wiki.f-si.org/index.php/FSiC2024>

« *The Free Silicon Foundation (F-Si) is a nonprofit organization with the scope of promoting:*

1) *Free and Open Source (FOS) CAD tools for designing integrated circuits,*

2) *the sharing of hardware designs and libraries,*

3) *common standards,*

4) *the freedom of users in the context of silicon integrated circuits.* »

- [2] Go IT! : <https://wiki.goit-project.eu/>

*The Go IT! is an EU Coordination and Support Action (CSA) about Open Source Hardware for ultra-low-power, secure processors funded under cluster 4 (Digital, Industry and Space), of Horizon Europe. The project was submitted on October 21 2021, was awarded on March 18 2022 and started on September 1 2022. Its planned duration is three years.*

- [3] Guidon, Yann : « *Une brève histoire des ASIC libres* » Hackable n°36, janvier 2021, pp. 42-66 <https://connect.ed-diamond.com/Hackable/hk-036/une-breve-histoire-des-asic-libres> (Creative Commons).

- [4] [https://en.wikipedia.org/wiki/Process\\_design\\_kit](https://en.wikipedia.org/wiki/Process_design_kit)

- [5] <https://open-source-silicon.dev/> liste et documente les trois PDK disponibles actuellement : SkyWater Sky130, GlobalFoundries GF180MCU et l'IHP SG13G2 Open Source PDK, présenté à FSiC2024.

## conférence/ EDA

- FSiC2024 : L'Open Silicium décolle à Paris ! -

pour réaliser leurs projets, comme Thorsten ! C'est un rêve que d'innombrables électroniciens ont gardé enfoui longtemps dans leur tête, et il se réalise enfin. Les choses sérieuses commencent donc vraiment : maintenant que tout le monde se réveille, il faut se retrousser les manches.

Une autre chose se profile au loin : l'EDA *open source* commence à rattraper les outils commerciaux sur certains points. Grâce à sa flexibilité, les coûts d'exploration

de l'espace des paramètres ont chuté radicalement : j'en parlais dans le cadre de GHDL (qui peut être lancé autant de fois que l'on souhaite), mais d'autres outils bénéficient d'une accélération par GPU ou IA (et pas juste pour la documentation). Ce n'est qu'une question de décennies avant que les outils propriétaires soient relégués à une niche particulière.

J'adresse mes chaleureux remerciements à chacun des participants et organisateurs, trop nombreux à lister individuellement ! J'aurai plaisir à vous retrouver, mais l'édition 2025 se déroulera probablement en Allemagne, ce qui est un peu loin pour moi (même si j'ai déjà participé à ce genre de rencontres outre-Rhin [56]). Je ne sais pas ce qui a motivé l'annonce des organisateurs après la dernière présentation, concernant le déplacement de l'événement, mais gardez un œil sur le site de F-SI pour obtenir les dernières informations à propos de la prochaine conférence ! **YG**

[6] Tiny Tapeout : <https://tinytapeout.com/>

Voir entre autres la vidéo de Robert Feranec « *How To Design and Manufacture Your Own Chip* » (14 juin 2024) à

<https://www.youtube.com/watch?v=caXwuuXSB-A>

[7] <https://efabless.com/chipignite> : 10 mm<sup>2</sup> pour 10000 dollars.

[8] Yann Guidon : « *Développer en VHDL sous Linux* » GLMF n°36, 2001,

<http://f-cpu.seul.org/new/lm02.tgz>

(état de l'art de la programmation avec Vanilla VHDL et Simili, GHDL n'existe pas encore).

[9] Moss, Sebastian : « *Ousted Arm China CEO refuses to go after being fired, again - It's not clear if SoftBank knows how to get rid of him* » 5 mai 2022,